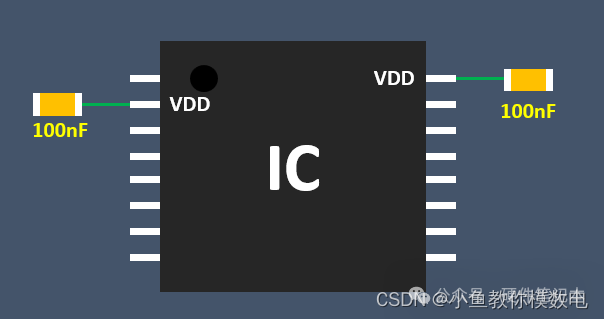

在设计电路的时候,常常会在芯片的每个电源引脚就近的放一个100nF的贴片电容,这电容有什么作用呢?今天就来和大家分享一下这个电容的作用以及为什么是100nF。

首先这个芯片电源引脚的100nF的电容一般我们称为旁路电容,也有叫去耦电容的,因为这颗电容的作用比较多,个人觉得叫旁路和去耦电容都没问题,我这里暂且称为旁路电容。这个电容的作用有几个方面:

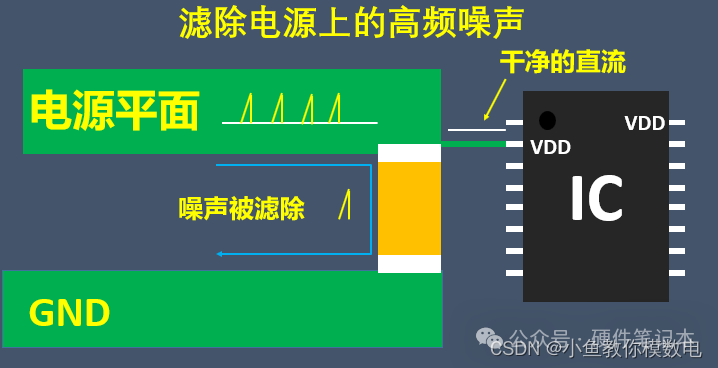

第一:滤除电源上的高频噪声。

电路中给芯片供电的电源平面一般都有很多高频的噪声,为了使芯片的输入电源干净,所以一般在芯片电源引脚加一个电容滤除电源中的高频噪声。

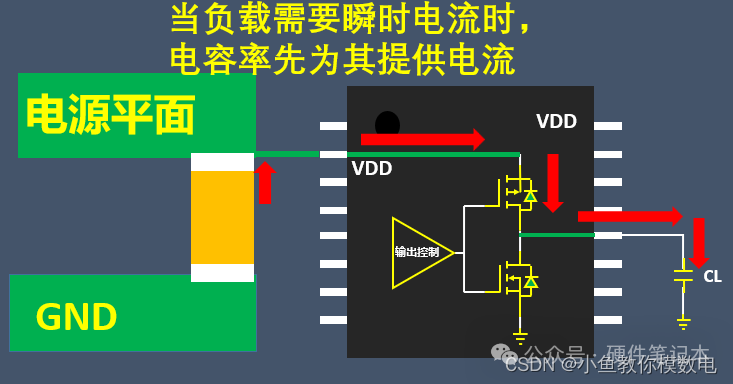

第二:储能,当负载需要瞬时电流时,电容率先为其提供电流,减小电源产生的波动

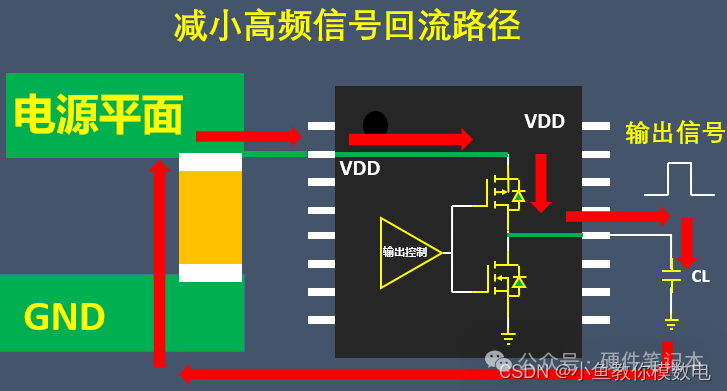

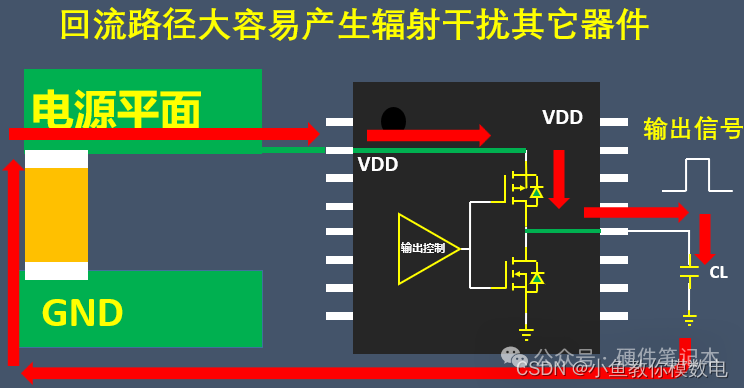

第三:给高频信号提供最近的低阻抗回流路径,减少对其它芯片电源的干扰

电流永远是闭合的,从哪里来,就要回到哪里去,不管是电流或者位移电流的形式,高频信号回流选择感抗最低的路径

接下来我们来探讨下为什么这个电容常常是100nF。

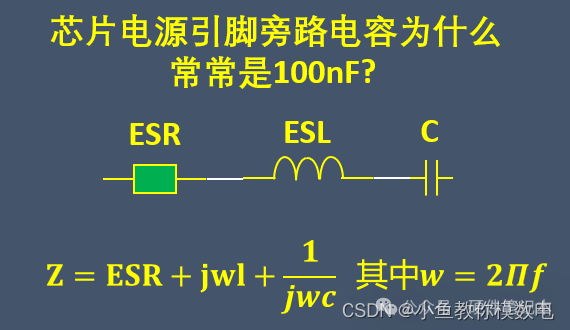

大家可以看下电容的等效模型,他其实是可看成一个电感,电容然后还有电阻的串联,ESL称为等效电感,ESR称为等效电阻,C为电容的理想容值。

等效的阻抗Z=ESR jwl 1jwc 其中w=2Πf

那么就有那么一个频率f=f0,使得Z=ESR,这时电容就相当于一个纯电阻,整个电容这时阻抗最小,这个频率f0我们称为电容的谐振频率,当信号频率小于f0时电容呈现容性,电容等效于一个电阻和电容的串联,当信号频率大于f0时电容呈现感性,表现为。电容当作高频滤波或回路时,应该工作在容性的条件下,因为电感对高频信号具有阻碍作用。也就是信号的频率应当小于电容的谐振频率。

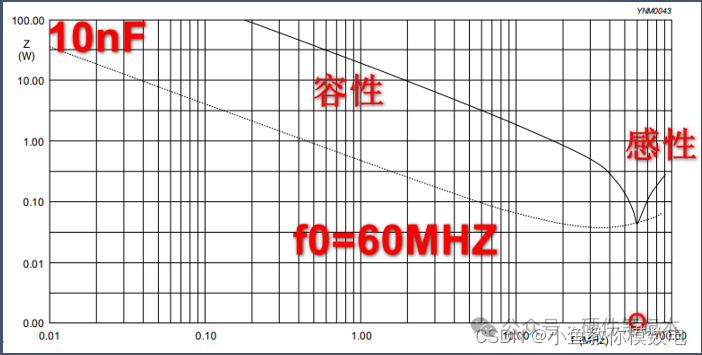

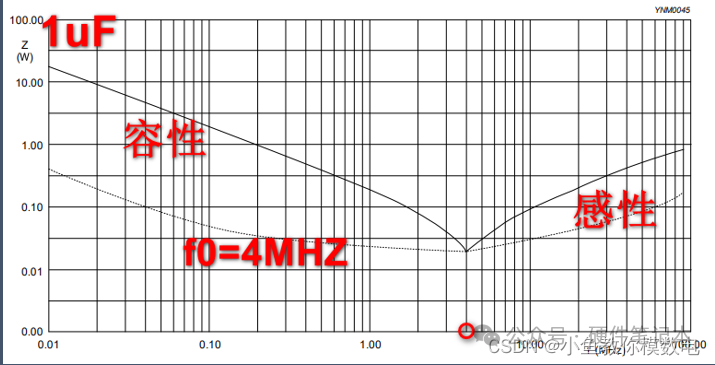

下面我们来看下某厂商贴片陶瓷电容ESR随频率的变化曲线

这个是10nF的,最低点就是谐振频率点的ESR,小于谐振频率电容呈容性,大于谐振频率电容呈感性。从图中可以看到这个10nF电容的谐振频率大概是60MHZ;

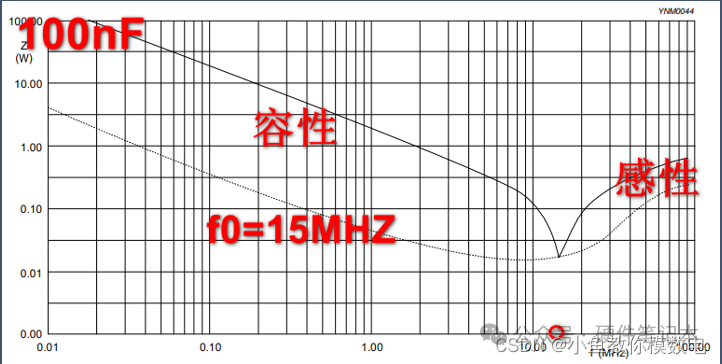

这个是100nF的,谐振频率大概是15MHZ

这个是1uF的

因为我们常用的数字芯片其信号频率基本都在10MHZ以下,所以电源上的干扰或者其自身产生的干扰信号也大概在这个范围,所以我们的常用的经验值一般用100nF的电容,如果器件信号频率比较高我们可以选择容值小点的电容。

电容容值与频率我们可以参考下面的

频率范围 | 推荐容值 |

DC-100K | 10uF以上电容 |

100K-10M | 100nF电容 |

10M-100M | 10nF电容 |

>100M | 1nF电容 |

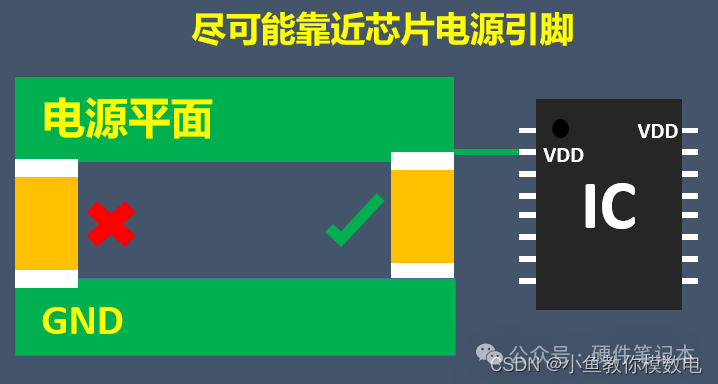

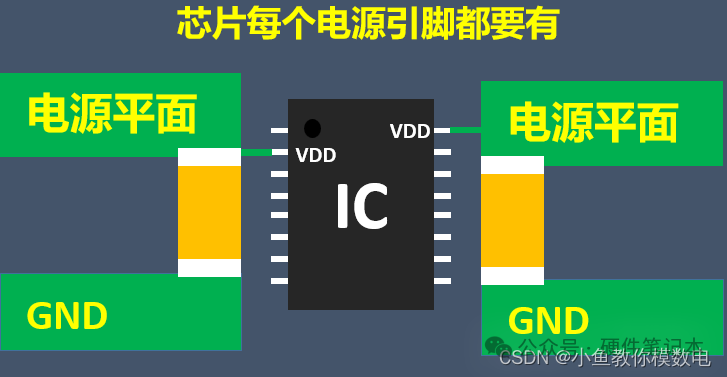

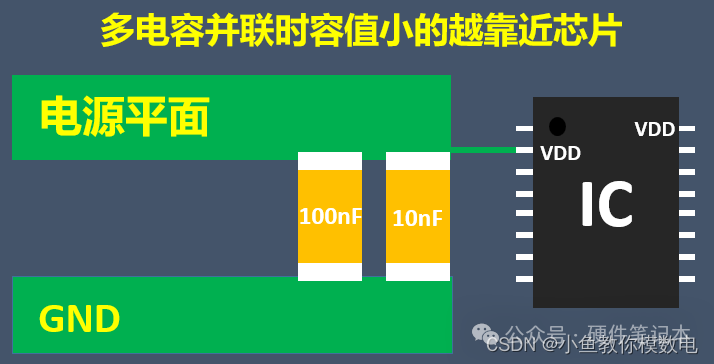

电容放置的要求

尽可能靠近芯片电源引脚;

尽量每个电源芯片引脚都有

根据芯片的信号频率修改电容的容值,多电容并联时,容值小的越靠近芯片

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/weixin_42693097/article/details/127719675

暂无评论