答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

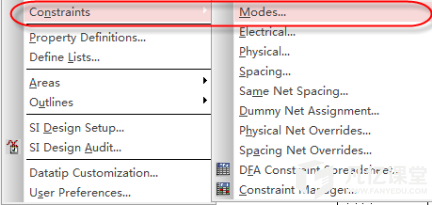

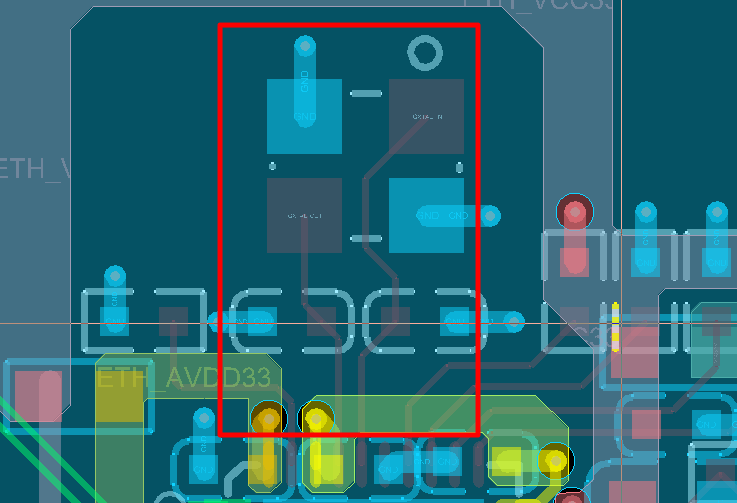

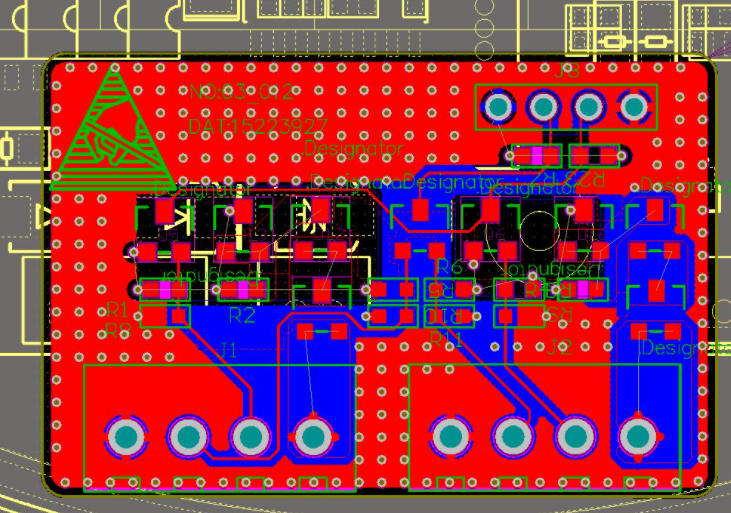

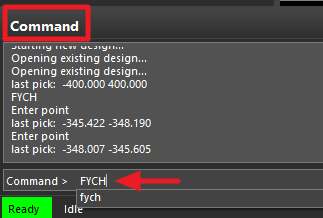

第一步,需要将约束封装引脚长度信息的约束开关打开,执行菜单命令Setup-Constraints,在下拉菜单中选择Modes,如图6-96所示;

图6-96 约束开关设置示意图

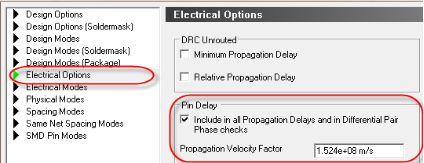

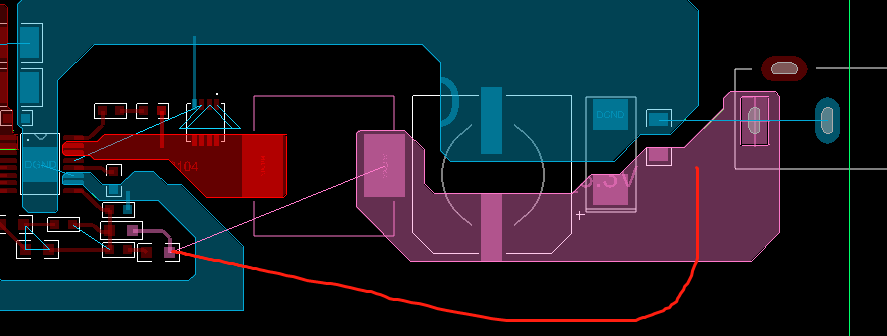

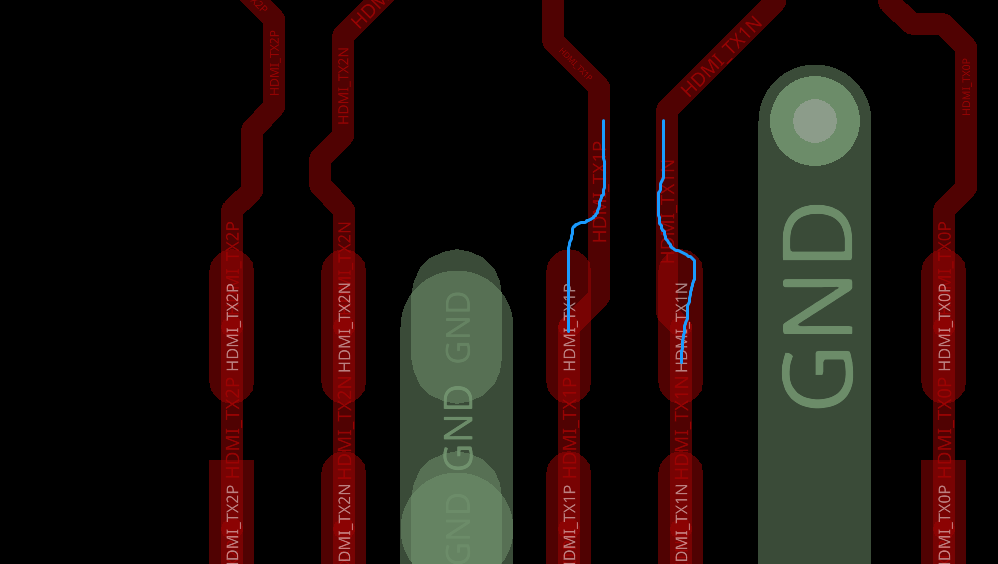

第二步,进入约束开关管理器界面之后,在左侧边栏选择Electrical Options选项,在右侧勾选上Pin Delay的选项,如图6-97所示,这样在等长约束规则中Pin Delay数据行才会被激活,才会应用到等长列表当中;

图6-97打开Pin Delay示意图

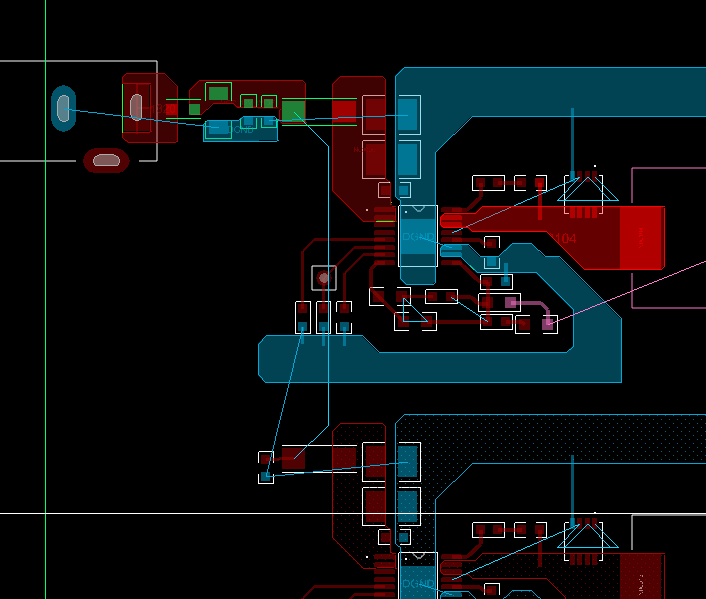

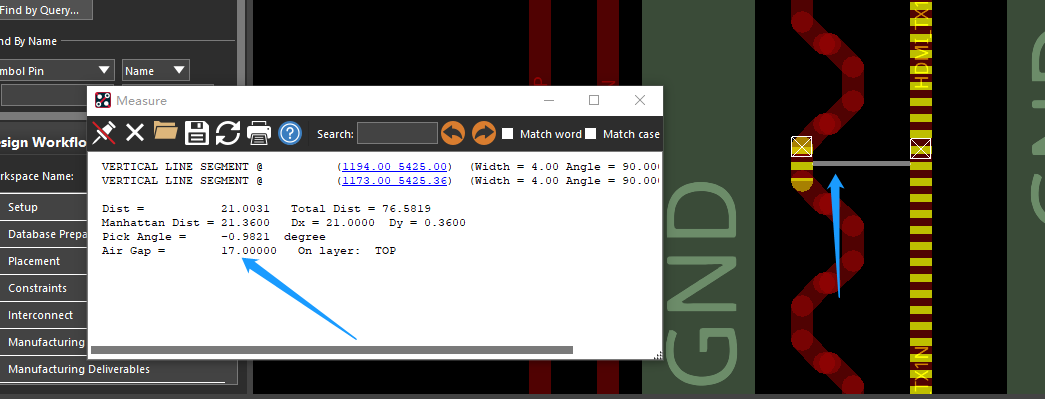

第三步,设置完上述的参数之后,回到规则管理器面板中,在加好的等长规则中,会发现Pin Delay才是可以编辑的状态,在Pin Delay界面,如图6-98所示,有Pin1和Pin2两个输入栏,代表的是该信号连接的两个IC,如果两个IC都有引脚长度的话,分别输入即可,这个数据是可以手动进行输入的,但是这样的工作量比较大,也非常容易出错,我们可以通过导入Excel表格的方式进行导入;

图6-98 Pin Delay输入栏示意图

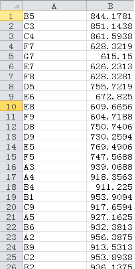

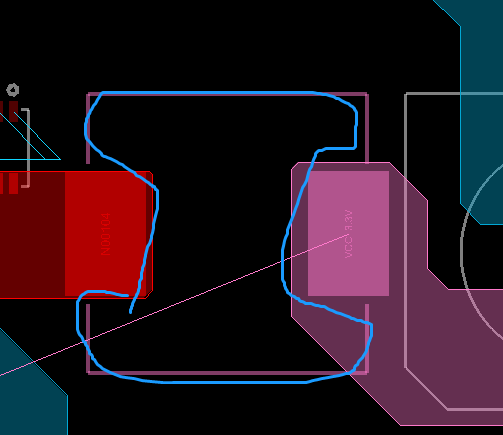

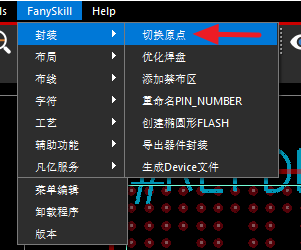

第四步,根据芯片厂家提供的参数,将Pin Delay的数据输入到Excel表格中,格式如图6-99所示,一行是芯片的管脚列表,一行是芯片引脚长度信息,然后保存,存为后缀为CSV的文件,Allegro软件才能识别;

图6-99 Pin Delay格式示意图 图6-100导入 Pin Delay示意图

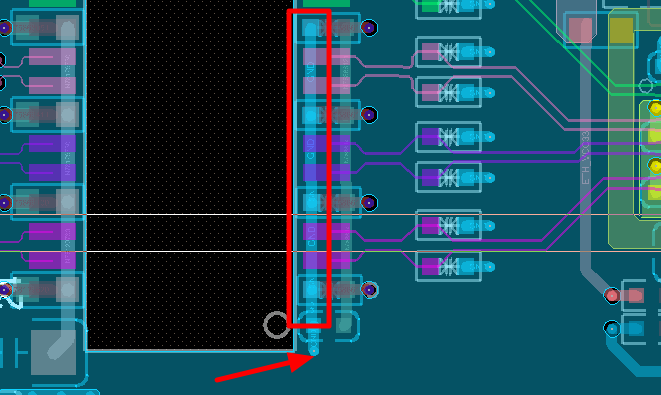

第五步,设置好Pin Delay的格式以后呢,点击执行菜单命令File-Import,导入选项中选择Pin Delay,如图6-100所示;

第六步,进入导入界面,选择刚刚处理好的csv文件,然后用鼠标去选择需要导入芯片封装引脚长度的元器件,进行导入即可;

第七步,导入成功后,在Pin Delay栏就可以相对应的数据,分别对应的是哪个芯片,这样可以大大提高效率,并且不会出错。

暂无评论