本期将为大家揭秘紫光盘古系列高性能入门级1K2K开发板。1K2K开发板以紫光Compact系列PGC1KG-LPG100/PGC2KG-LPG100器件为核心,满足低功耗、低成本、小尺寸需求。

小编将为大家陆续推出1K2K实验教程,本期介绍控制LED灯。控制LED灯1.1 实验目的: 实现对多LED灯的控制;1.2 实验要求: 控制8个LED以1s的周期闪烁(0.5s亮,0.5s灭)

1.3 实验原理

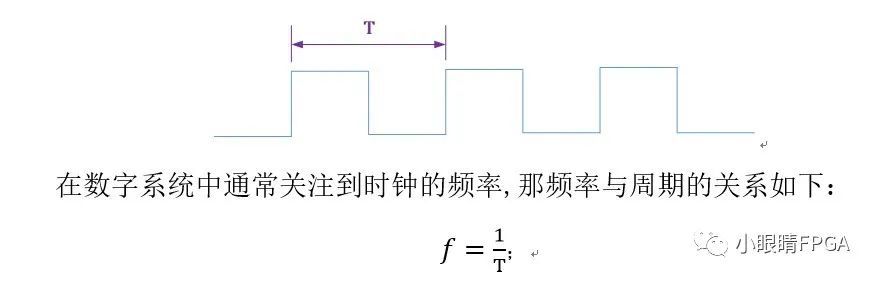

通常的时,分,秒的计时进位大家应该不陌生;1小时=60分钟=3600秒,当时针转动1小时,秒针跳动3600次;那在数字电路中的时钟信号也是有固定的节奏的,这种节奏的开始到结束的时间,我们通常称之为周期(T)。

在数字系统中通常关注到时钟的频率,那频率与周期的关系如下:

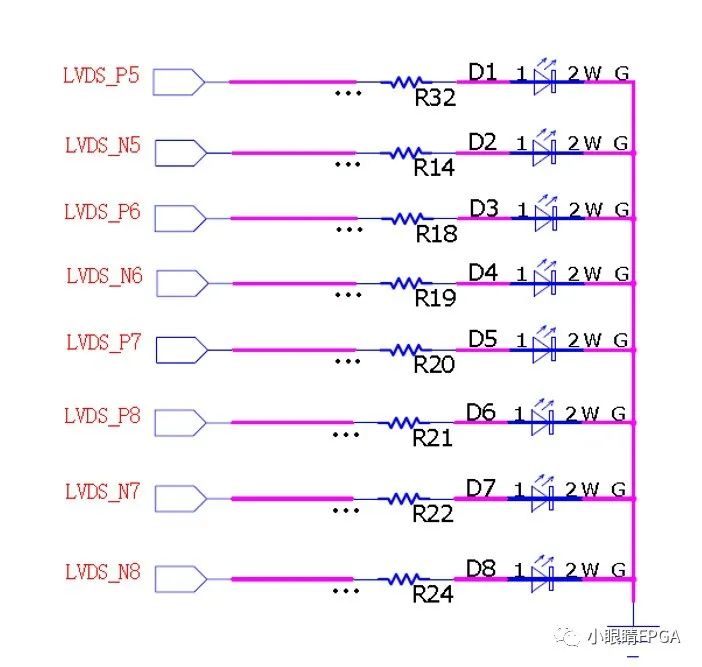

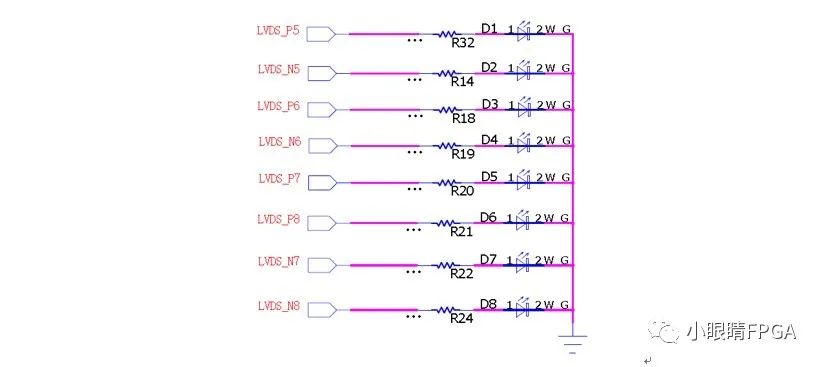

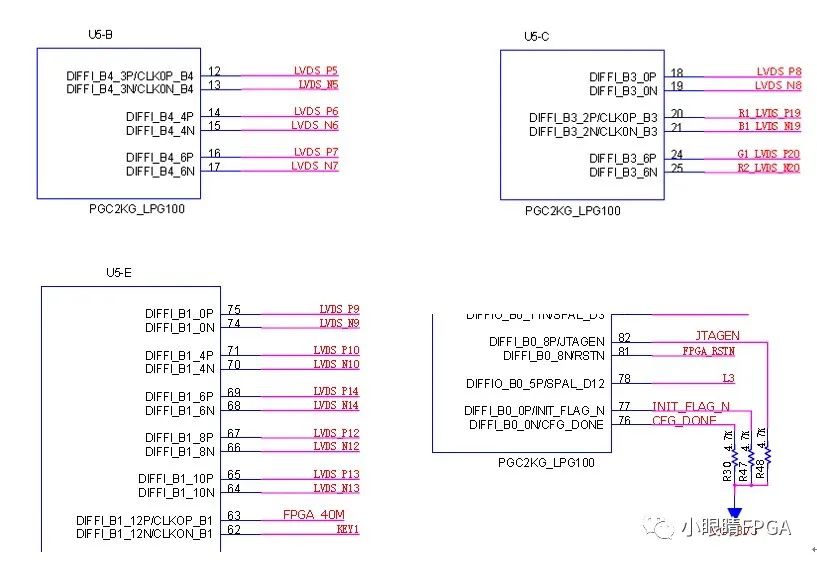

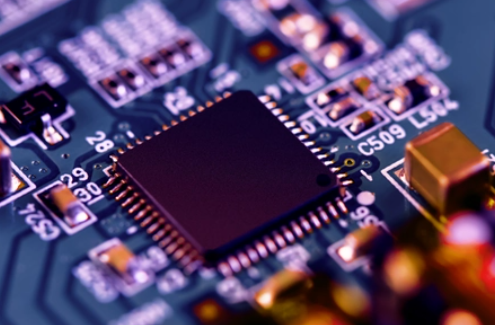

MES2KG板卡上有一个40MHz的晶振提供时钟给到PGC2KG;实验分析: 控制LED亮灭需要控制IO输出的高低电平即可(高电平点亮,低电平熄灭),原理图如下:

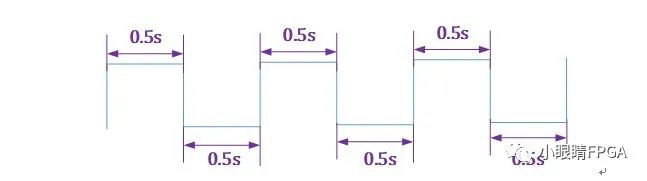

控制LED周期性的维持0.5s亮,0.5s灭,需要控制IO输出0.5s高电平,0.5s低电平周期变化,如下图波形:

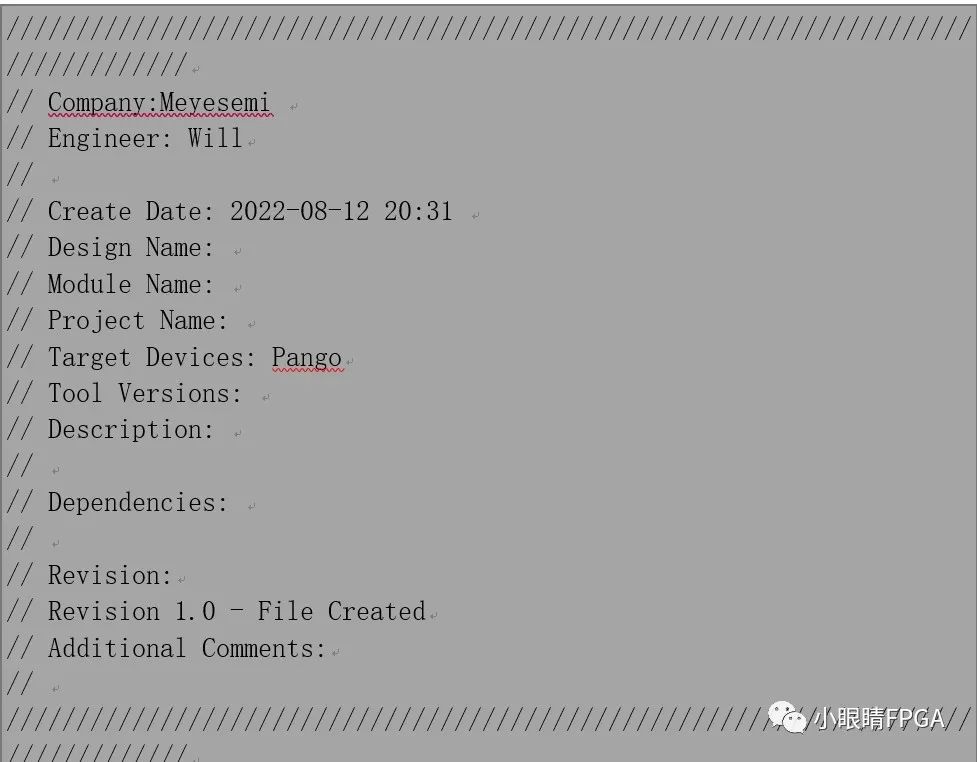

外部输入时钟为40MHz时钟周期为25ns(在verilog设计中的计数器的计时原理基本上是一致的,确认输入时钟周期,目标计时时间后可得到计数器的计数值到达多少后可得到计时宽度); 0.5s = 20000000*25ns = 20000000 ×; IO输出状态只有两种:1或0;我们可以使用一个计数器,计数满20000000个时钟周期时将IO状态进行翻转,即可完成每0.5S输出状态跳转,即LED灯会以0.5S的间隔亮灭变化;1.4 实验源码设计(完整源码查看demo源文件)1.4.1 文件头设计 在module之前添加文件头,文件头中包含信息有:公司,作者,时间,设计名,工程名,模块名,目标器件,EDA工具(版本),模块描述,版本描述(修改描述)等信息;以及仿真时间单位定义;

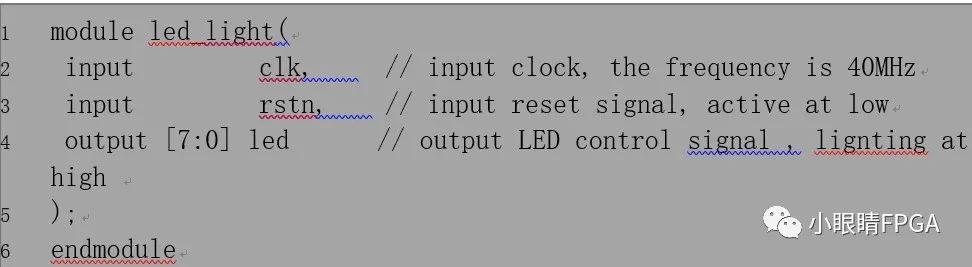

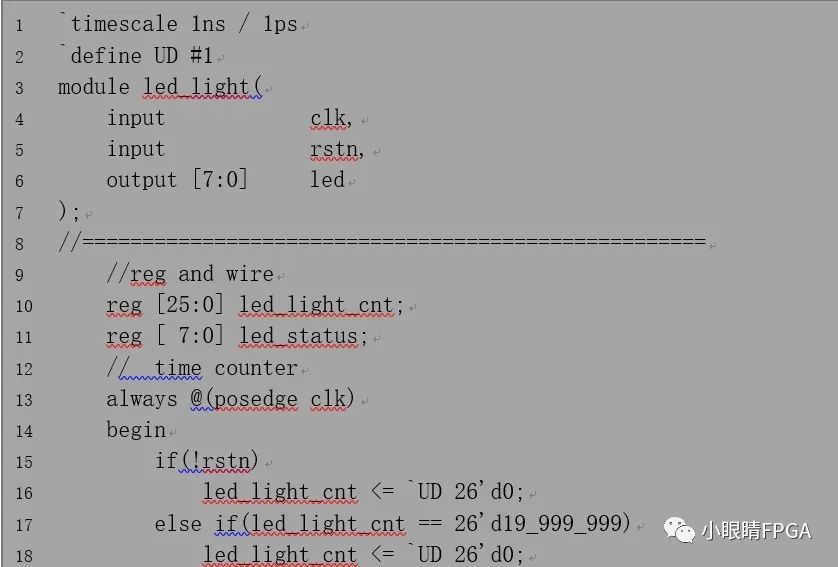

`timescale 1ns / 1ps 表示仿真精度是1ns,显示精度是1ps;`define UD #1 定义UD表示#1;#1仅仿真有效,表示延时一个仿真精度,结合上一条语句表示延时1ns;1.4.2 设计module1.4.2.1 创建module,确定输入输出信号

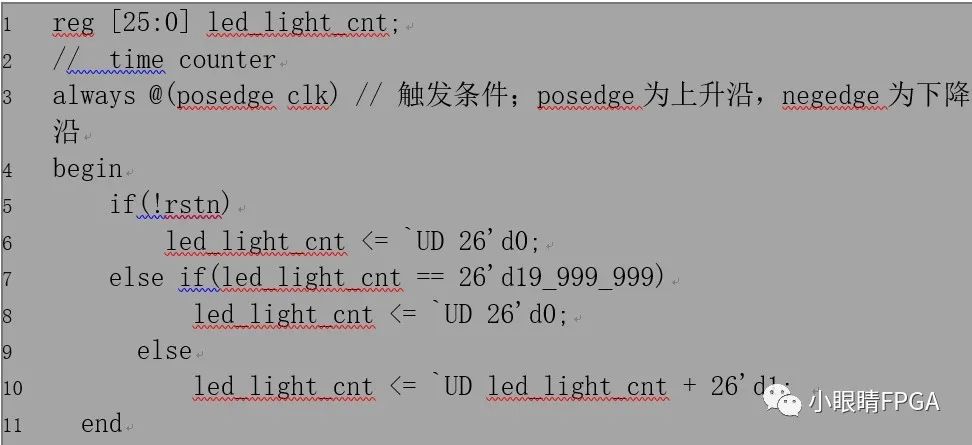

此段代码是标准的module创建的模型,module创建时需要确认输入输出信号并定义好位宽,之后在对module进行具体的逻辑设计;管脚与管脚之间间隔用“,”,最后一个管脚不用间隔符号; 创建module时需要定义输入输出信号;本实验输入时钟和复位即可,输出是控制LED的亮灭,MES2KG板卡上共有8个LED,故而输出8bit位宽的信号;1.4.2.2 设计一个计数器; 单个状态计数20000000,1个亮灭周期的计数即为40000000 = 26’h2625A00;所以计数器的位宽为26位即可,此处请结合数字电路中的同步计数器的工作原理分析;

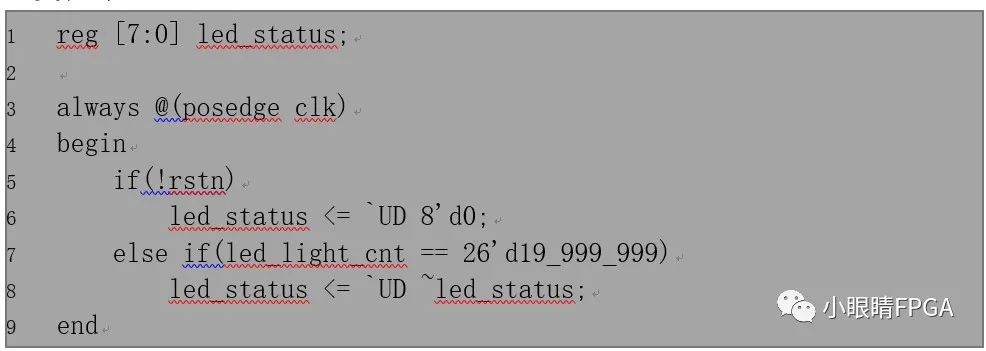

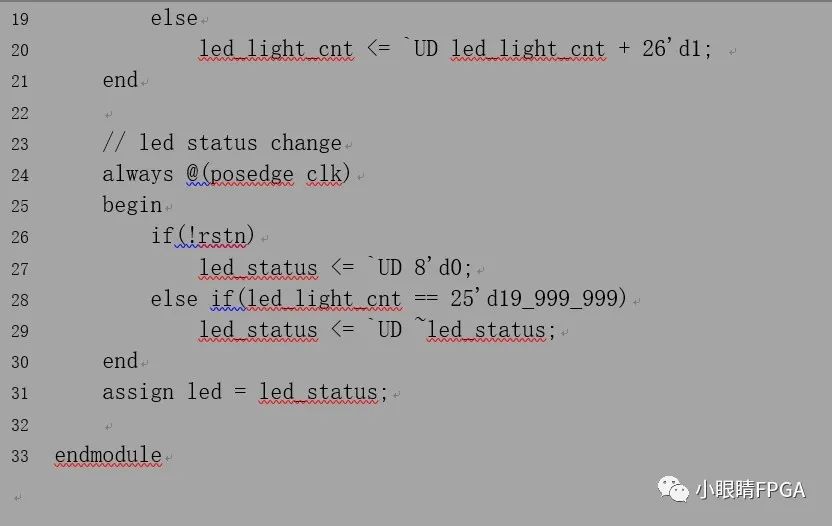

当计数器计数到26’d19999999时,计数周期包含了从0~26’d19999999的时钟周期,故而总时长时26‘d20000000 × ;硬件输入时钟为40MHz,所以此计数器的技术周期是0.5s;1.4.2.3 led显示状态控制 在指定的时间刻度上对LED的状态进行变更,以达到控制LED规律的亮灭的目的; led_light_cnt的计时周期为0.5s,故在led_light_cnt上取一个点来变更LED的显示状态即可完成每隔0.5s LED显示发生变化;由于LED亮和灭只有两个状态,在赋值处理上将寄存器取反即可得到对应的从亮到灭变化(或从灭到亮的变化);

1.4.3 完整的Module(不含注释)

1.4.4 硬件管脚分配 MES2KG的LED和CLK与FPGA的IO连接部分的原理图如下(在工程中做物理约束时需要结合原理图的FPGA管脚分配进行约束):

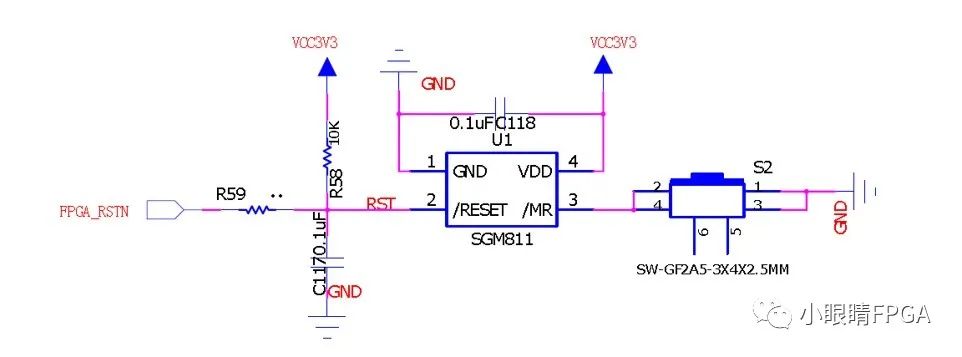

复位设计是低电平有效,而MES2KG板卡上的按键按下时为低电平,松开为高电平,可用按键输入来做复位信号;使用RSET做为复位按键即可;

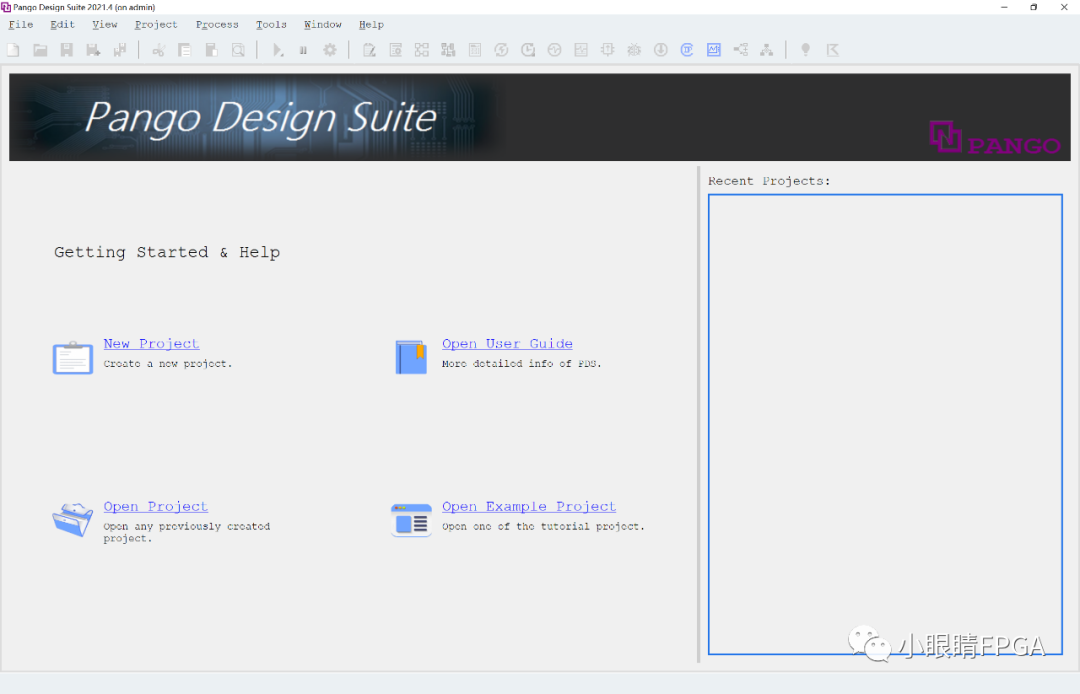

1.5 实验步骤1.5.1 打开PDS软件,创建工程Step1:打开PDS软件,单击New Project

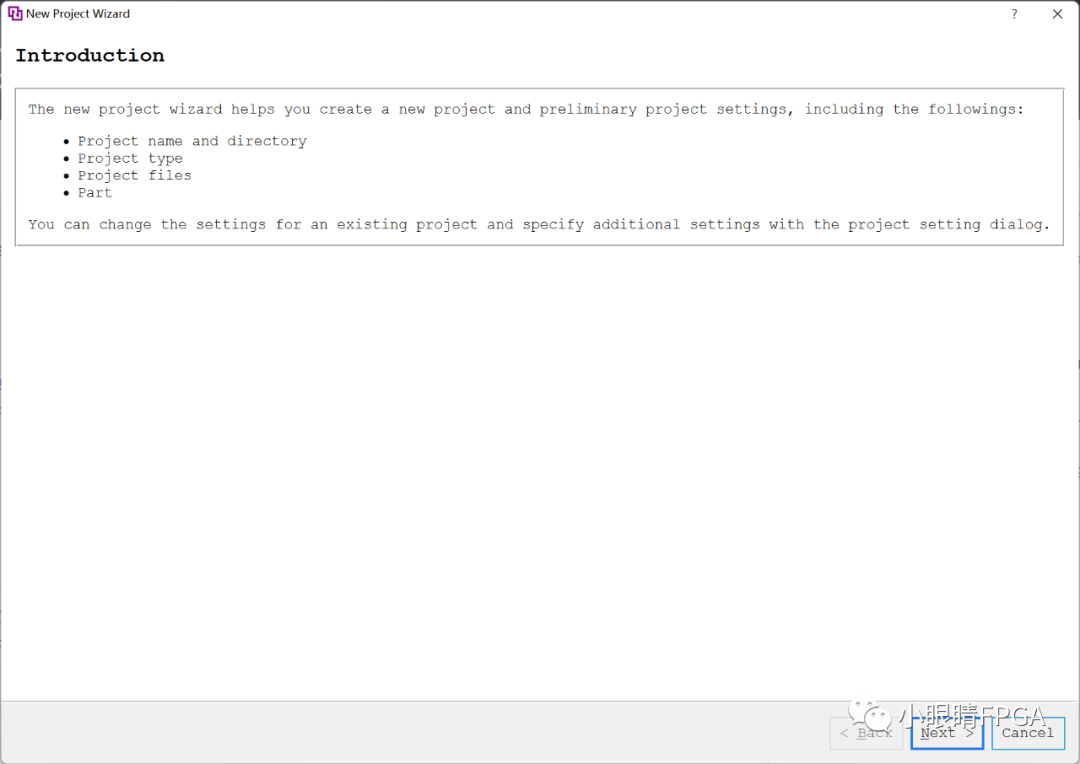

Step2:单击NEXT

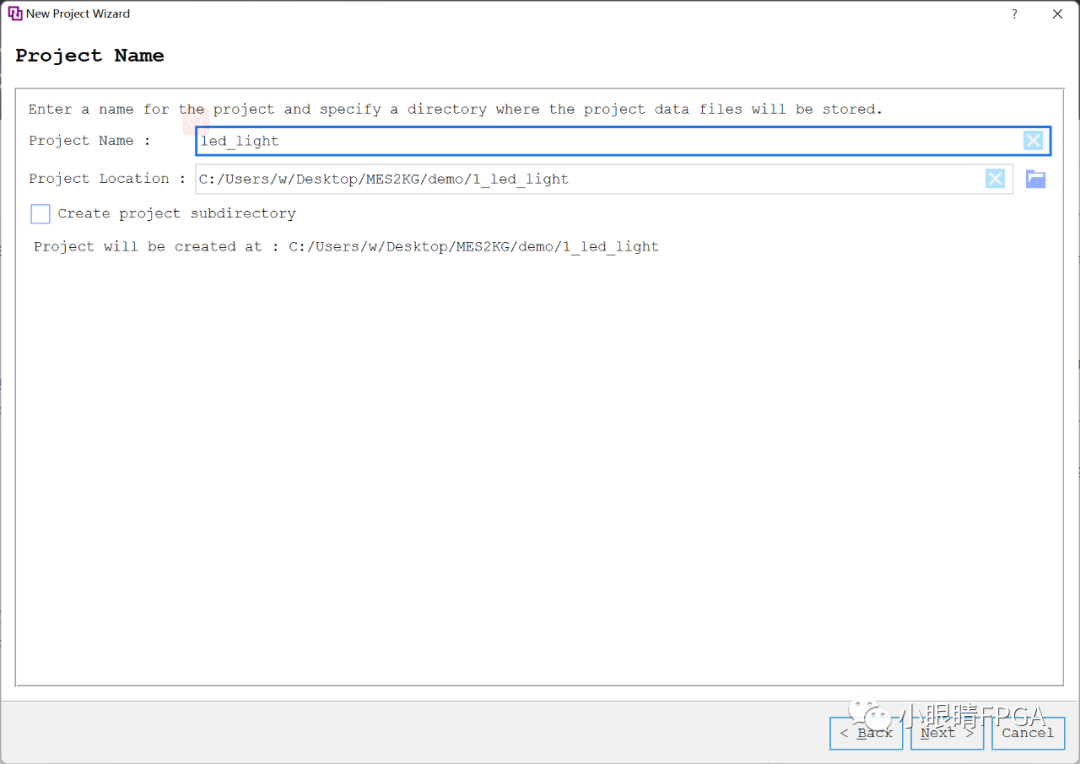

Step3:创建名为led_light的工程到对应的文件目录,之后单击Next

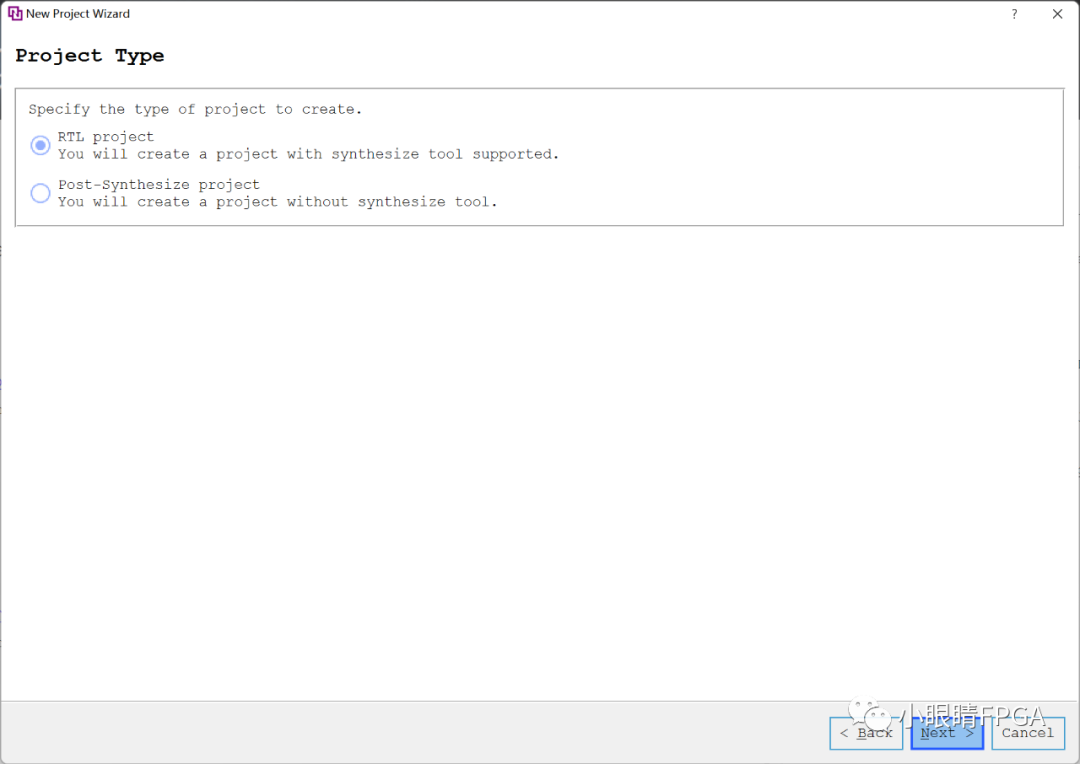

Step4:选择RTL project,单击Next

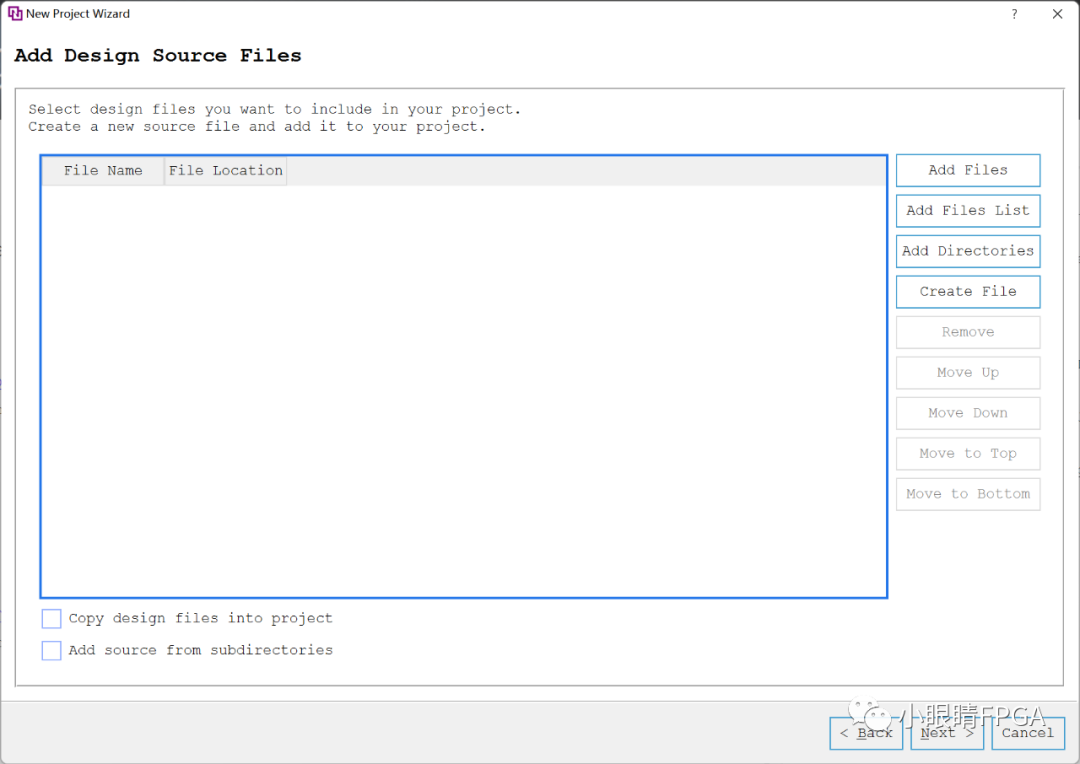

Step5:单击Next(也可添加.v文件)

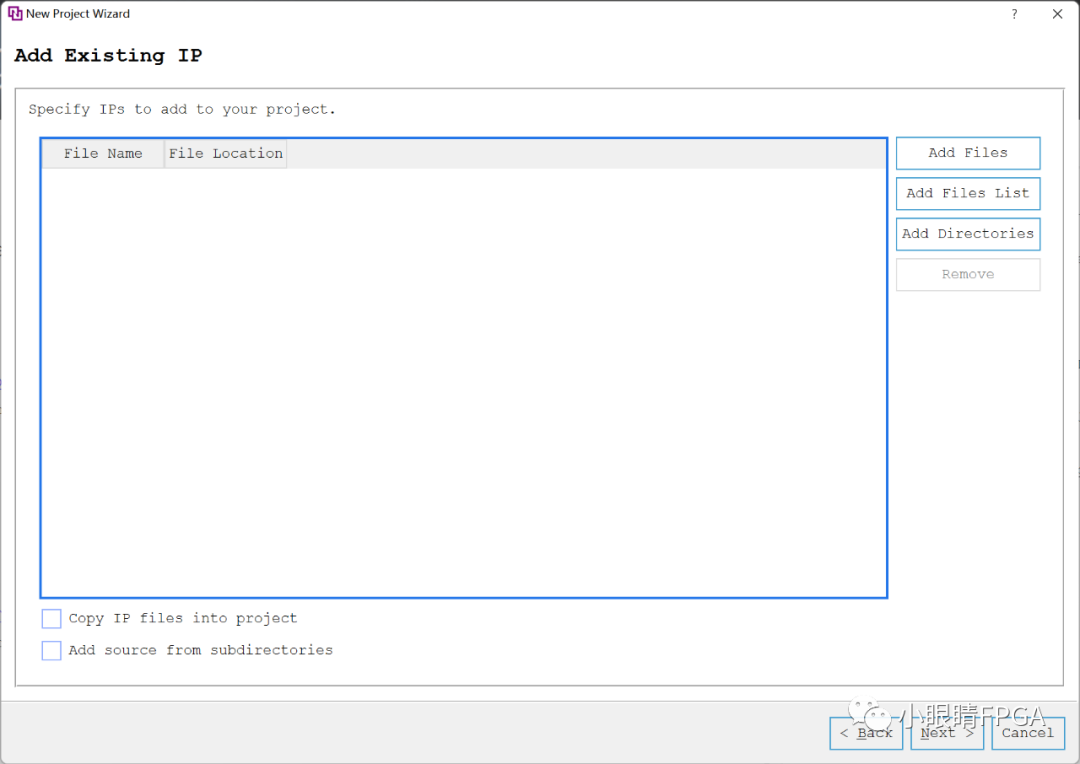

Step6:单击Next

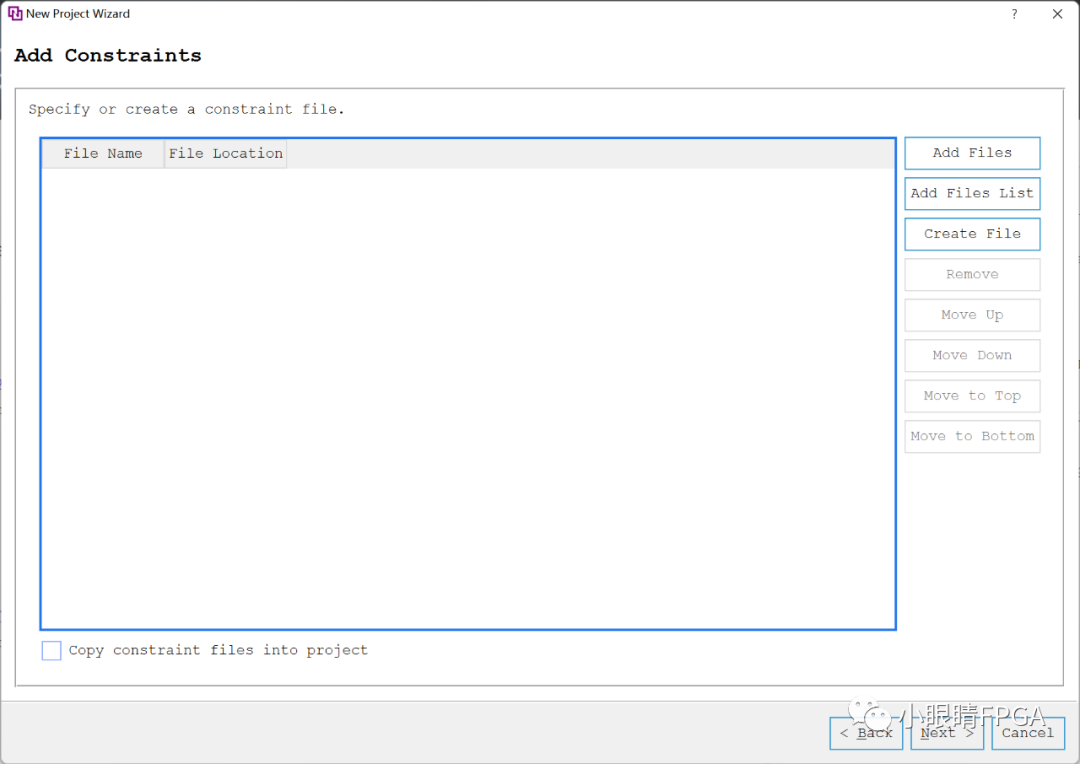

Step7:单击Next

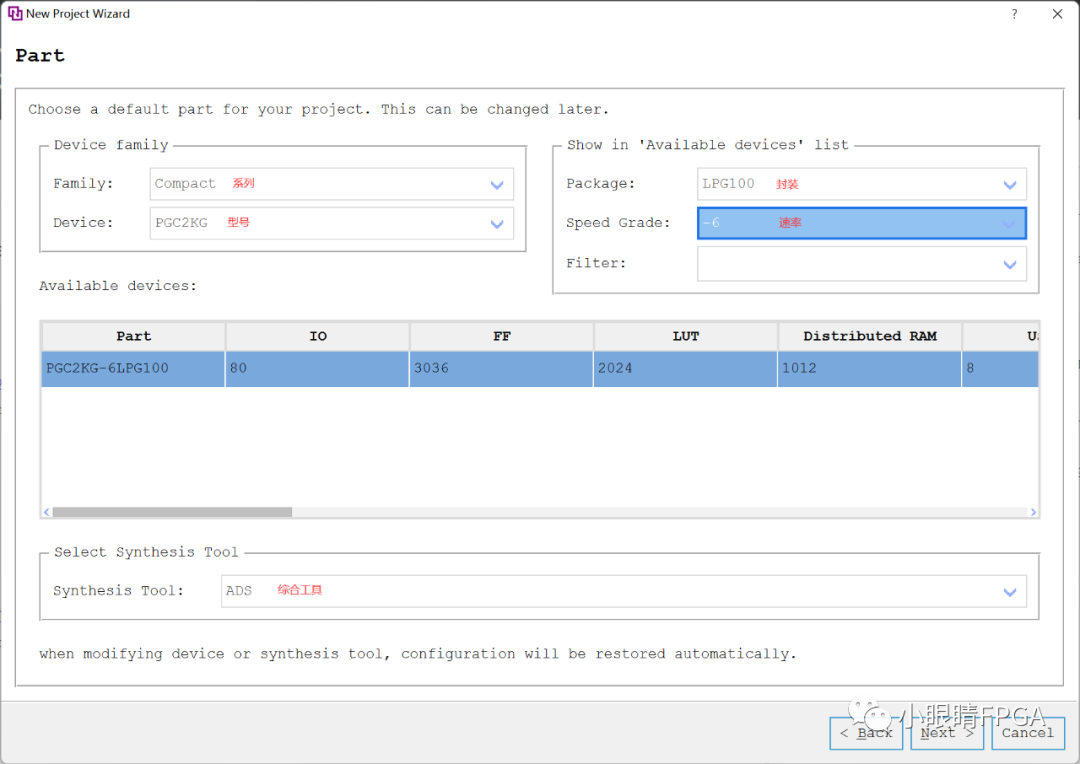

Step8:选择器件系列、型号、封装、速率、综合工具,之后单击Next

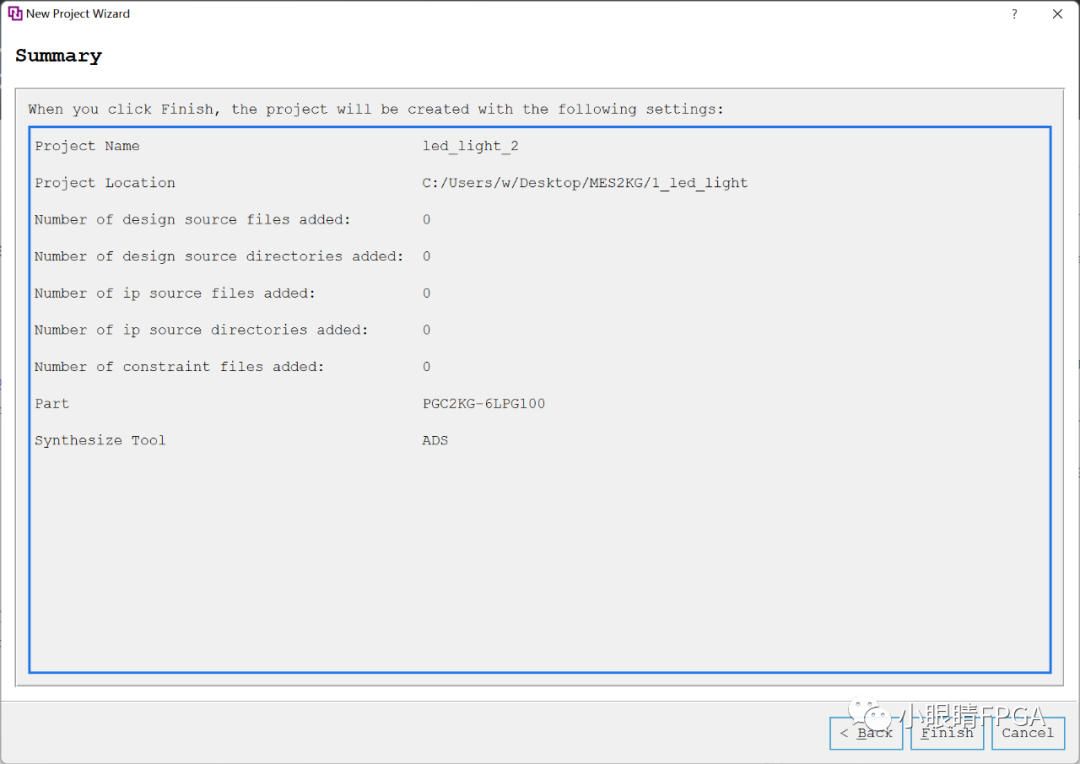

Step9:单击Finish,完成工程创建

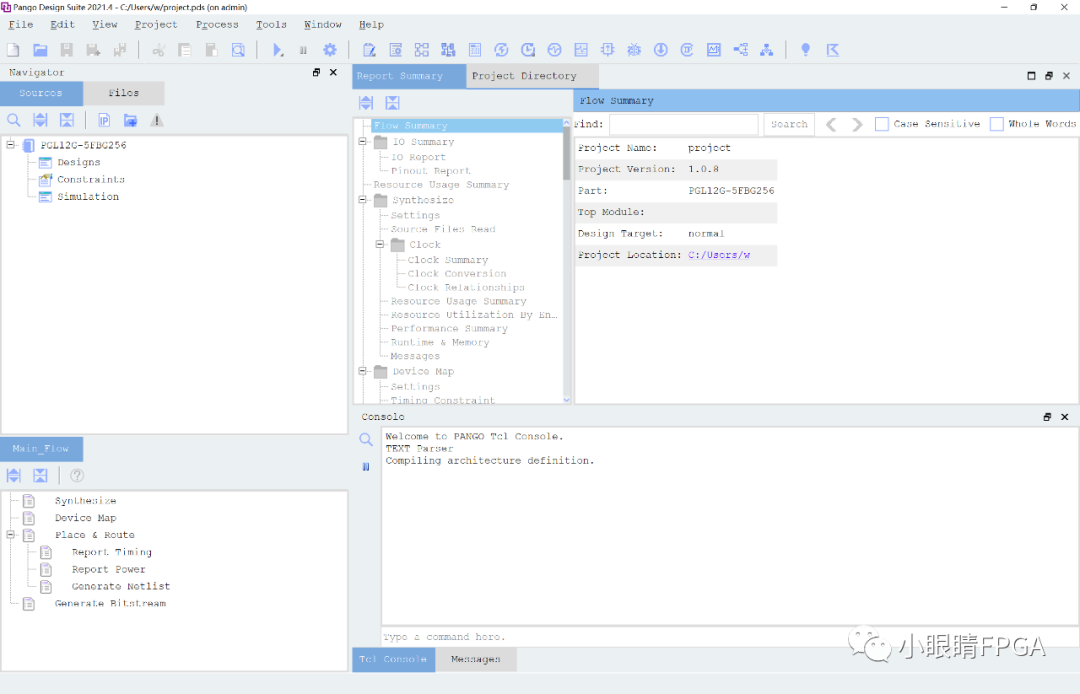

1.5.2 添加设计文件PDS软件界面如下图:

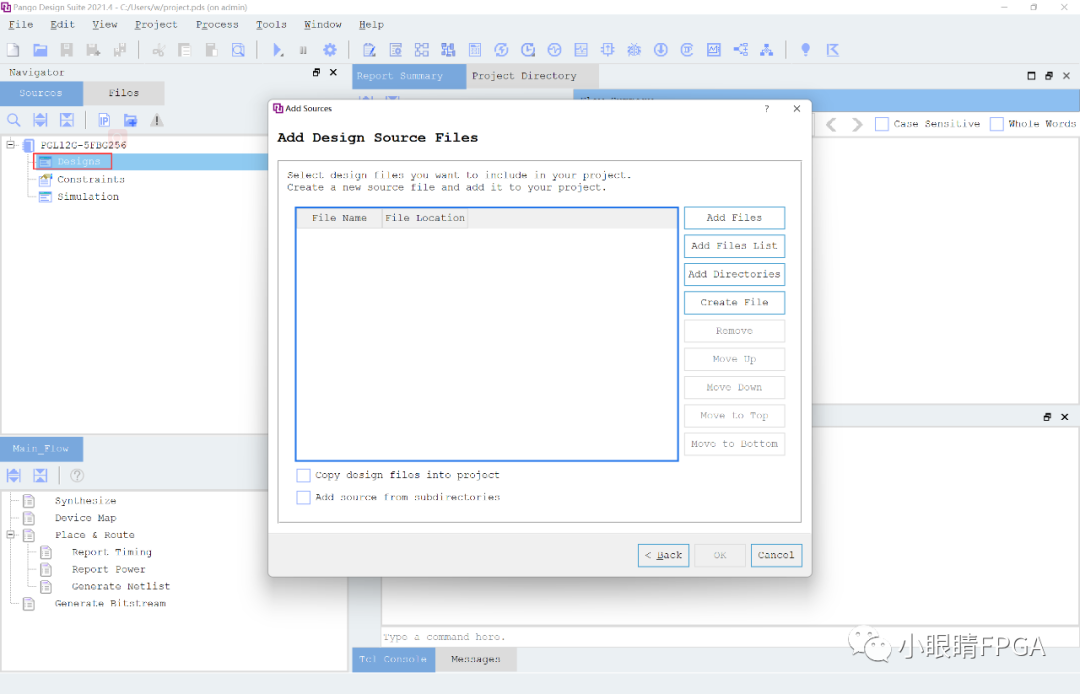

双击Designs,将前面设计的module新建到文件中,或者将前面编辑好的verilog文件添加到工程中:

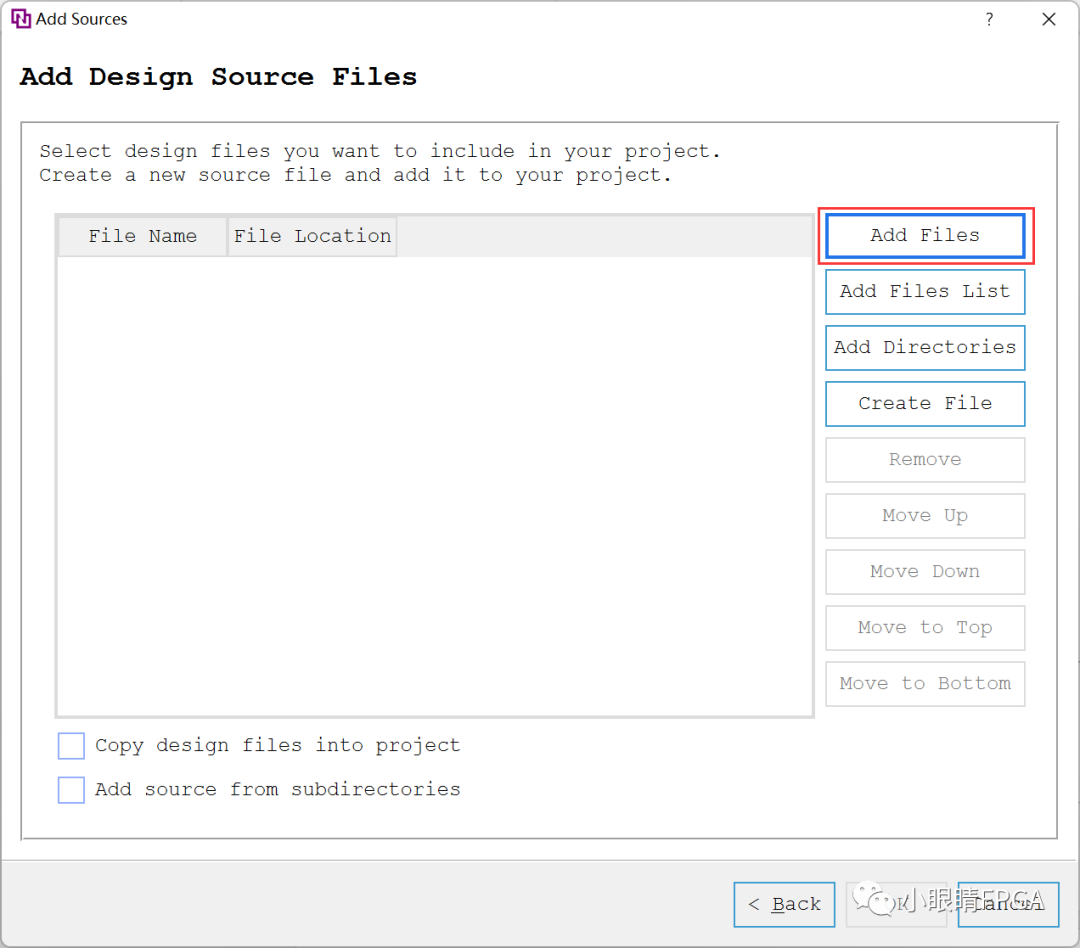

添加文件到工程:在窗口中点击Add Files,选择添加文件到工程;

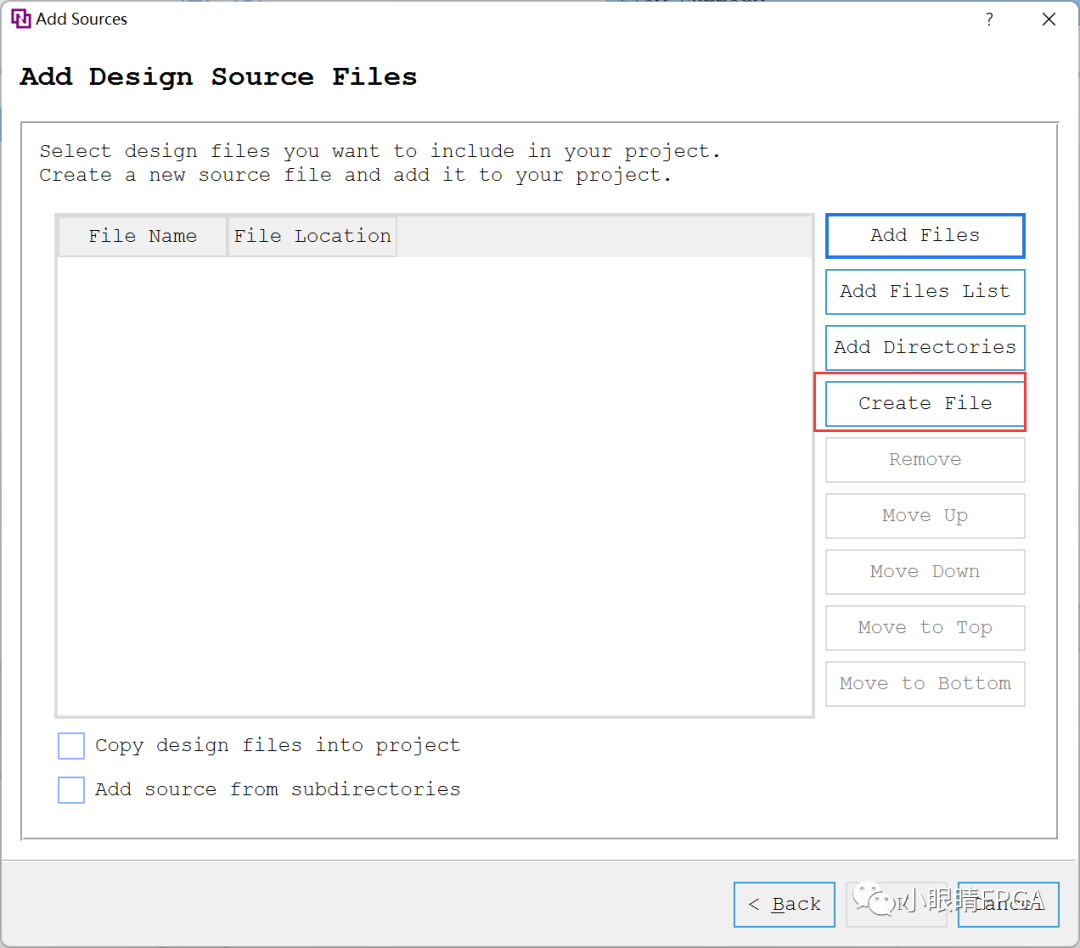

新建文件到工程:1)在窗口中点击Create File;

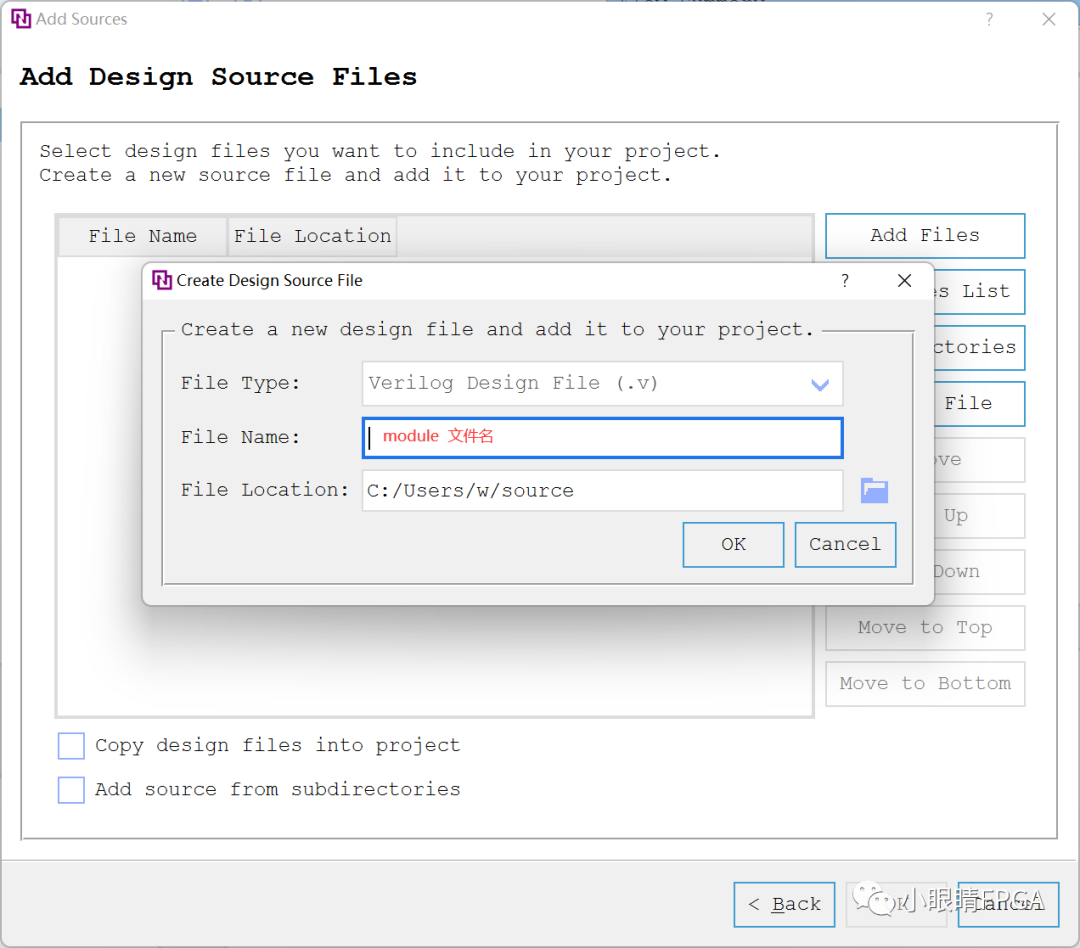

2)选择Verilog Design File,文件名和module名一致,默认路径,点击OK;

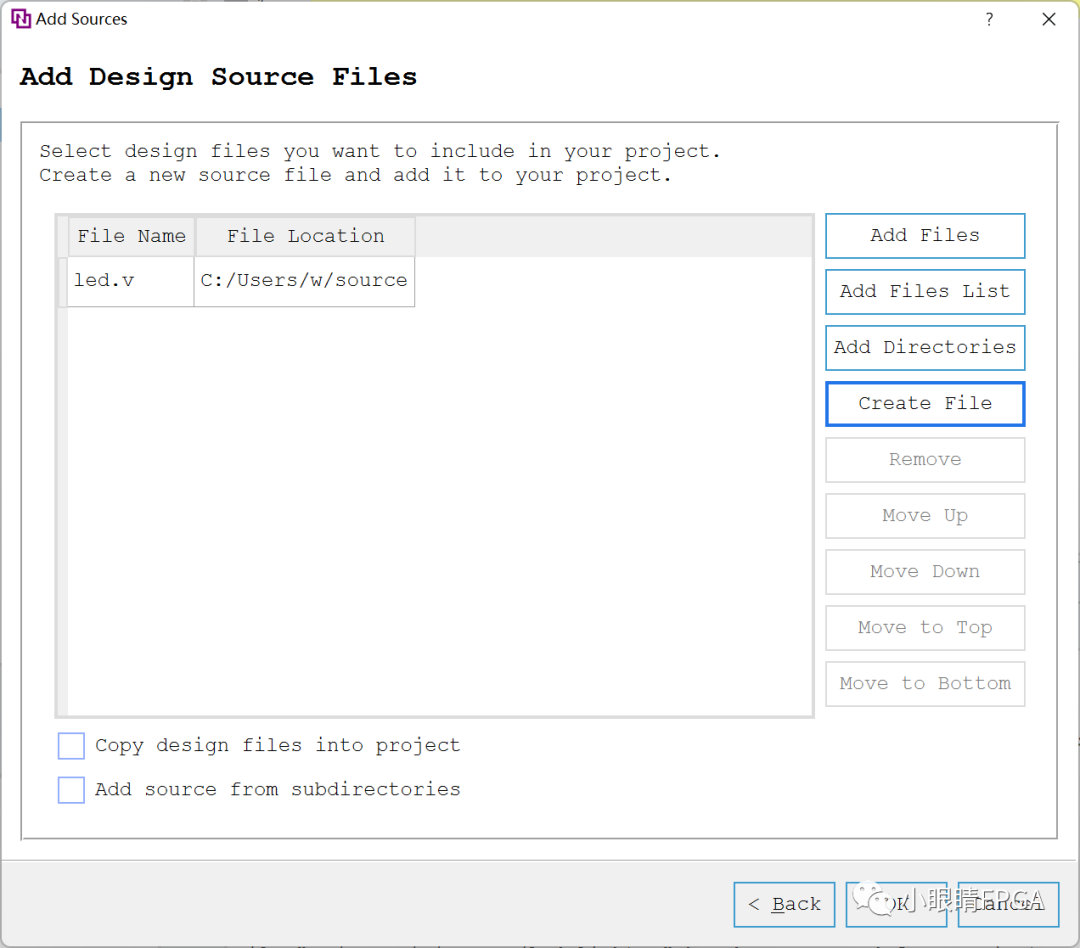

3)点击OK;

3)点击Cancel;

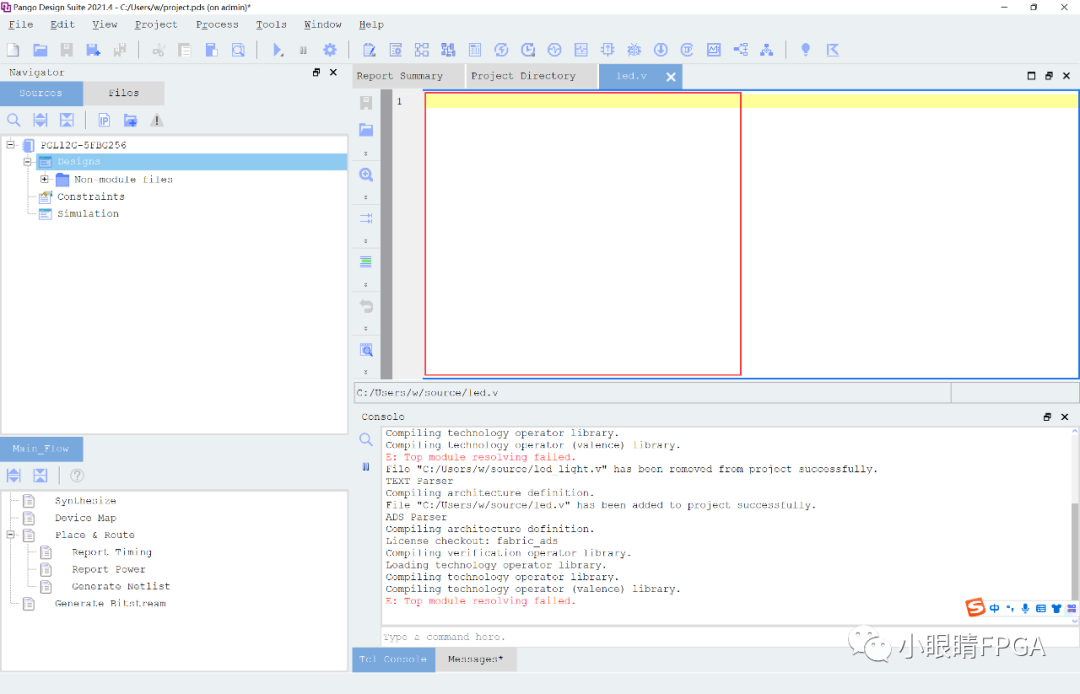

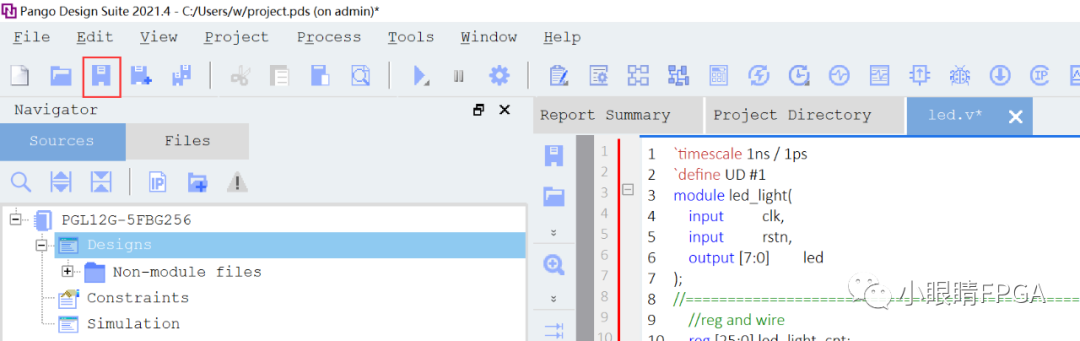

4)默认打开新建文件,将前面设计的module复制进去,

5)点击保存,新建文件完成

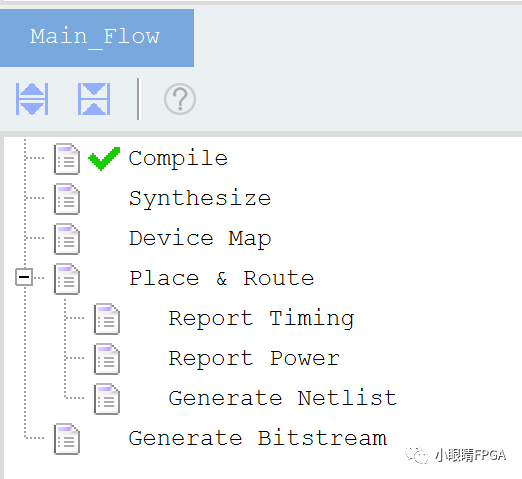

1.5.3 编译双击Compile或右击选择Run,编译完成后如下;

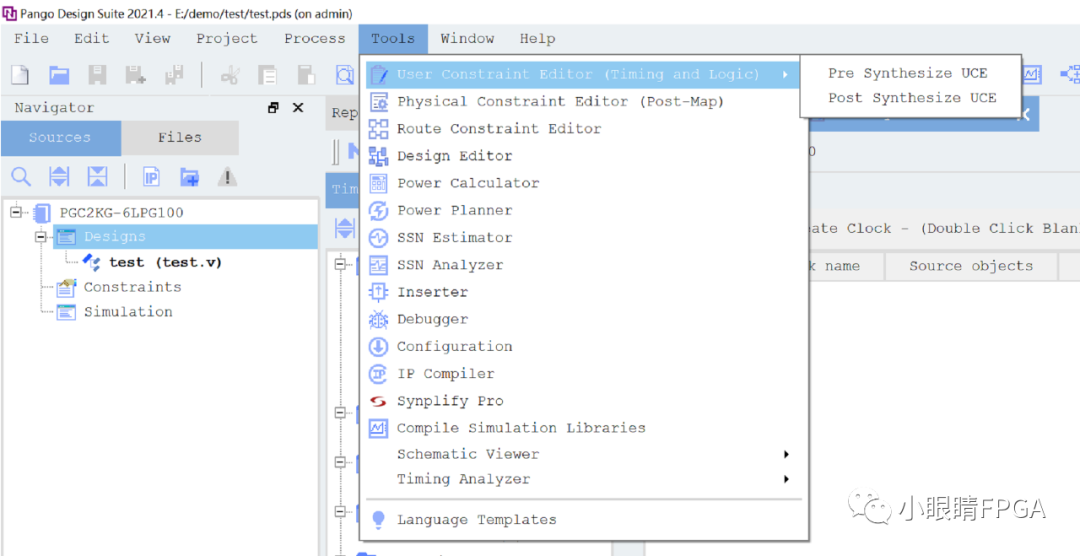

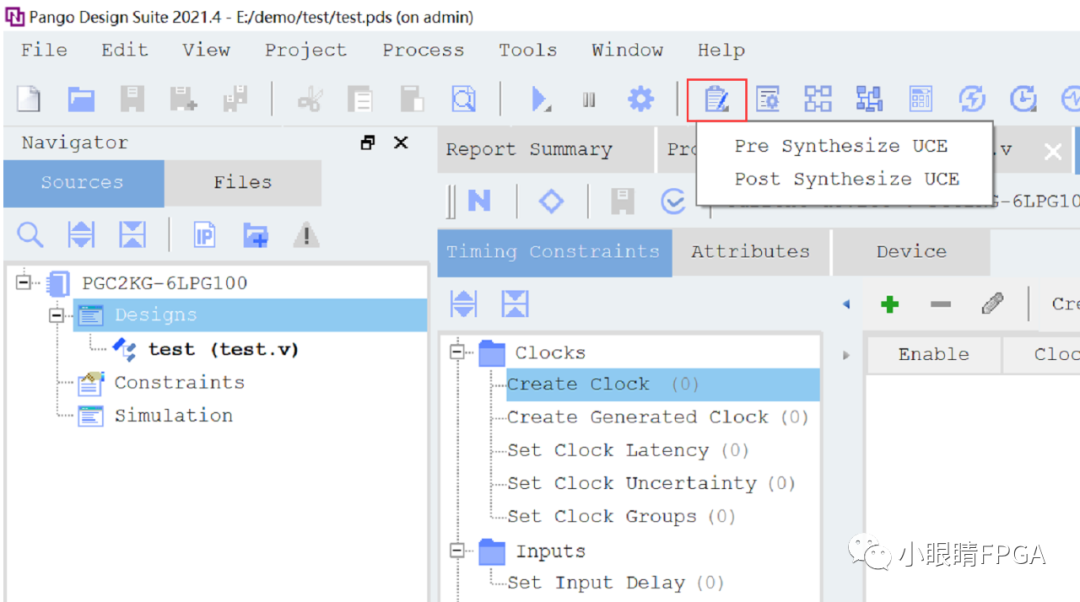

1.5.4 工程约束点击Tools选择User Constraint Editor(Timing and Logic)或者点击工具栏图标User Constraint Editor(Timing and Logic) 选择Pre Synthesize UCE,如下图所示。

Tools 下的User

Constraint Editor(Timing and Logic)

工具栏User Constraint Editor(Timing and

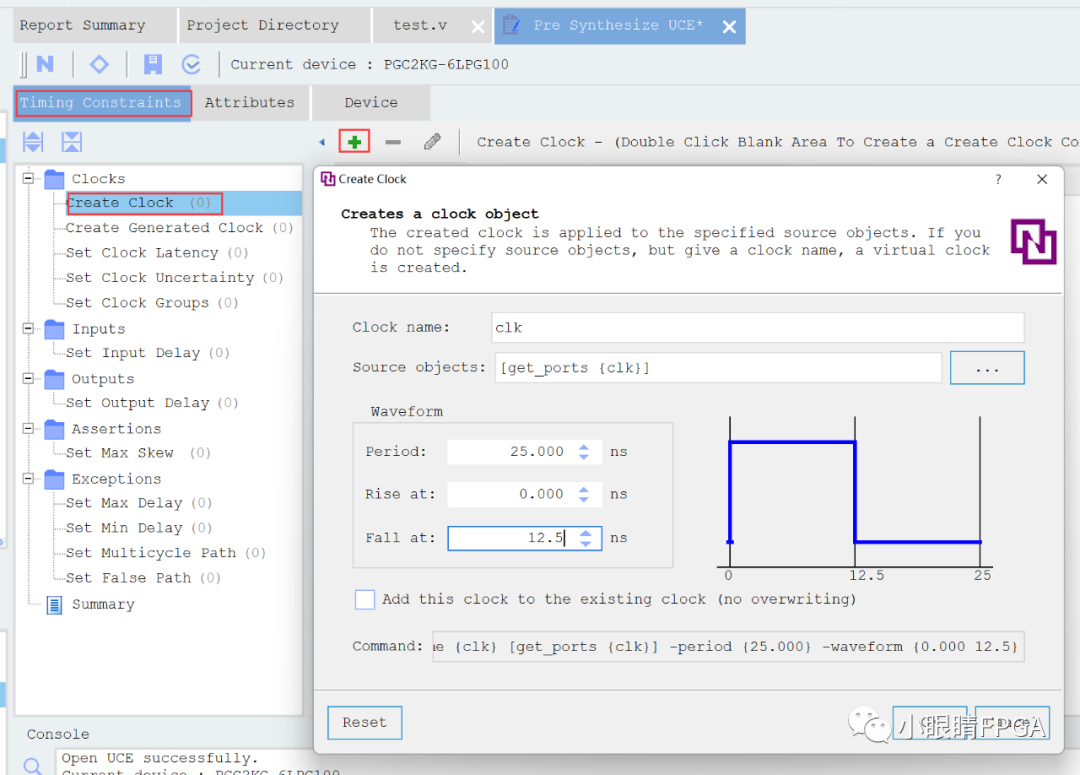

Logic)图标1.5.4.1 时钟约束打开UCE后,选择Timing Constraints后选择Create Clock添加基准时钟,基准时钟一般是通过输入port输入用户涉及的板上时钟。

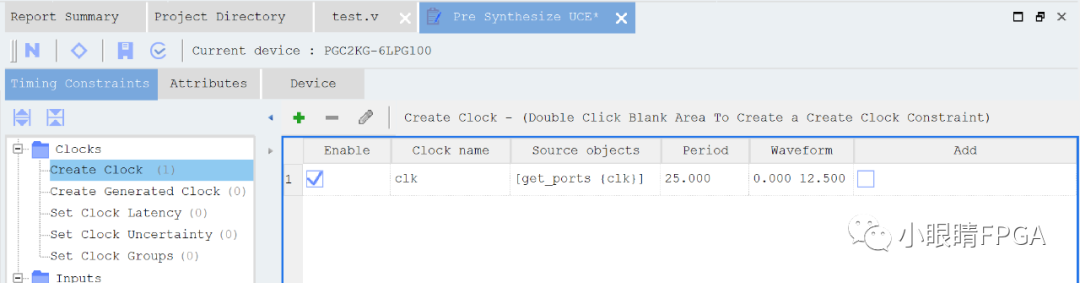

在弹窗中对时钟命名,关联时钟管脚,添加时钟参数,点击OK会创建一条时钟约束,Reset重置该页面。创建完成如下图所示:

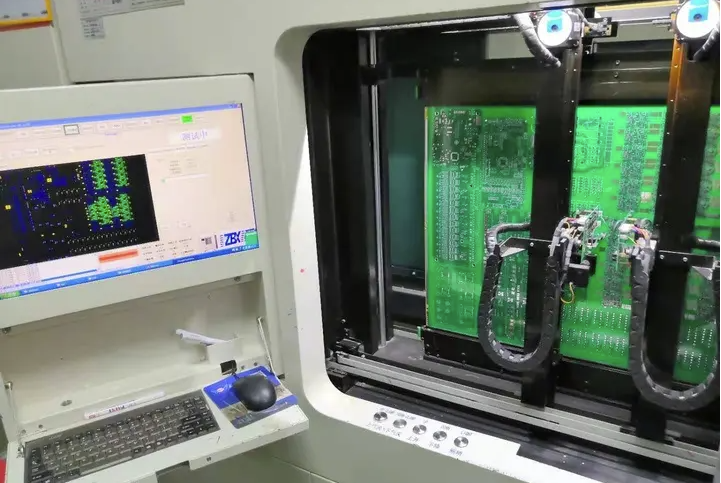

1.5.4.2 物理约束

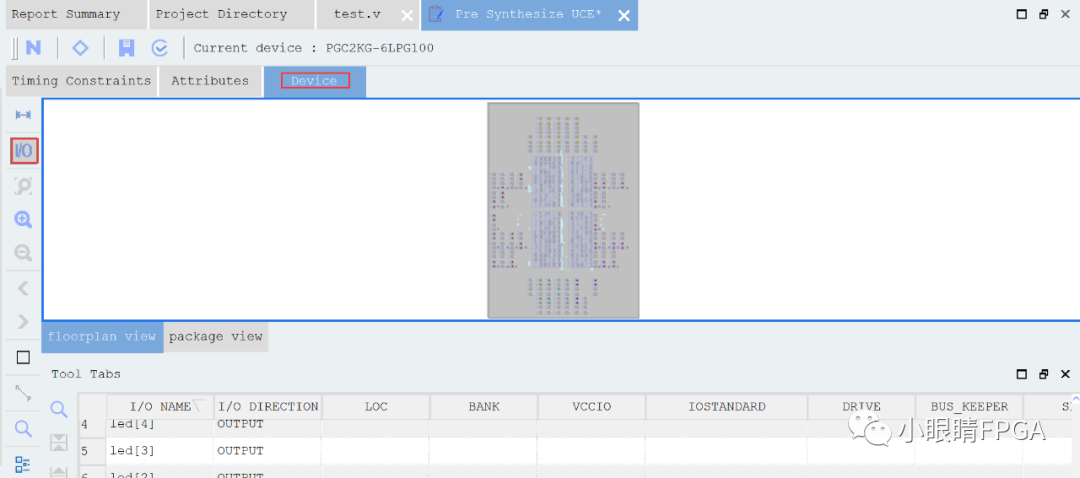

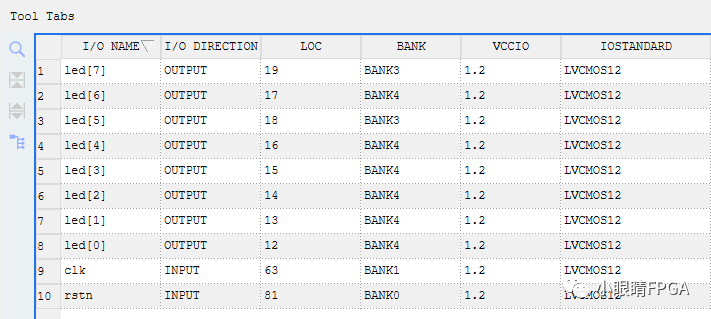

打开UCE后,选择Device后选择I/O,根据原理图编辑IO的分配。

编辑好IO分配后,点击保存,完成约束。1.6 生成位流文件并下载双击Generate Bitstream或右击选择Run,生成二进制位流文件。下载位流文件请参考《PDS快速使用手册》2.8下载位流文件1.7 实验现象8个LED灯同时亮和灭,亮和灭之间间隔时间为0.5s。

暂无评论