凡亿助教-小美

凡事用心,一起进步打开APP

公司名片立创EDA梁山派-刺猬作业评审报告

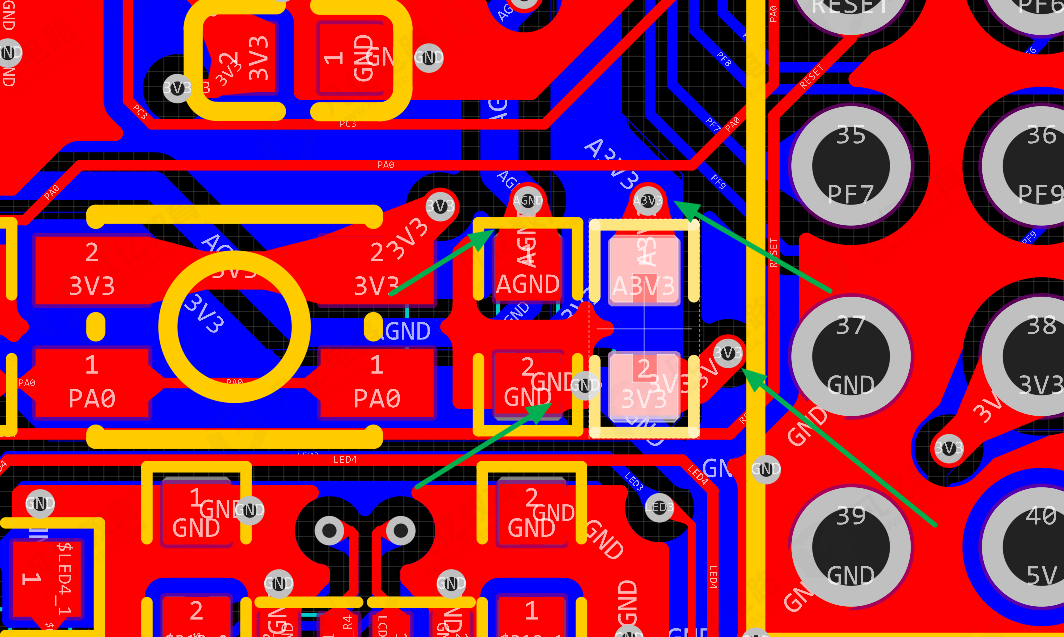

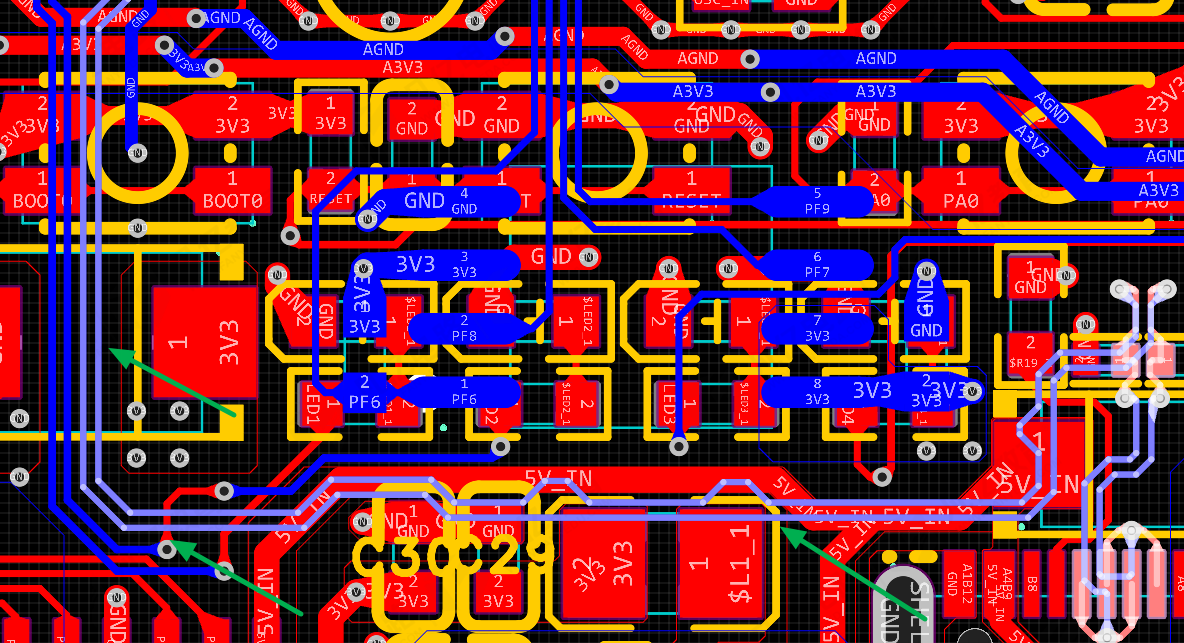

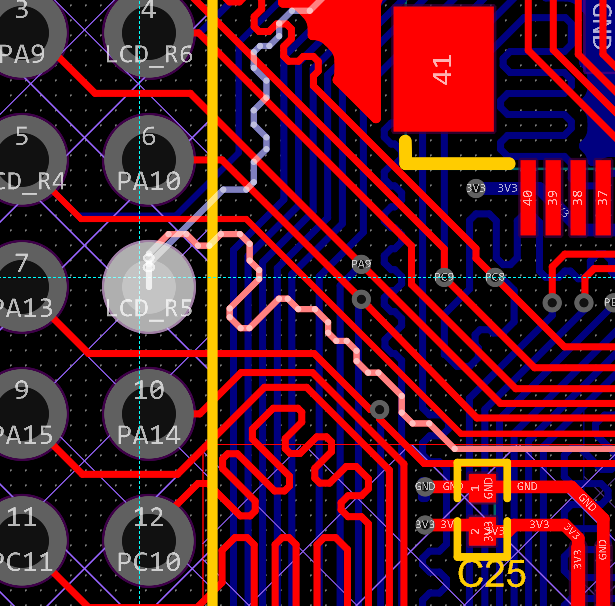

1. 模拟数字连接处电容要多打孔加大载流。

2. 走线避免锐角,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊

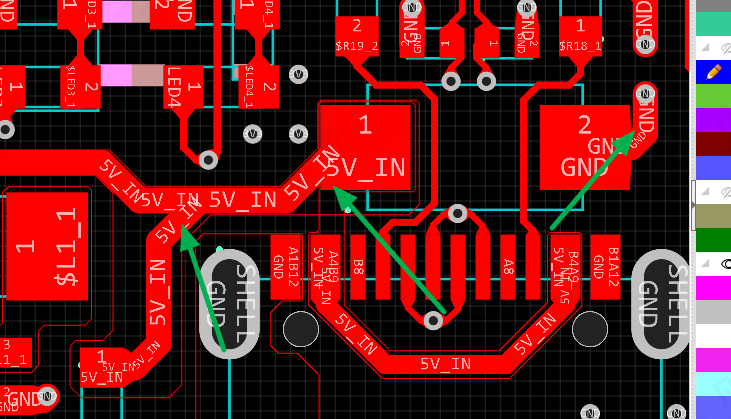

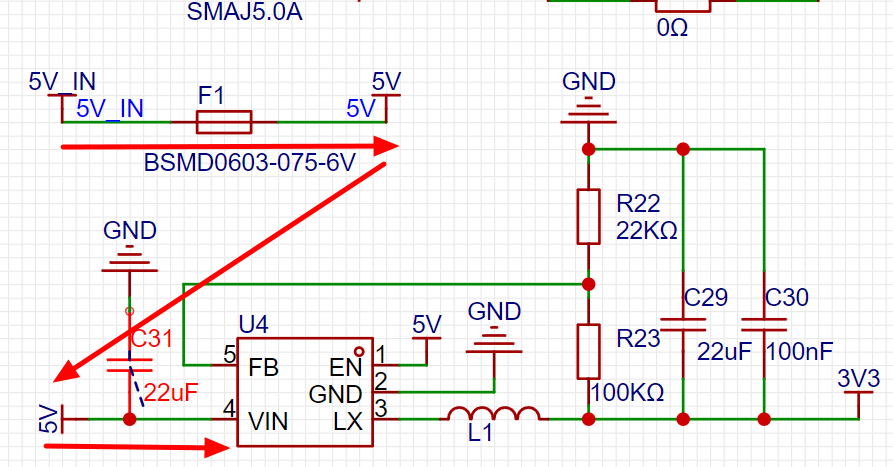

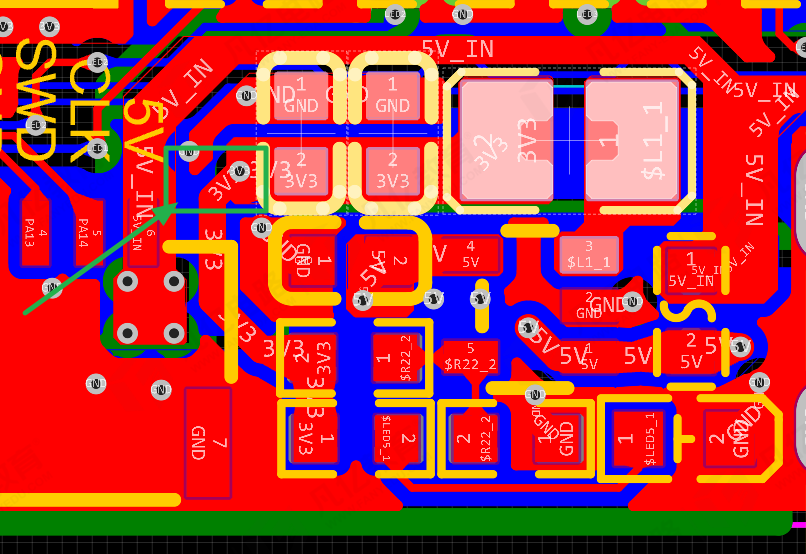

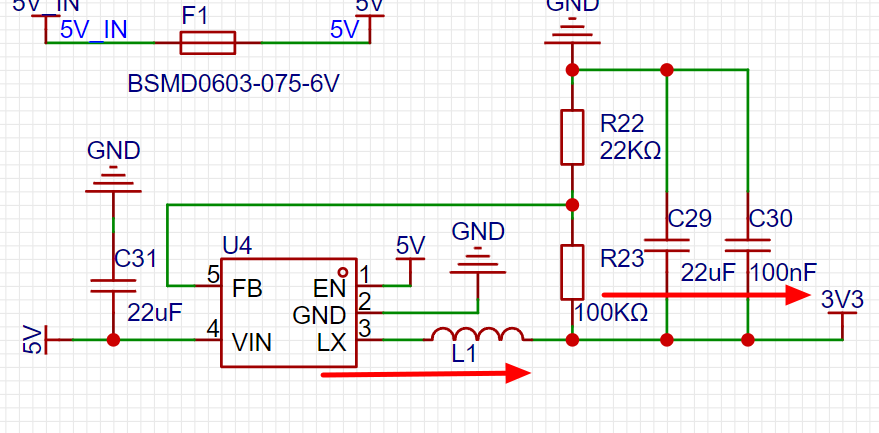

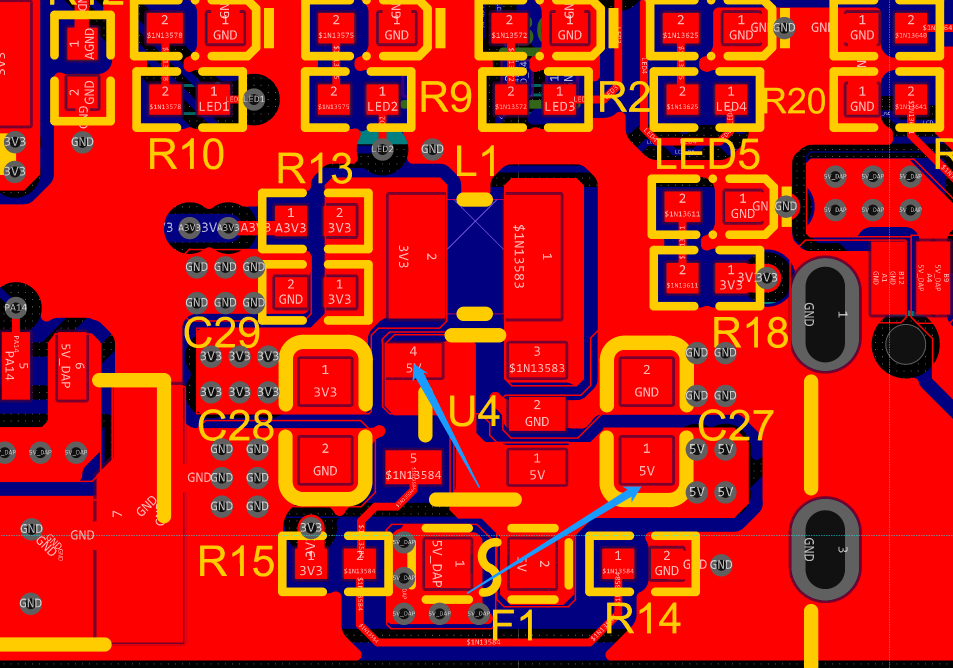

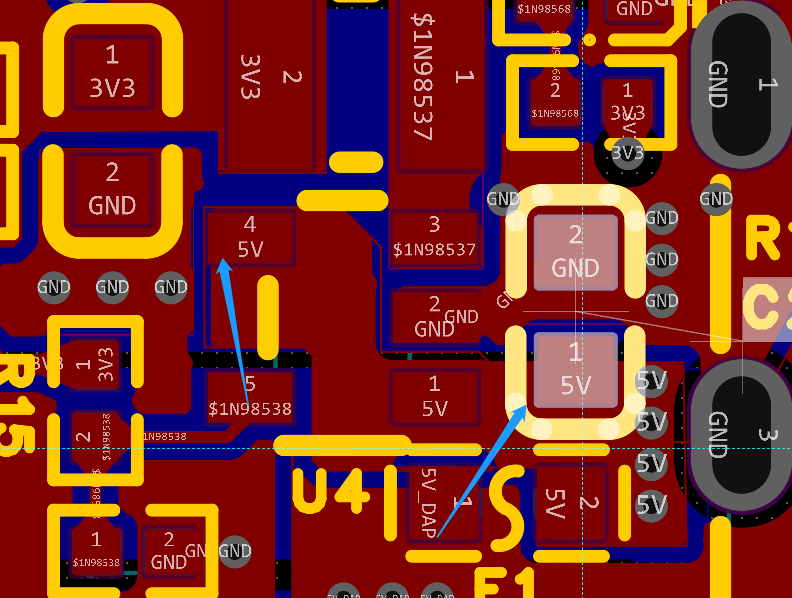

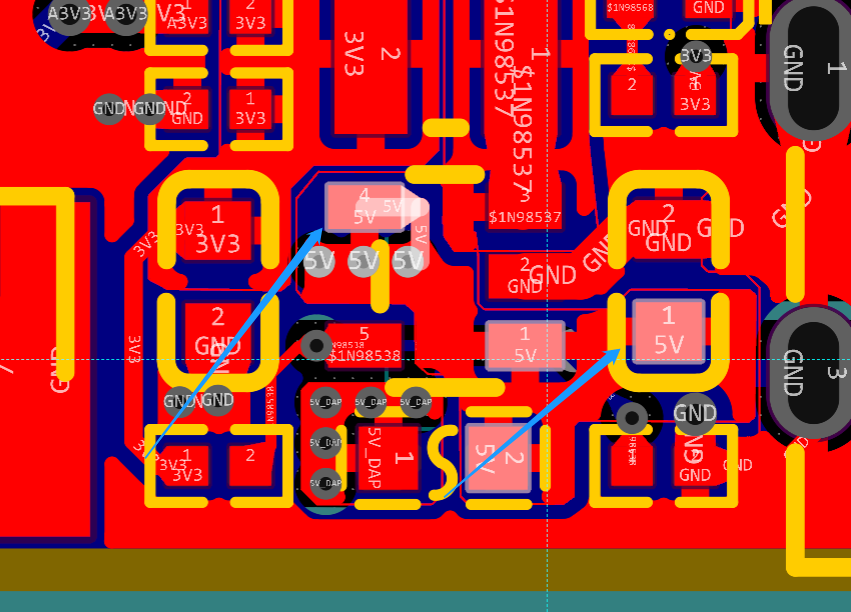

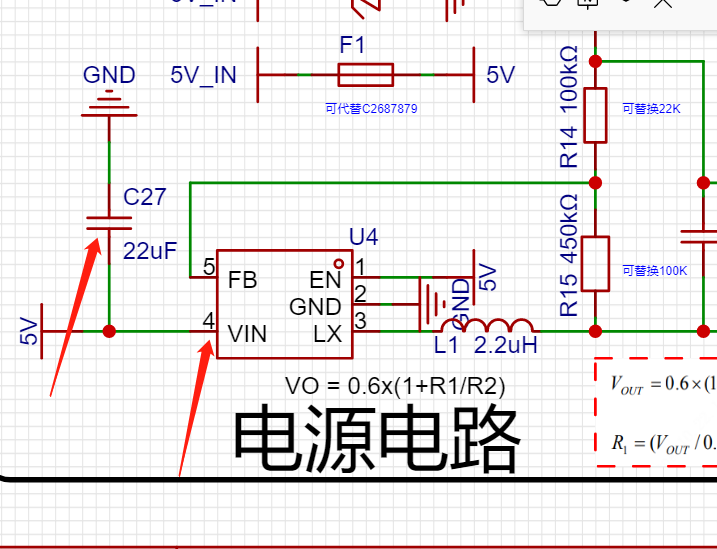

3. 电源模块输入应该从F1-C31-U4.4pin;要f1连接到c31到u4.4脚在到1脚。

4. 电源模块输出路径应该铺铜或走线加粗多打过孔加大载流

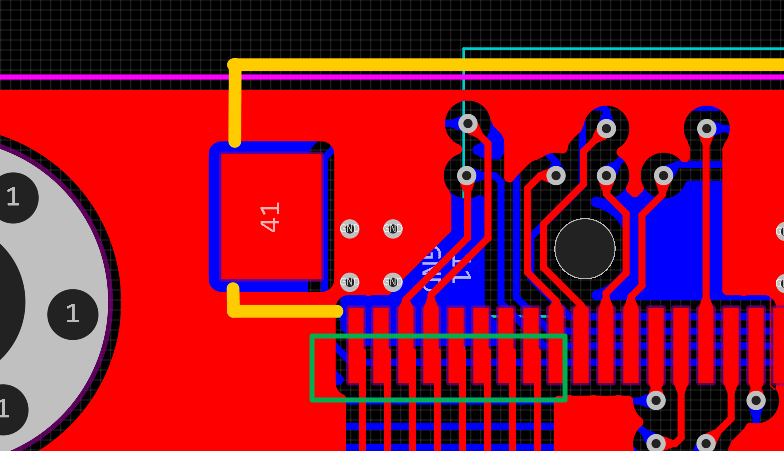

5. TypeC差分对走线应该包地处理,打孔换层需要在旁边打一对地过孔。

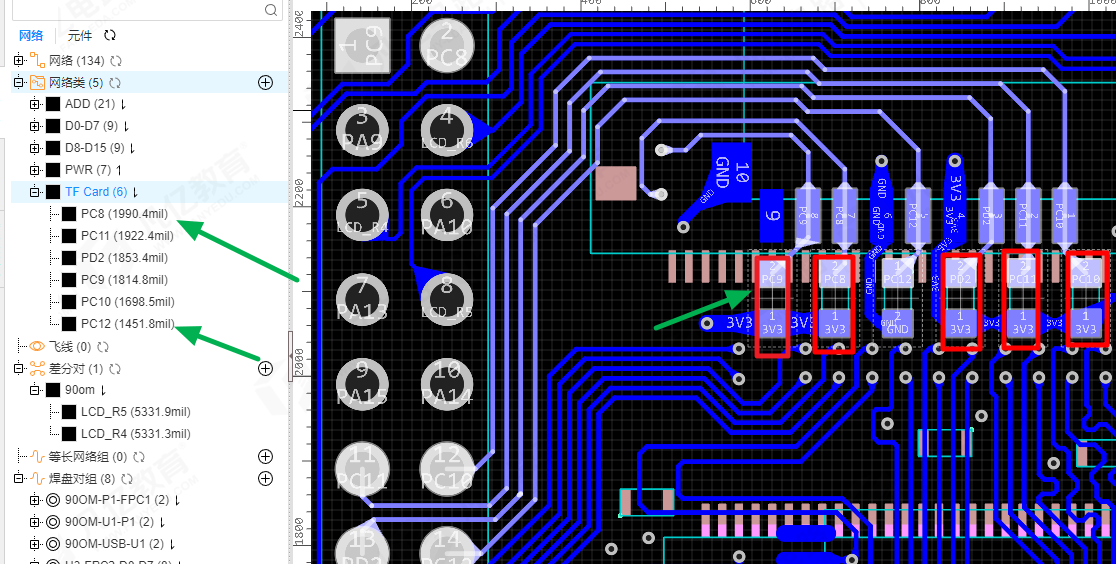

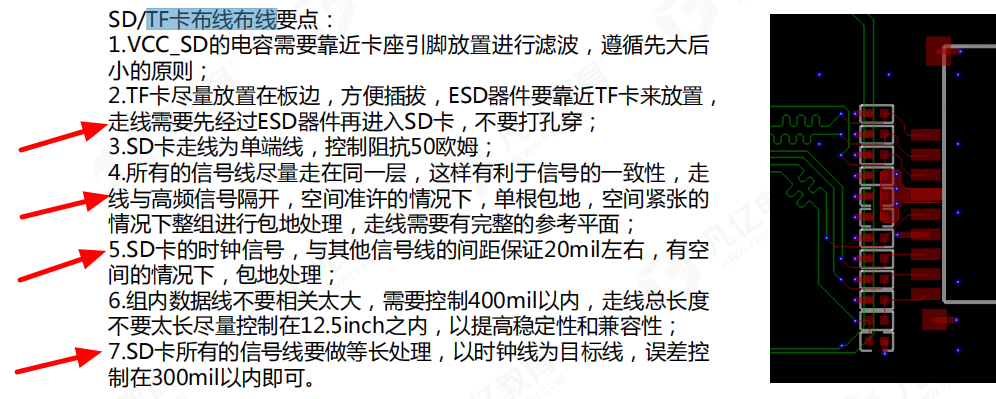

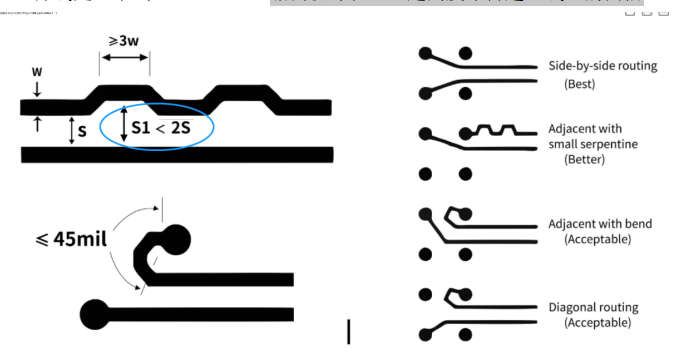

6. 走线需要先经过ESD器件再进入TF卡,TF卡所有信号线需要等长,以时钟信号为目标误差300mil。

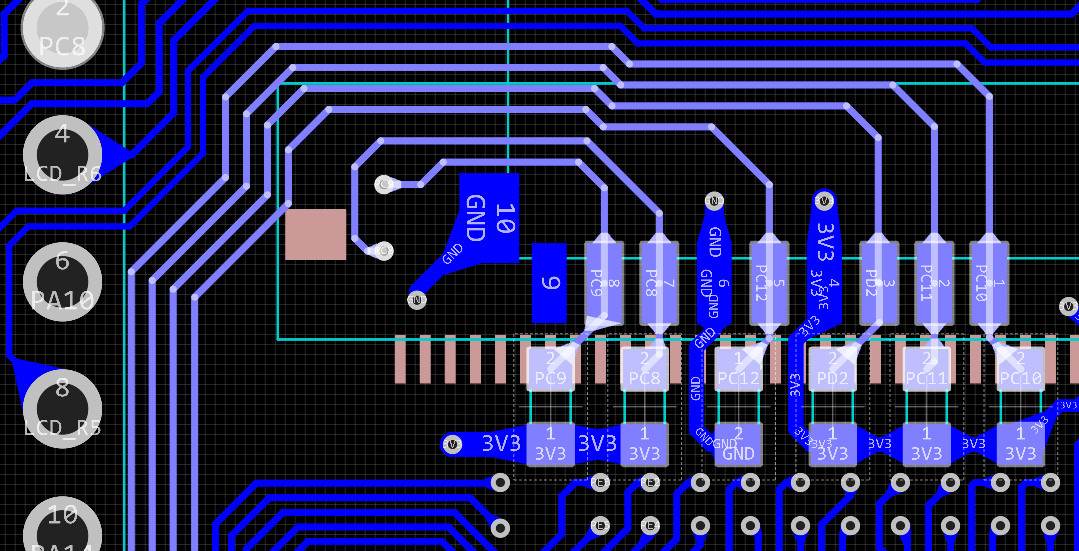

7. 要单根包地,空间紧张整组包地;时钟信号和其他信号保持20mil有空间单根包地。

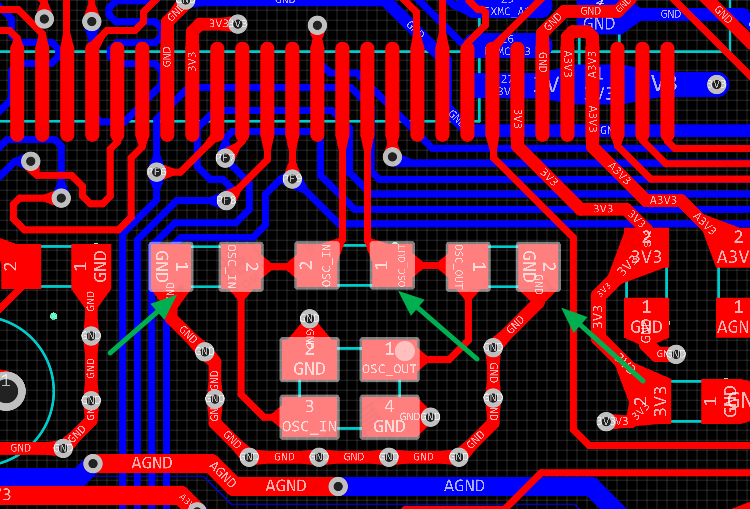

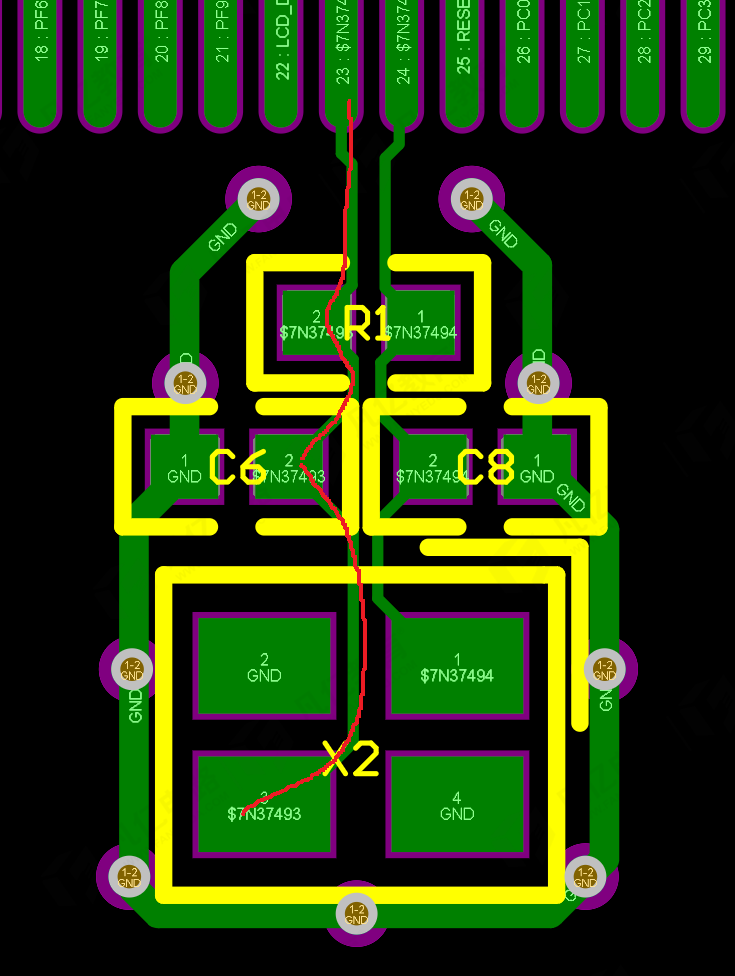

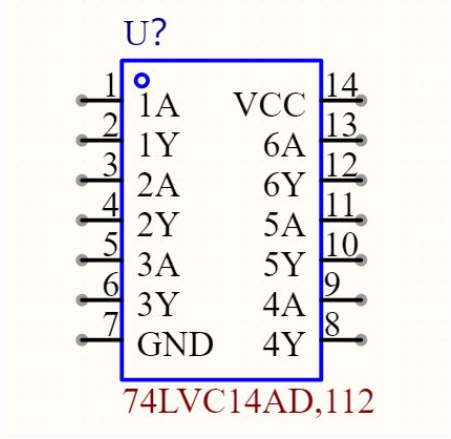

8. 晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。

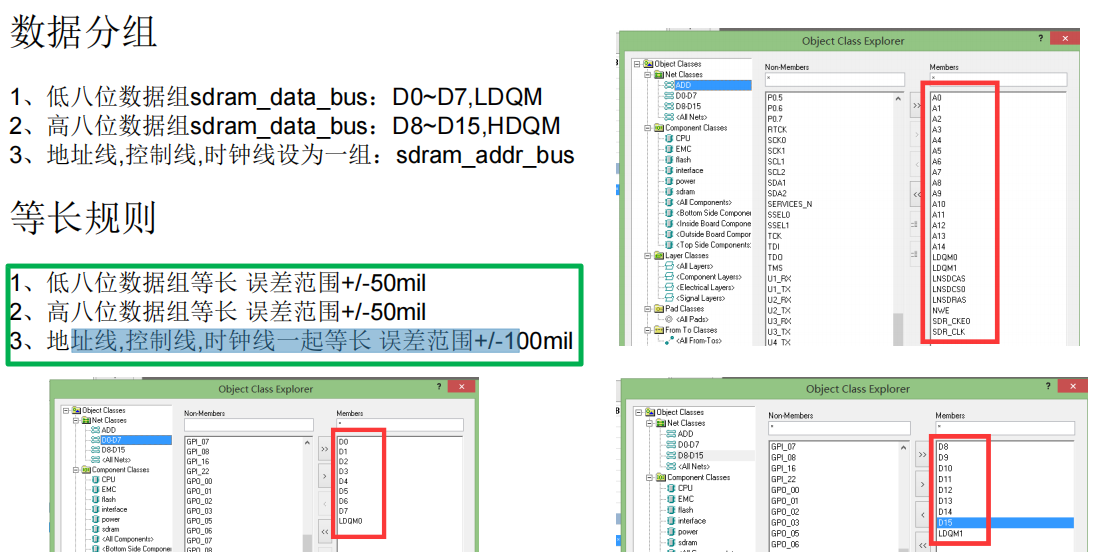

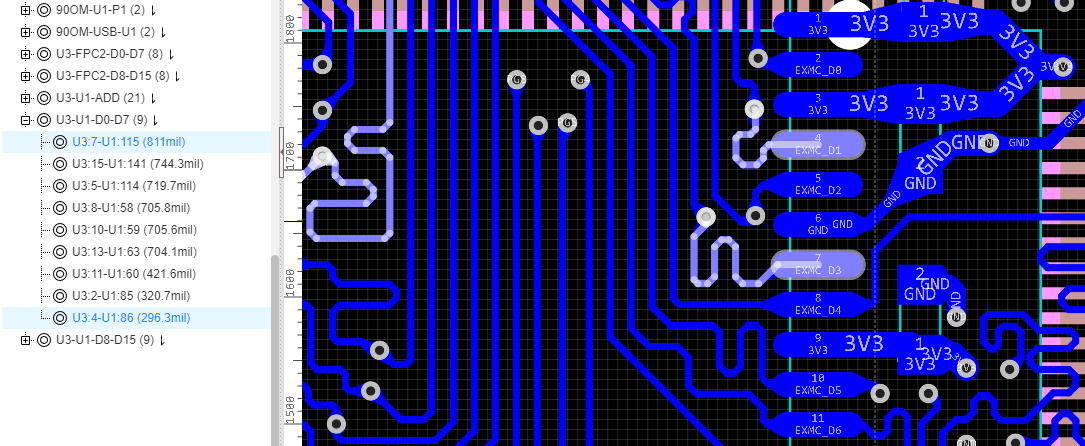

9. SDRAM等长误差数据线控制+-50地址线+-100

以上评审报告来源于凡亿教育梁山派pcb设计特训营作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教:

![e787b929638417b223f5c5c9a30aa0[1].png](https://api.fanyedu.com/uploads/ueditor/image/20230130/1675048100366139.png)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论