前期为了满足各项设计的要求,通常会设置很多约束规则,当一个PCB设计完成之后,通常要进行DRC。DRC就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项连接性规则检查,常见的检查包括开路及短路的检查,更加严格的还有差分对、阻抗线等检查。

一、DRC检查

1.1 DRC设置

DRC就是检查设计是否满足所设置的规则。需要检查什么,其实都是和规则相对应的,在检查某个选项时,请注意对应的规则是否进行勾选。

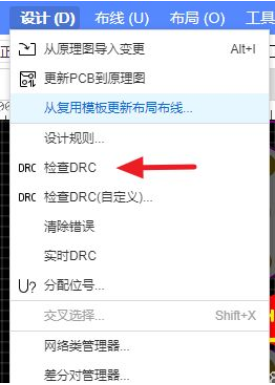

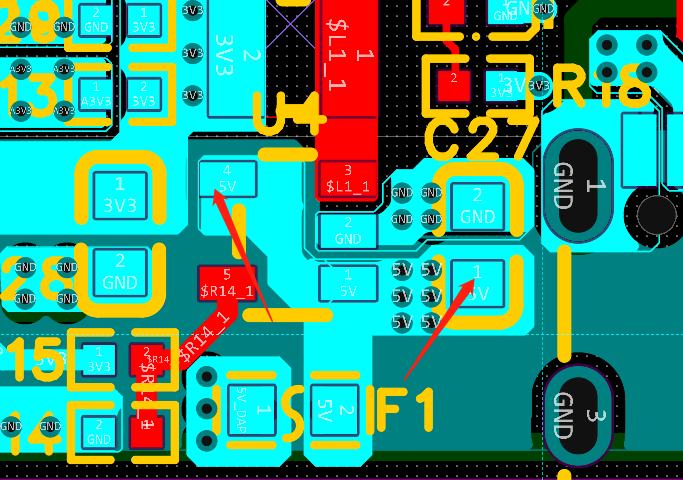

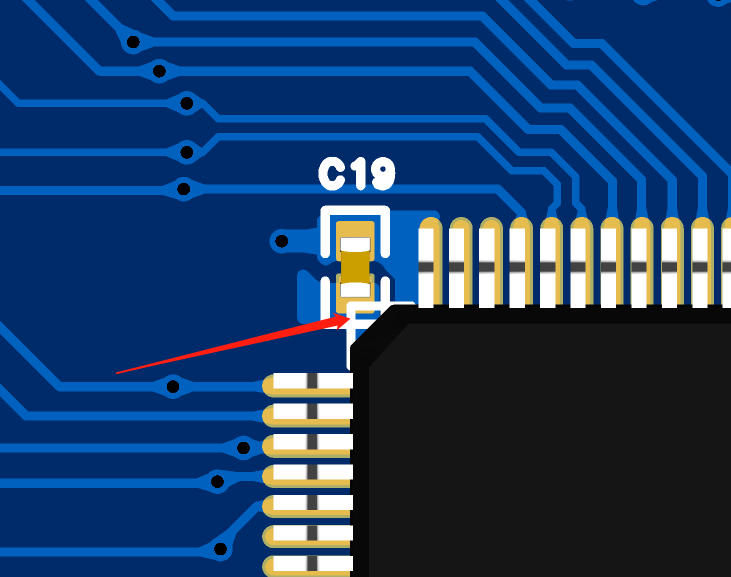

1)执行菜单命令“设计-检查DRC,如图1-1所示。

图1-1 打开DRC设置命令

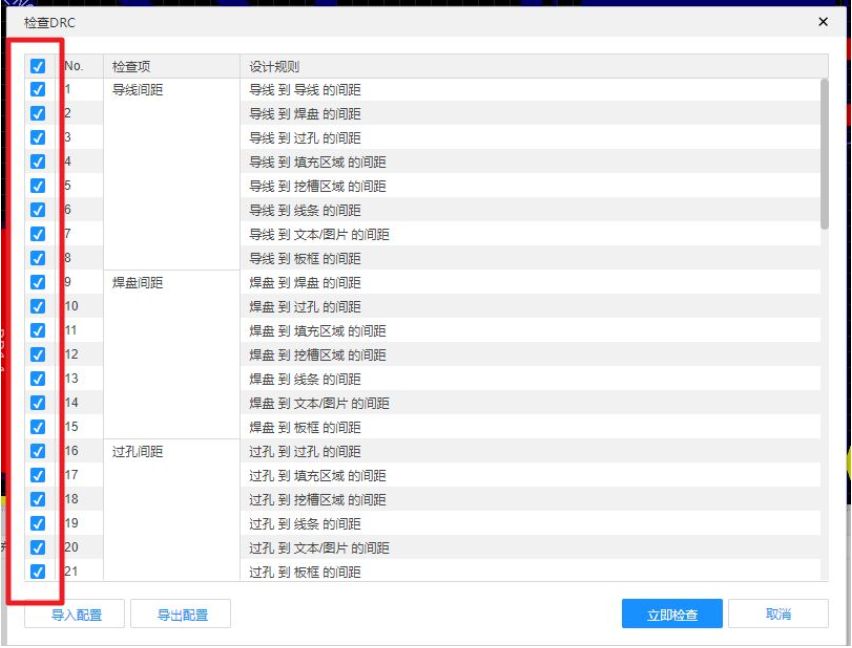

图1-2 设计规则检查器

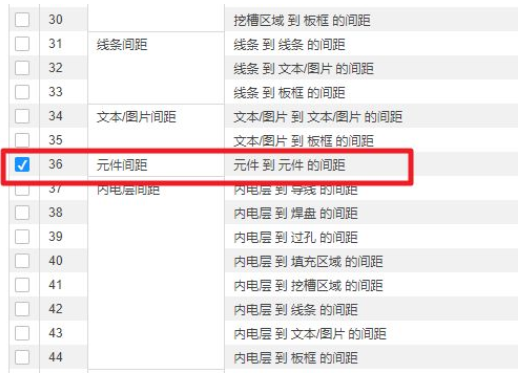

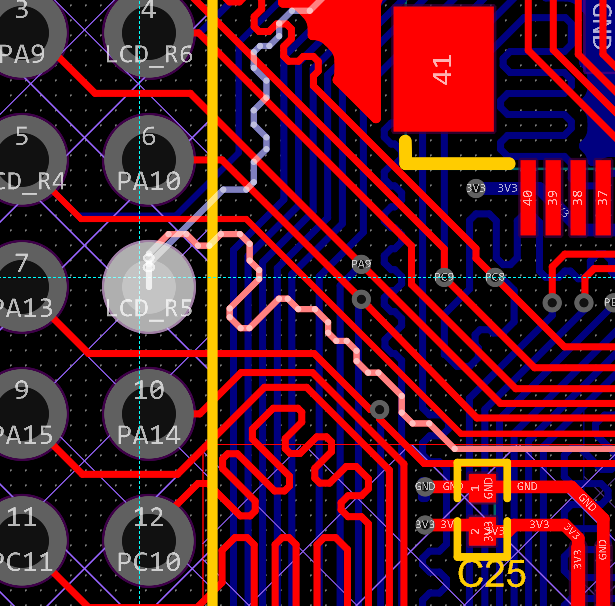

2)设置DRC检查选项:“设计-检查DRC(自定义)”,选择需要检查的规则项在前面进行勾选,如图1-2所示。

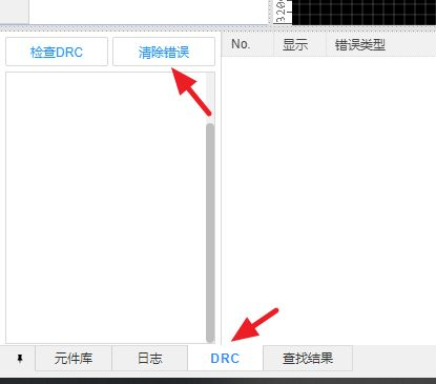

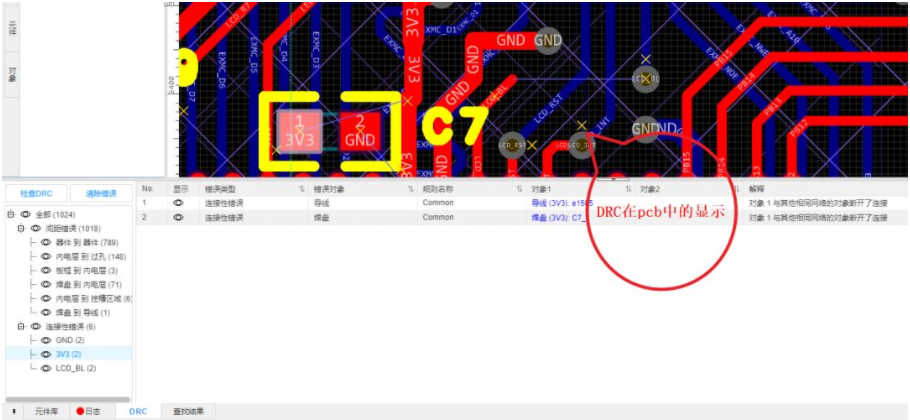

3)检查的DRC结果在底部的DRC面板显示。如图1-3所示。

图1-3 DRC详细报告内容

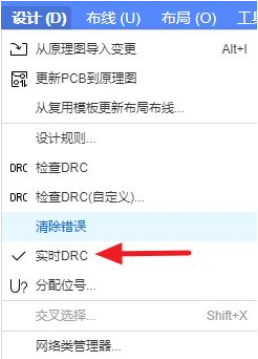

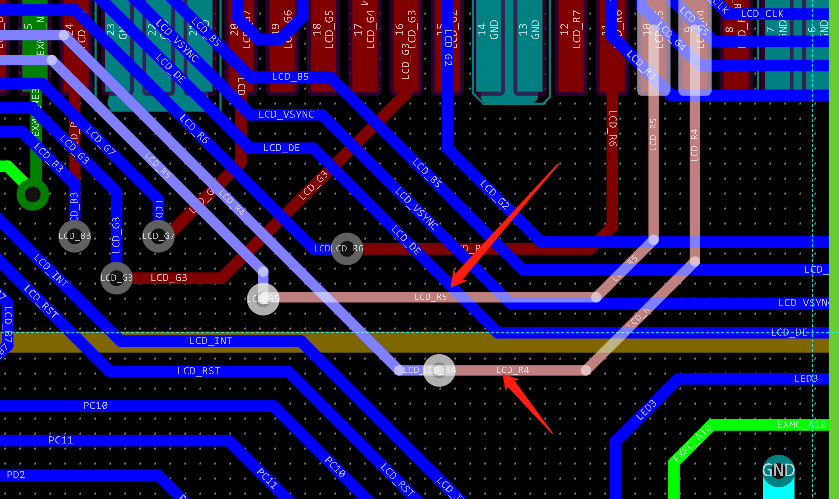

4)开启实时DRC:执行菜单命令“设计-实时DRC”;开启实时DRC时,能在绘制PCB过程中实时报告错误,显示黄色的 X 标识。开启实时DRC选项时,会弹窗提示是否执行一次DRC检查,直接点击是。前面有√,表示已开启;如图1-4所示。

图1-4开启实时DRC

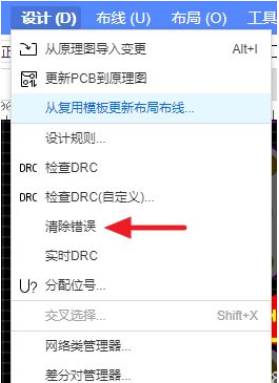

图1-5(A)清除错误

图1-5(B)清除错误

5)清除错误:“ 设计 - 清除错误”,如图10-5(A B)所示;将DRC检查复位,清空画布的DRC错误标识;或者在底部面板- DRC -清除错误,即可把检查后的DRC清除复位。

DRC不是说所有的规则都需要检查,设计者只需要检查自己想要检查的规则即可。下面对常见的几种DRC进行详细的描述。

1.2 连接性检查

连接性检查包括对象与其他相同网络的对象的断开连接(开路检查)、游离的铜块(孤铜)、游离的导线,如图1-6所示。

图1-6 连接性检查设置

图1-7 间距规则检查

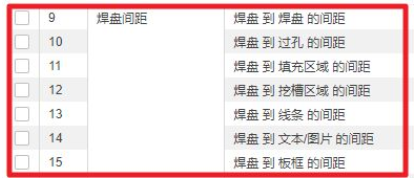

1.3 间距规则检查

间距规则检查包括导线间距、过孔间距、焊盘间距、填充区域、挖槽区域间距、铺铜间距、如图1-7所示。

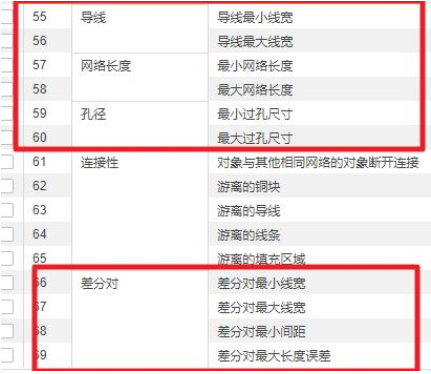

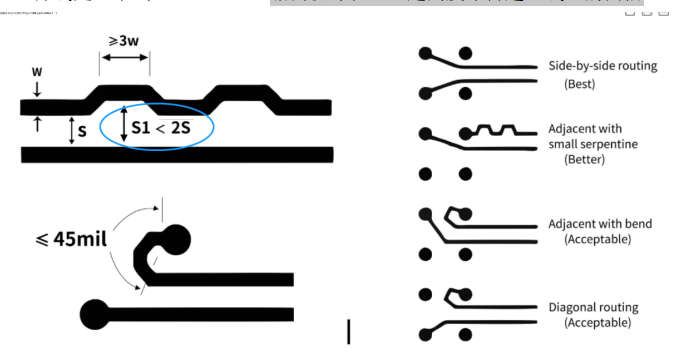

1.4 布线检查

如图10-8所示,布线检查包含导线检查、网络长度检查、孔径检查、差分对检查,当设置的线宽、过孔大小及差分线宽不满足规则约束要求时就会提示DRC报错,让设计者注意。

图1-8 导线检查、网络长度检查、孔径检查、差分对检查设置

小助手提示:一般在设计中,过孔的类型不要超过两种,这样再生产的时候可以少用钻头类型,提高生产效率。

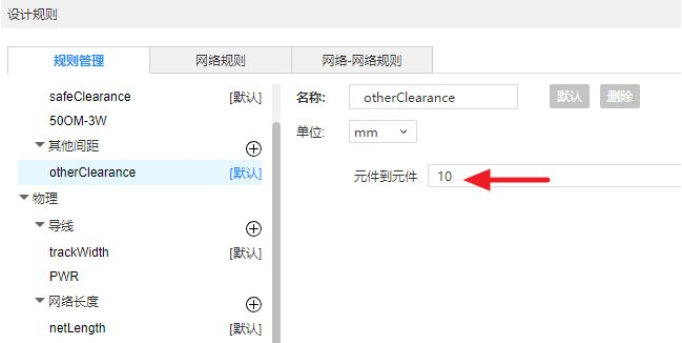

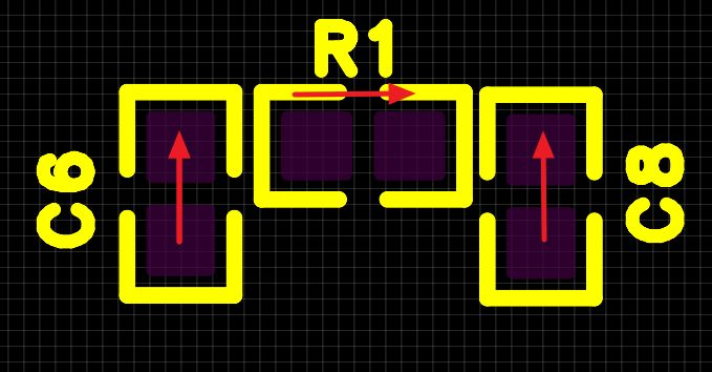

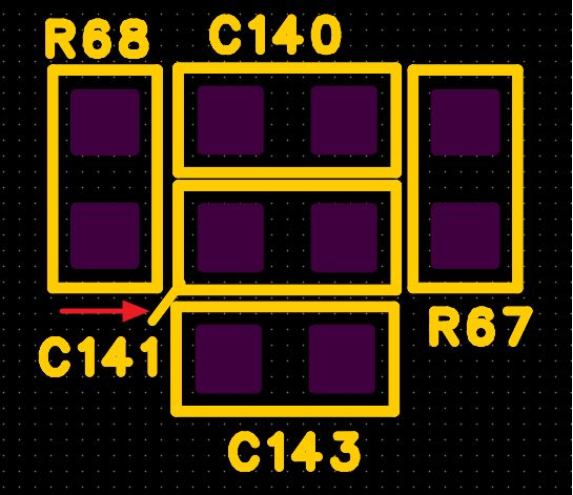

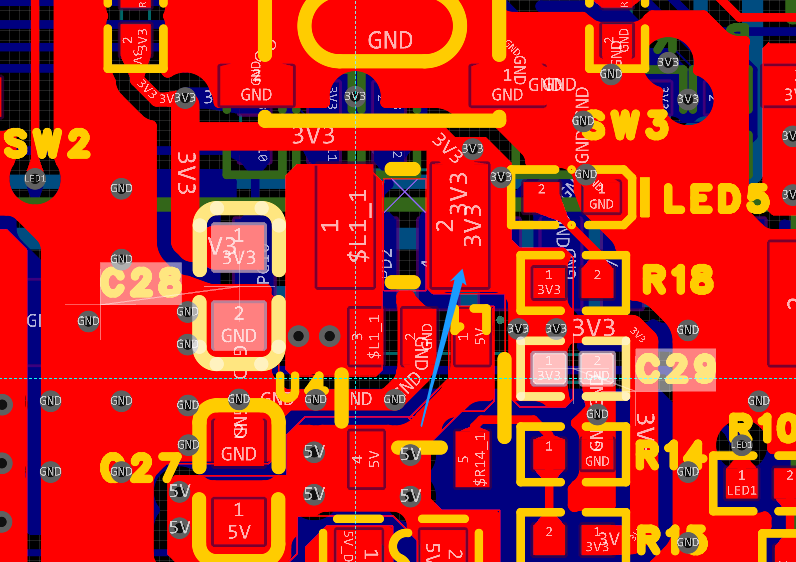

1.4 元件间距检查

大部分板子设计都是手工布局,难免存在元件重叠的情况,需要对元件间距进行检查,防止后期元件装配时出现干涉,如图1-8和图1-9所示。

图1-9 元件间距设置

图1-10 元件规则检查

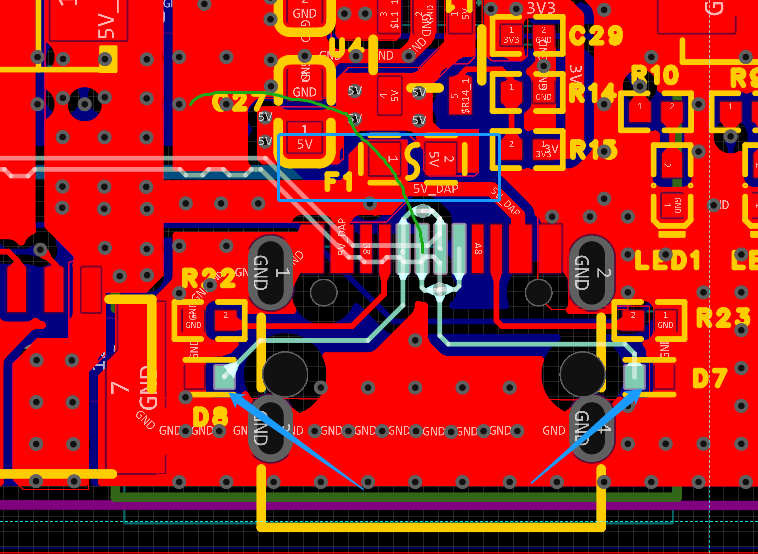

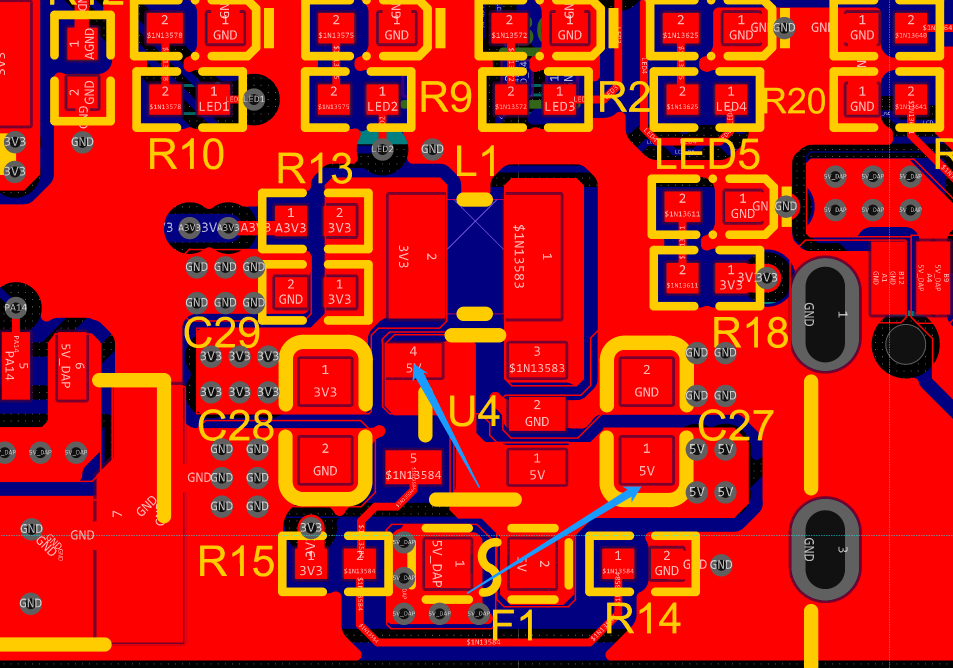

对上述常见的DRC检查选项设置勾选之后,执行DRC菜单右下角的“立即检查”命令,运行DRC,检查的DRC结果在底部的DRC面板显示,对应的PCB也会有一个 X 的符号。

图1-11 DRC报告

鼠标单击“错误类型”可在PCB高亮定位,双击会放大并定位错误点,可以有针对性地对这个DRC报错修正,可以接受的DRC报错可以直接忽略。例如,焊盘在禁止布线层边线上,会出现间距报错,这种可以直接忽略不管。

重复上述步骤直到所有DRC报错更改完成,没有DRC报错或者所有DRC报错可以忽略为止,即完成DRC。PCB电路设计通过DRC,可以进行下一步骤。

声明:本文凡亿教育原创文章,转载请注明来源!

暂无评论