凡亿助教-小美

凡事用心,一起进步打开APP

公司名片高速PCB技巧:如何做好走线阻抗设计?

走线阻抗是高速PCB设计的重要内容,随着电子系统复杂度越来越高,阻抗的危害也越来越大,工程师为保证产品竞争力需要做好阻抗设计,而阻抗的来源之一是走线,今天谈谈如何做好走线阻抗设计,降低其影响。

一般来说,常见的走线阻抗可分为单端50ohm和差分100ohm,当然越来越多的阻抗类型也出现,如27ohm、33ohm、75ohm、120ohm(diff)等,但目前以50ohm和100ohm为主。

同一设计中可能会同时存在多个单线阻抗和差分阻抗,这就要求使用不同的走线宽度。所以下面将以多种走线阻抗来分析如何做好设计:

1、单线阻抗50Ω的设计

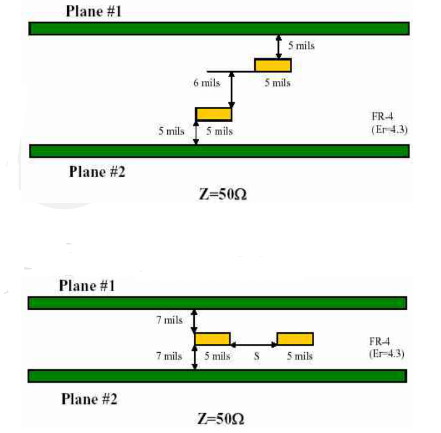

常见的单线阻抗是50ohm,一般误差控制范围是-10%-+10%,常见的单线结构有两种,如图所示:

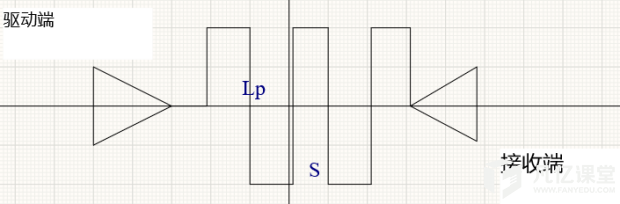

2、差分阻抗100Ω的设计

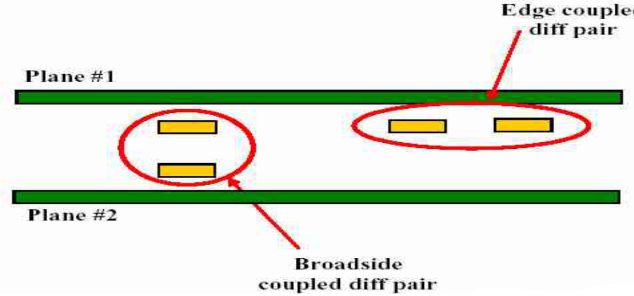

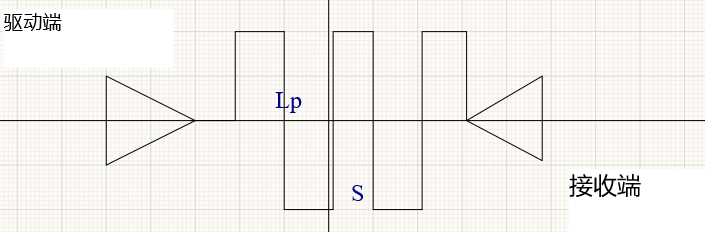

常见的差分阻抗是100ohm,一般误差控制范围是-10%-+10%,常见的差分结构有两种,如图所示,从性能上来说,两种结构是没有明显的差距,但从PCB加工阻抗控制角度来说Edge coupled diff pair更容写,也是最广泛应用;而Broadside coupled pair比较适合走线密集的地方,如芯片管脚出线等。

对于Edeg coupled diff pair有紧耦合和松耦合的区别。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论