凡亿教育-小叶

凡事用心,一起进步打开APP

公司名片高速PCB设计的蛇形走线和码间干扰

蛇形走线和码间干扰是高速PCB设计中需要关注的两个重要问题,在布线阶段若是没处理好蛇形走线和码间干扰,容易影响到系统性能和稳定性,下面讲讲如何处理这两个问题,希望对小伙伴们有所帮助。

蛇形走线是一种常用的布线方式,可以降低信号线之间的互相干扰,提高信号传输的稳定性和可靠性。但是,蛇形走线也存在一些缺点,比如会增加信号线的长度,从而增加信号传输延迟,而且布线的过程也比较复杂,需要进行大量的计算和优化。

码间干扰是不同信号线之间的互相干扰,通常会表现为信号失真、串扰等问题,影响信号的传输质量。在高速PCB设计中,需要采取一系列措施来减少码间干扰,比如增加信号线之间的间距、使用屏蔽技术、优化信号线的布局等。

因此,在高速PCB设计中,需要综合考虑蛇形走线和码间干扰等因素,通过合理的布线和技术手段,确保信号的传输质量和可靠性。

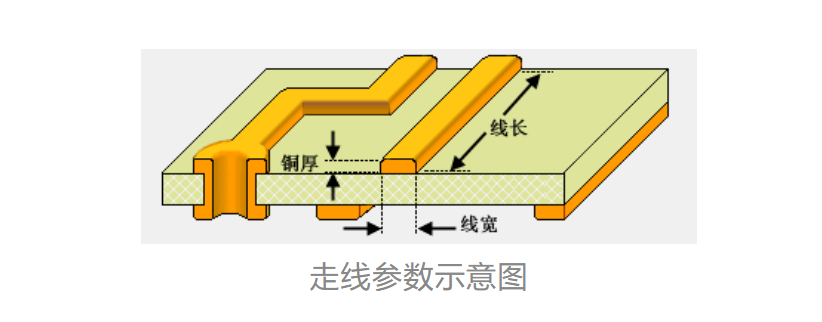

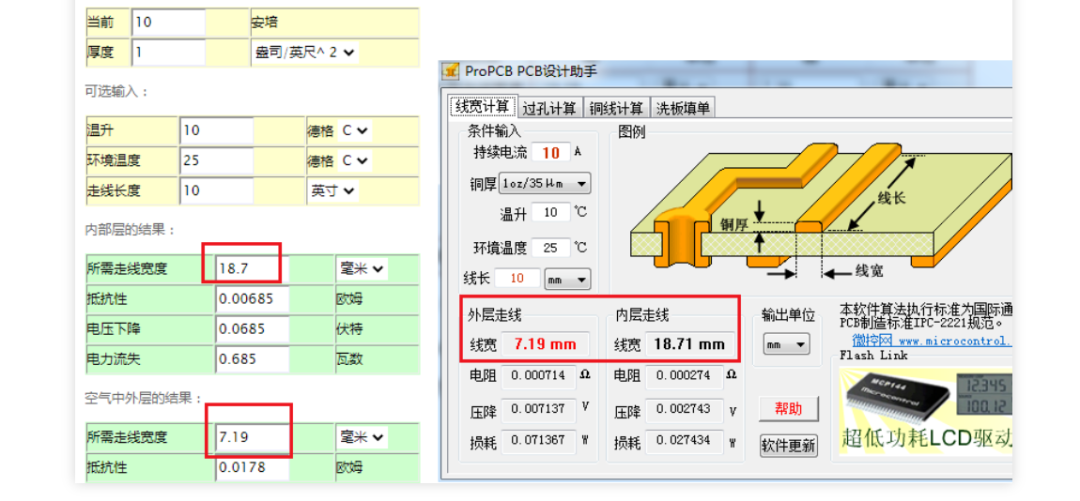

蛇形走线的作用一般是用来匹配长度和延时,若是滥用将带来线间耦合、传输延时延长、阻抗改变等问题。

平行区域的间距至少为3-4H,这样可以使平衡区域间的耦合最小化;

尽量使弯曲的长度最小化,这样做的好处是是可以减少耦合的总幅度;

与微带线相比,带状线和埋层微带线影响最小;

时钟信号尽量不要进行弯曲绕线,若需要绕线,尽量满足上面的规则。

当信号沿传输线传播时,总存在由反射、串扰、或其他噪声源引起的噪声,浙西噪声将影响发送到传输线上的信号,降低时序容限和信号完整性容限,这个现象称之为码间干扰ISI。

通过消除阻抗不连续,并使走线分支长度和较大的寄生效应(源自封装、插槽、或连接器)最小化,使得总线上的反射为最小;

使互联通道尽可能短。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论