凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片20天PCB设计与DFM的PCB设计作业--贺远

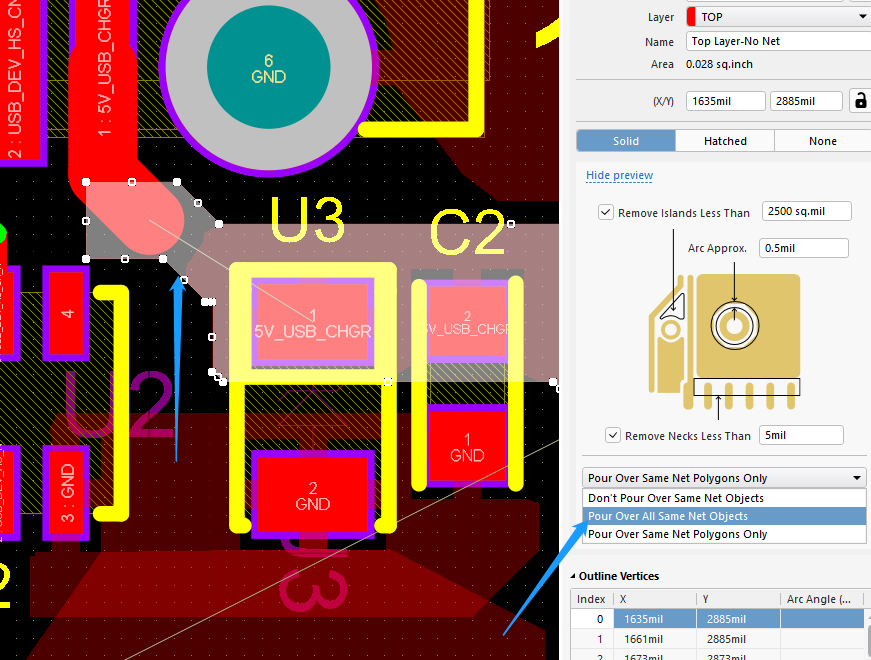

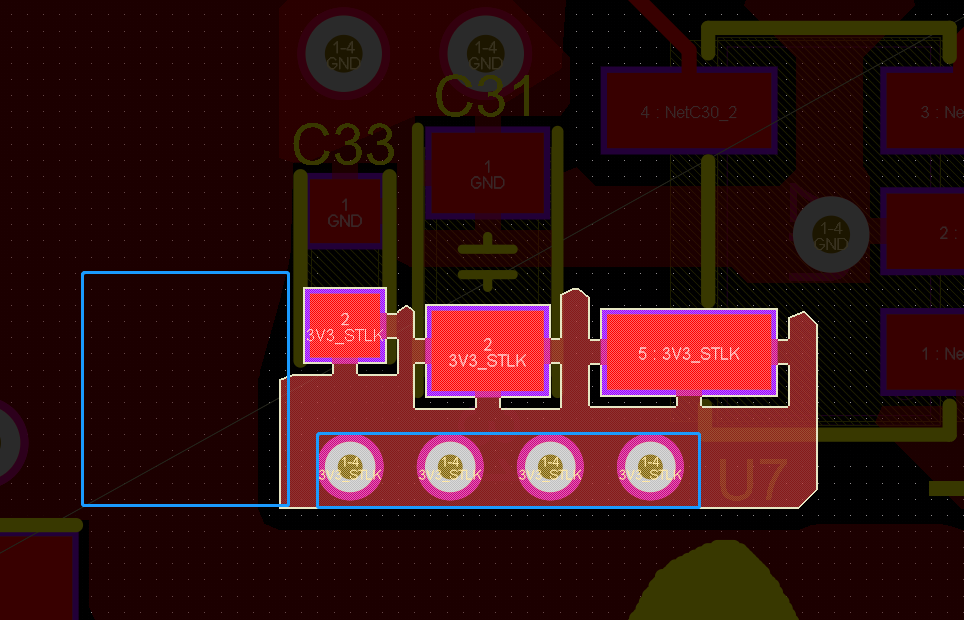

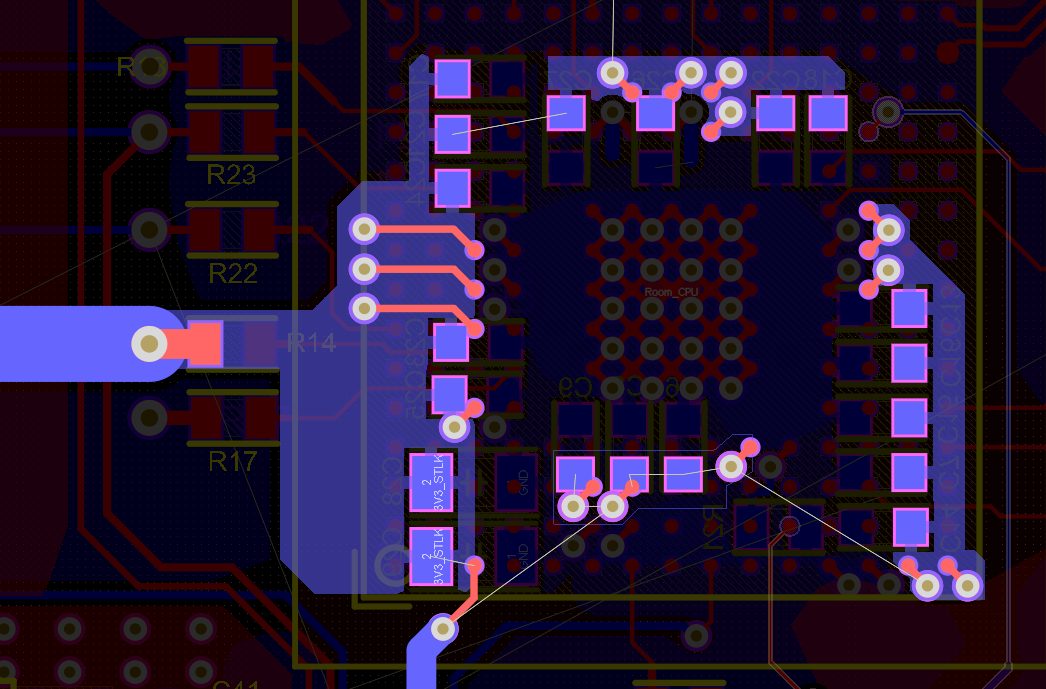

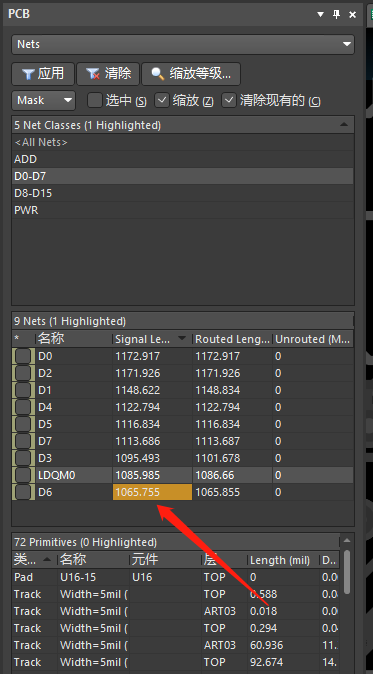

相同网络的铜皮没有连接在一起,后期自己修改一下铜皮设置,重启铺铜

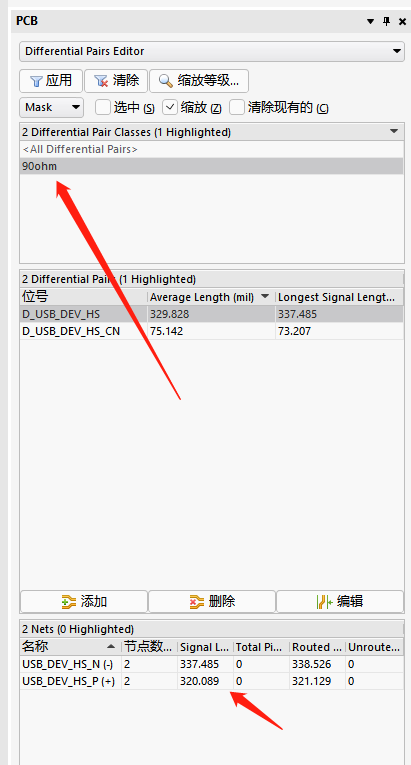

2.USB差分需要进行对内等长,误差5mil

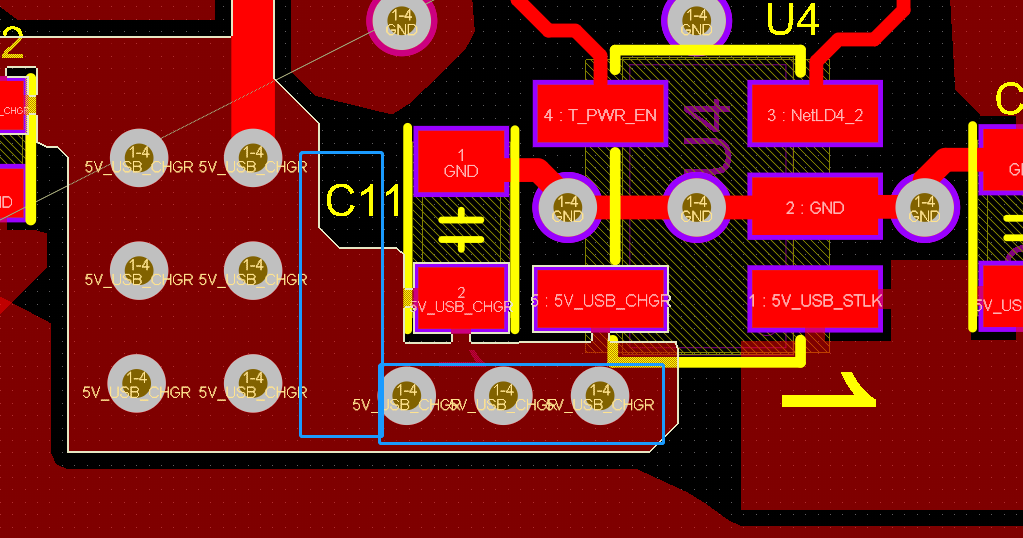

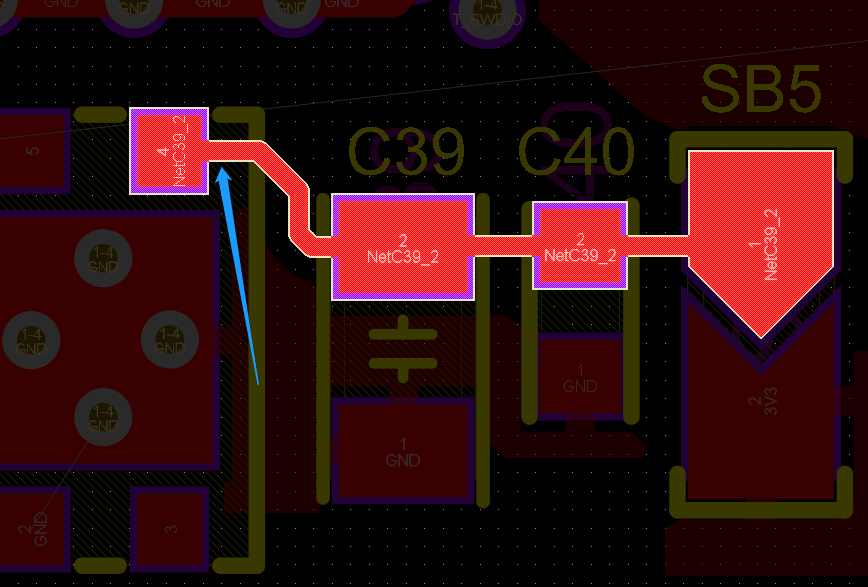

3.输入的过孔要打在电容的前面

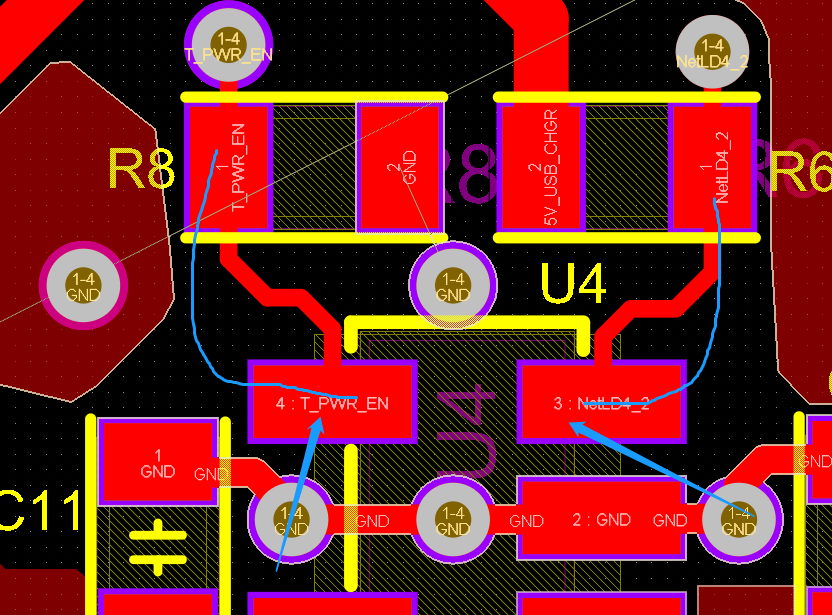

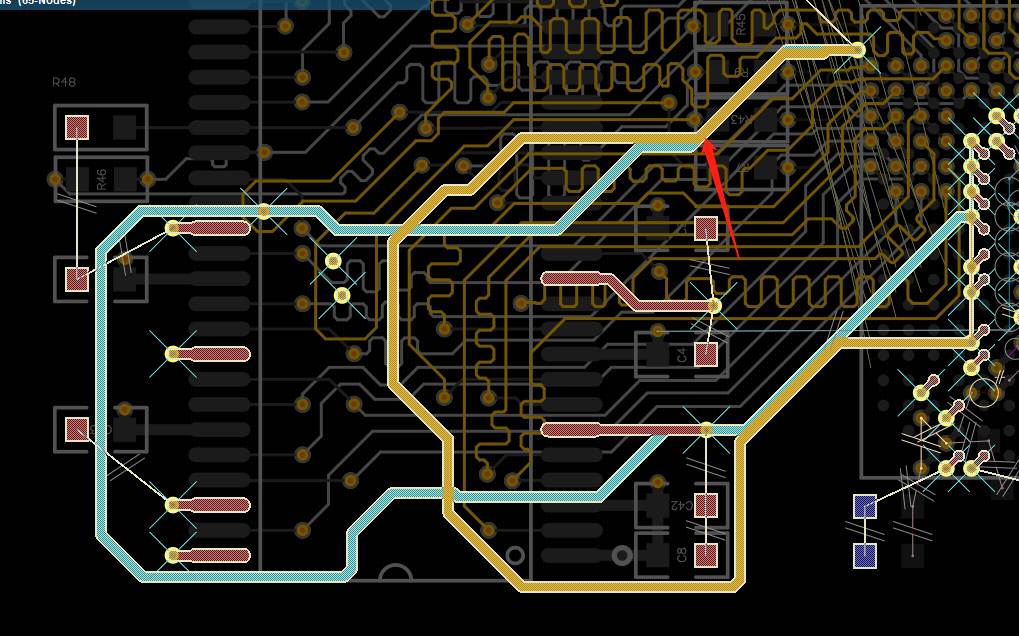

4.此处铜皮会出线载流瓶颈,自己在此处放置一块填充扩大载流路径

5.输出过孔要打在最后一个电容的后面

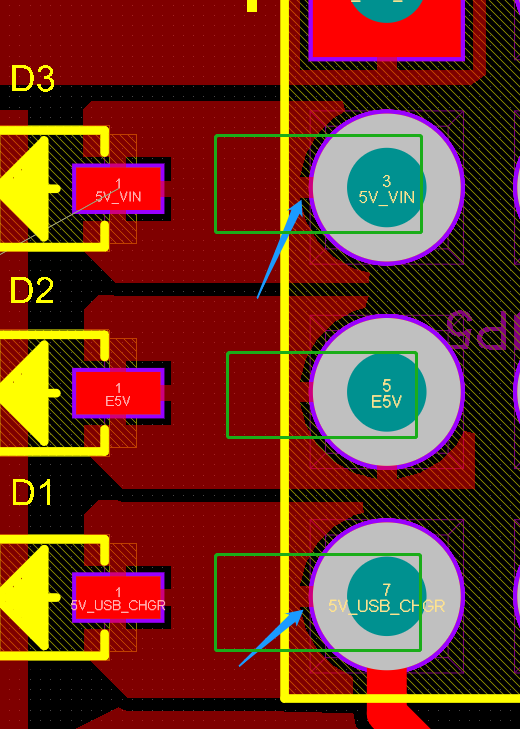

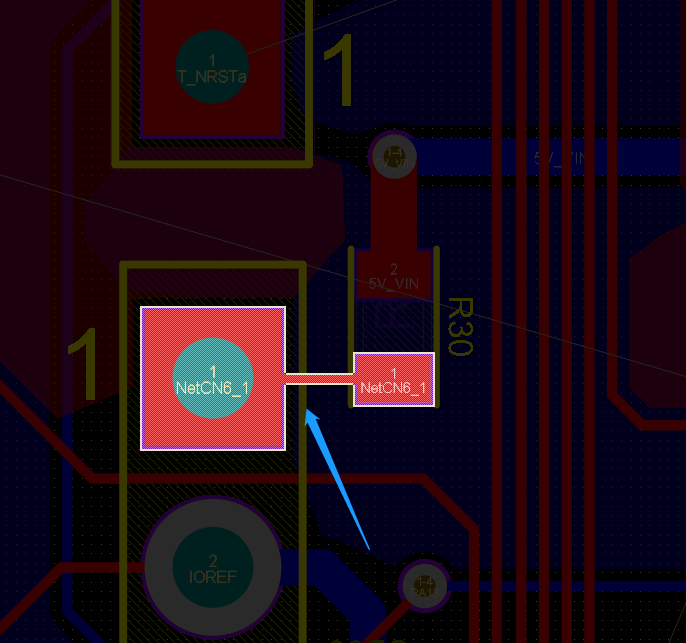

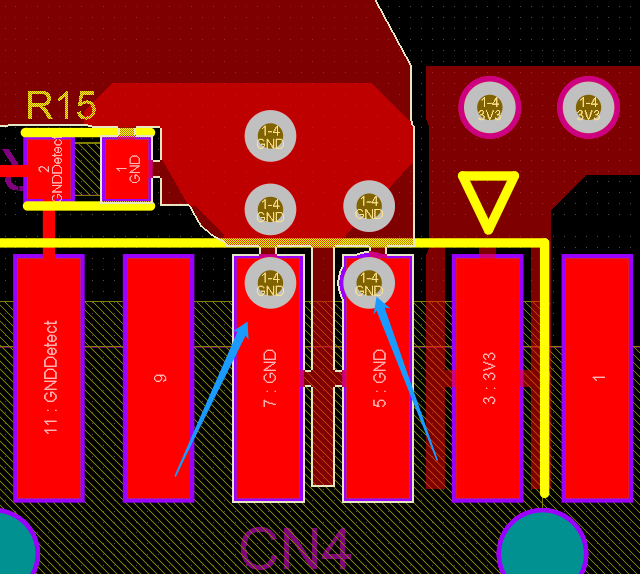

6.焊盘出线需要再进行一下优化,尽量从长边出线

7.电源输出路径不满足载流,尽量铺铜处理

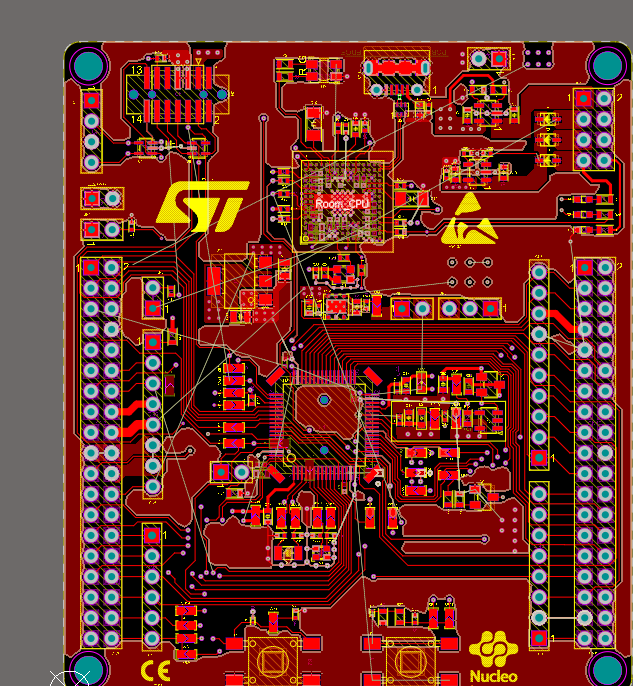

多处电源存在不满足载流情况,还有输入输出打孔的问题,后期自己对应检查,修改一下

8.VREFP电源走线需要加粗处理,拉出焊盘在进行加粗

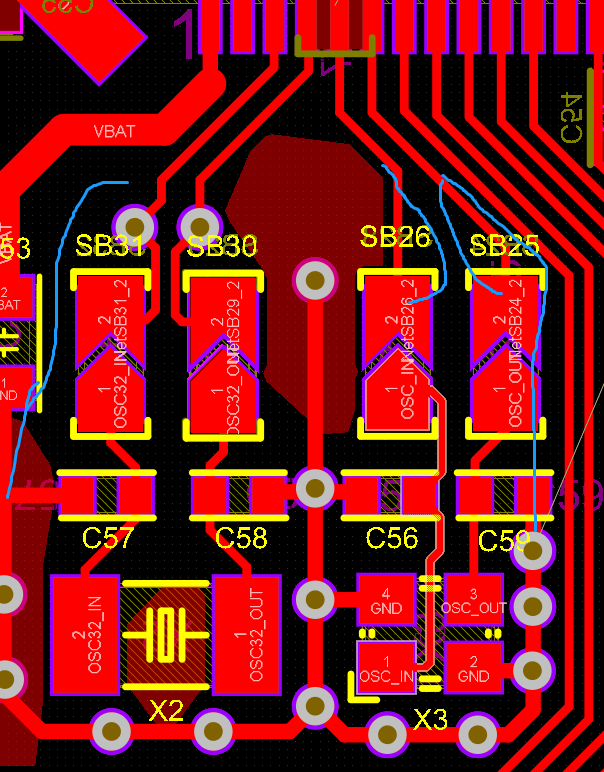

9.晶振走内差分需要再优化一下,包地尽量包完整

10.pcb上存在很多开路,后期自己处理一下

11.注意过孔不要上焊盘

12.电容放置尽量靠近管脚放置,尽量保证一个管脚一个

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论