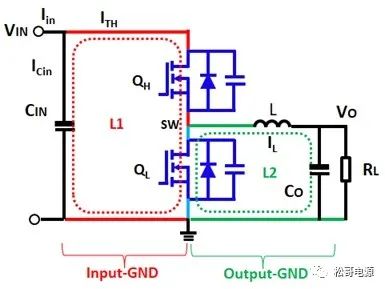

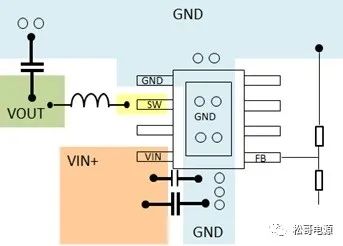

1、BUCK变换器关键回路和关键节点

不管是什么类型的变换器,PCB布局设计的关键就是要找到电路系统的关键回路和关键节点,那么什么是电路系统的关键回路和关键节点?通常,电流变化率di/dt大的环路以及电压变化率dV/dt大的节点,就是关键回路和关键节点,在PCB布局设计的时候,要优先考虑和布局。

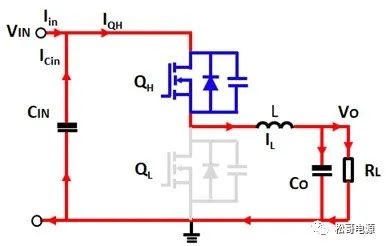

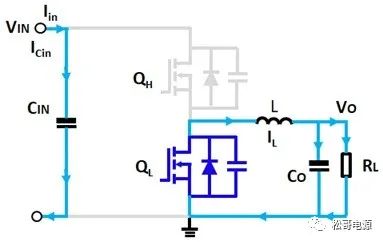

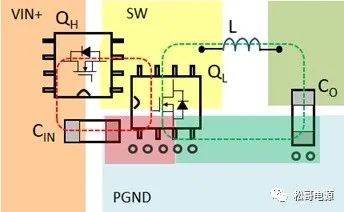

BUCK变换器上管开通以及关断时,各环路的电流及波形如图1所示。

(a)上管开通的电流回路

(b)上管关断的电流回路

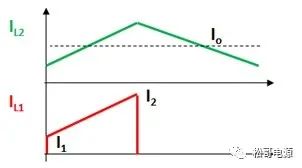

(c)L1和L2环路的电流波形

(d)开关节点SW工作电压

(e)BUCK的工作电流环路

图1:BUCK的工作电流环路及波形

如果把L1称为输入回路,L2称为输出回路;下管的S源极到输入电容的地,称为输入地,下管的S源极到输出入电容的地,称为输出地,可以发现:

(1)L1回路的电流、包括输入地,都是脉冲的电流波形,电流波形的前沿和后沿,具有非常大的电流变化率di/dt。

(2)L2回路的电流、包括输出地,相当于直流电流上面,叠加了峰峰值比较小的交流三角波,电流波形的前沿和后沿,具有较小的电流变化率di/dt。

因此,具有非常大的电流变化率di/dt的输入回路,也就是L1回路,包括输入地,是强磁场发射的干扰源。

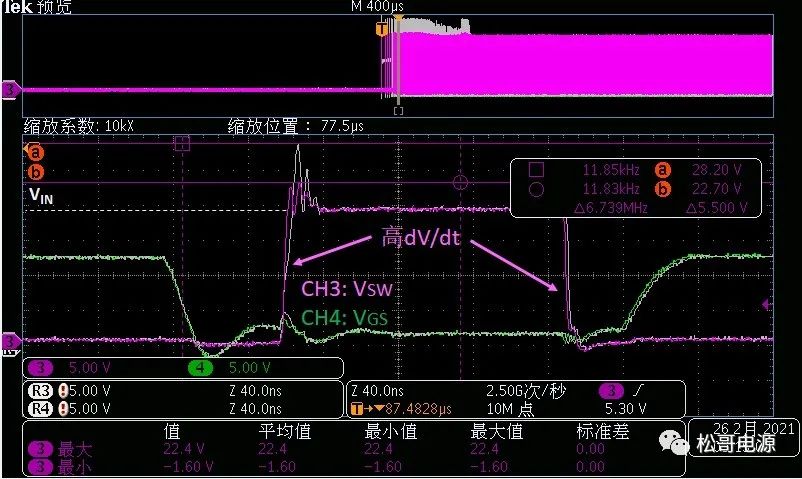

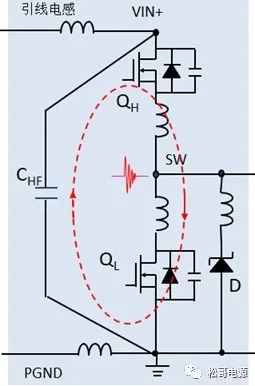

如果查看电压的波形,输入电压、输出电压及地回路,都是稳定的电压,而开关节点SW的电压,在上管开通和关断的过程中,产生非常大的电压变化率dV/dt,是强电场发射的干扰源。

2、BUCK变换器PCB基本的设计和布局要求

根据BUCK变换器的工作原理、各个回路的电流特性以及开关节点的电压特性,就很容易的得到BUCK变换器PCB布局的基本原则:

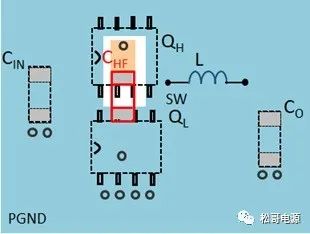

(1)输入回路L1,包括输入地,回路要尽可能的短,也就是输入电容CIN的正端尽可能靠近上管的漏极D、输入电容CIN的地端尽可能靠近下管的源极S,回路的布线要尽可能的粗,从而减小环路的寄生电感,减小磁场干扰。

必要的时候,在上管的漏极D和下管的源极S之间最近的距离,放置一个小尺寸的去耦陶瓷电容。

输入回路尽可能短、布线粗,可以减小杂散电阻,减小其导通损耗,有利于散热。

(2)输出回路L2,包括输出地,磁场干扰不大,但是,输出电流通常比较大,要尽可能减小环路,布线尽可能的粗,减小杂散电阻,减小其导通损耗,也有利于散热,可以提高系统的效率。在一定的程度上,也可以减小磁场干扰。

(3)开关节点SW的面积要尽可能的小,从而减小节点的寄生电容,减小电场干扰。但是,这个节点要铺设铜皮,加强功率MOSFET的散热,因此,要在散热和EMI(电场发射干扰)的设计之间取得平衡,必要的时候,需要加吸收电路,减小电压变化率。

其他的注意事项还有:

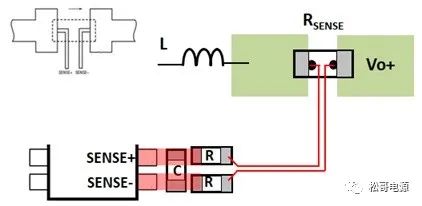

(4)所有的反馈信号以及模拟小信号,要远离上面干扰大的回路和节点,并尽可能用较细的布线。控制IC或变换器的下面不要流过开关电流。电流取样信号要采用开尔文Kevin的连接方式,电流取样信号的RC滤波网络,要尽可能靠近IC的管脚。

图2:电流取样信号

(5)输入和输出电容的地,通过多个过孔连接到底层或内层的地平面,如果器件底部有电气特性为地的铜皮,也可以通过多个过孔连接到底层或内层的地平面,加强散热。

(6)DC电源和DC地,相当于交流地,可以屏蔽干扰信号,因此尽可能不要做分割。如果分割不可避免,尽可能减小信号线的数量和长度,小信号尽可能和大信号平面用交流地进行隔离。

(7)功率MOSFET的栅极Gate驱动环路要尽可能短,并使用平行走线。功率MOSFET的源极D和漏极S,尽可能用铜皮布线,如图3所示。

(a) 好的布线 (b) 不好布线

图3:功率MOSFET的布线

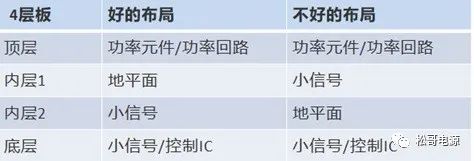

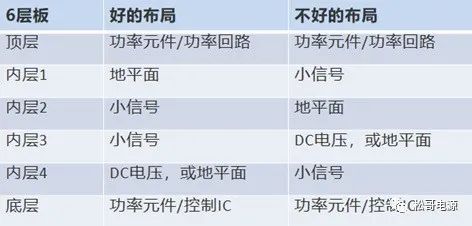

(8)2层板的电源系统,顶层为元件和功率回路层,底层为小信号和地平面层。4层或6层板,可以采用下面的方案。

表1:4层板各层分配

表2:6层板各层分配

3、BUCK变换器PCB设计布局实例

3.1 分立方案

上管、下管采用分立功率MOSFET,上管、下管常用的排布有二种布局:

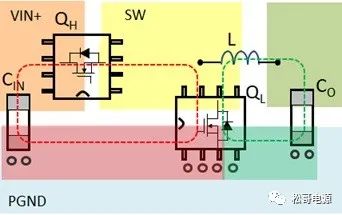

(1)上管、下管一个水平,一个垂直,成90度,如图4示;

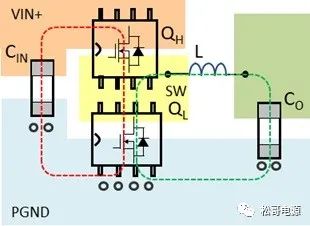

(2)上管、下管水平排列,如图5所示。

基本的原则是:先布局主功率回路,特别是输入电容、功率MOSFET回路,然后布局电感和输出电容回路,考虑功率地、小信号地的分区;最后,在小信号地一侧,布局相关的信号线。

(a) 优化布局

(b) 较差布局

图4:垂直排列分立器件BUCK布局

图4中的二种布局,图4(a)的输入环路以及输入地,比图4(b)要小很多,因此,图4(a)布局更优化。

(a) 顶层布局

(b) 高频电容

(c) 高频电容放置背面底层

图5:水平排列分立器件BUCK布局

图5的布局中,Cin距离较远,输入环路以及输入地比较大,但是这种布局适合多管并联,可以通过在PCB背面加高频滤波电容,减小BUCK电路的电流环路。

3.2 集成方案

集成方案是指集成上管和下管的BUCK变换器IC,下面这些设计来源于一些厂家器件数据表推荐的布局,以及一些客户工程师实际的设计。

基本的原则和上面相同:先布局主功率回路,特别是输入电容、IC的地回路,然后布局输出电容,考虑功率地、小信号地的分区;最后,在小信号地一侧,布局相关的信号线。

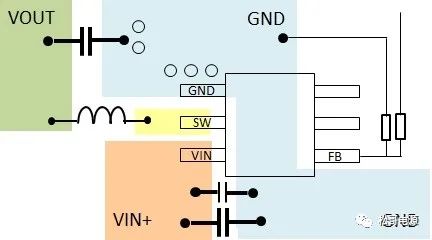

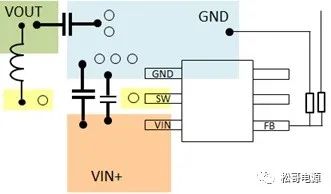

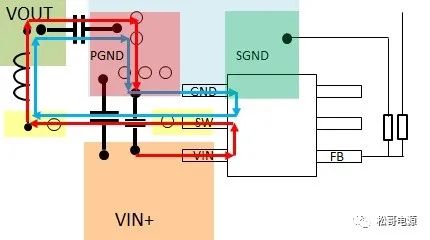

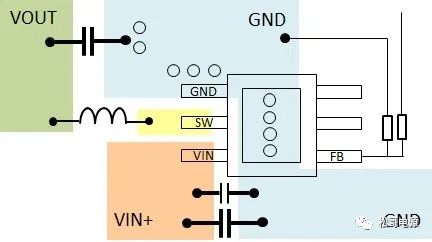

(a) 布局1

(b) 布局2

(c) 布局3

图6:SOT23几种PCB布局

按图4的分析方法,分别画出图6中上管开通、关断的电流路径,可以发现:

(1)图6(a)的电流路径要穿过IC底部,回到下面输入电容的地,电流路径较长,功率地(IC的GND管脚左上角区域)、小信号地(IC的GND管脚右边区域)也做到严格分区,优点是:开关节点SW在顶层直接连接到电感。

(2)图6(b)的电流路径最短,功率地(IC的GND管脚左上角区域PGND)、小信号地(IC的GND管脚右边区域SGND)严格分区,如图7所示,缺点是:开关节点SW要通过过孔,连接到电感。

图7:SOT23布局2电流路径

(3)图6(c )中,IC右边管脚附近元件、连接到BOOT管脚的一个电阻和一个电容,让输出电容的地,不能直接回到IC的GND管脚,输出电容的地和IC的GND管脚的连接有二个回路:一个是通过IC底部的过孔、输出电容的地附近过孔,和底层的地平面,形成连接回路;另一个是输出电容的地,通过顶层铜皮,从IC下方绕回到IC的GND管脚以及输入电容的地。

这种布局设计电流路径最长,功率地、小信号地没有分区,开关节点SW要通过过孔,连接到电感,因此,布局设计比较差。

SOT23器件底部有电气特性为地的铜皮,在PCB对应的焊盘上,可以布设多个过孔,连接到底层或内层的地平面,加强散热,如图8所示,在许可的条件下,尽可能多布设过孔,过孔直径要选择合适,保证焊接后,既不漏锡,锡也要填满过孔。

图8:下部有铜皮SOT23 PCB布局

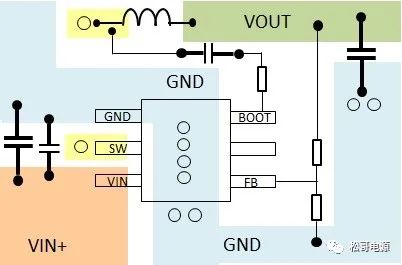

图9列出了SO8封装的几种PCB设计布局,有兴趣的可以按照上面的方法,分析一下它们的优缺点。

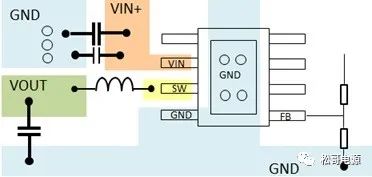

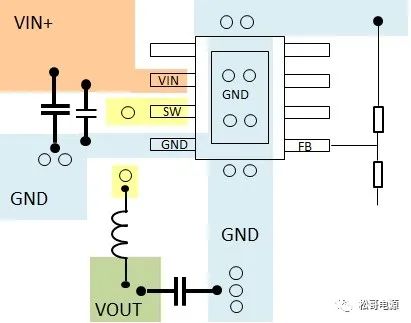

(a) 布局1

(b) 布局2

(c) 布局3

图9:下部有铜皮SO8几种PCB布局

暂无评论