本节讲一下硬件系统中常用的滤波电路,主要包括芯片的滤波电路,一些模拟芯片的滤波电路,模拟电路的滤波电路。

基本上是项目中遇到的一些实际情况。

SoC常用的滤波电路有这么几类:储能电容,旁路电容,RC滤波,LC滤波,pi型滤波等。

储能电容

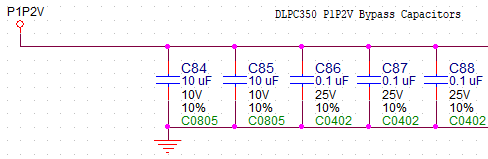

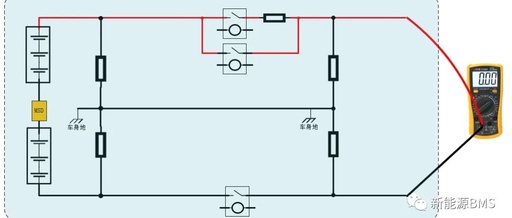

下图2个10uF的电容就是储能电容。

一般电路系统中的电源输出端是DCDC或者LDO,那么从电源输出端到用电器件/SoC管脚还会有一段不短的距离,而储能电容都是靠近用电器件/SoC管脚摆放。否则的话,过长的供电路径会造成电量抽载时供电不稳。

储能电容的大小,主要依赖于用电消耗,不同的用电器件需求不同,要根据规格书/设计指导/参考电路来选择。

深入到芯片内部来说,主要是动态消耗部分所决定的,这个和电路原理(IP核),制程工艺都相关,一般来说,IP复杂度越高,芯片制程工艺越落后,动态功耗就会越大。

储能电容的数量,一般要求SoC的每个功能块至少一个,不同的功能块之间最好不要共用。

储能电容的容值选择,从100~470UF的电解电容,到22uF,10uF,2.2uF,1uF的陶瓷电容都会出现。

一般是沿用参考设计的,而参考设计则是从芯片模型电源完整性仿真,实际测试最终形成的——这部分一般来说只有SoC厂商有能力做,甚至很多也没有仿真能力。而下游的产品研发/生产商没有这个能力,所以很难做改动。

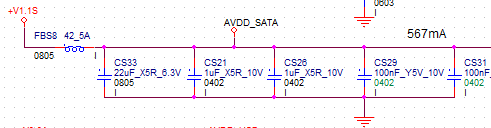

下图是TI的某投影SoC所用

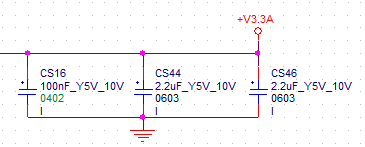

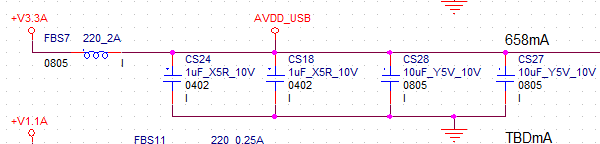

下面两图是英特尔的某笔电平台所用(22uF,2.2uF,1uF)

如果参考设计用的储能电容比较多,实际产品中由于PCB面积受限等,无法实现,必须缩减的情况下,缩减到多少为好呢?

严格来说,这要通过电源仿真来确认。但是,一般情况下芯片模型数据,公司技术能力等都有限,没办法去做这样的仿真,主要是依据经验和产品实测决定。

迫于成本/体积压力等,必须减少的情况下,那么可以根据实际测量情况来修改,即测量各种工作模式/负载情况下,纹波的频率,依据这些数据来设计。思路上有两种,一是逐步减少,即逐个减少后看测量数据;二是根据经验一次性减少若干个之后,再根据测量数据加回来一些。保障电源纹波不超过芯片要求的情况下,最终形成一种方案。

由于测量不充分(很难模拟到所有工作模式/可能性等),修改是比较容易产生问题的。笔者曾做过的一款安防产品(DVR)就遇到过这样的问题,原厂参考设计是6层PCB,且储能电容比较丰富,而实际产品所用的PCB是4层板,储能电容也缩减了一些,导致出现了老化过程中死机的问题,最终在SoC的core电源上增加了一颗22uF的储能电容才解决。

旁路电容

上图中0.1uF的几个电容就是旁路电容;

芯片一般要求每个管脚旁边放置一颗。如果SoC管脚比较紧密,无法保障每个管脚旁边放置一颗的话,可以适当减少,比如2~3个管脚共用一颗,距离要靠近,不能太远。或者2~5个管脚共用2可旁路电容。

LC滤波

LC滤波在SoC的需求,一般是磁珠+电容的方式,不是电感+电容的方式。

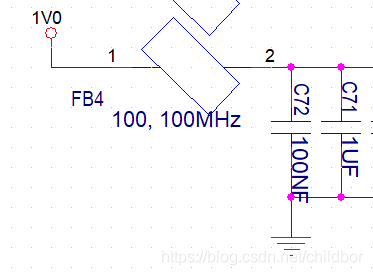

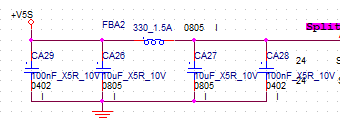

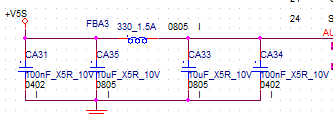

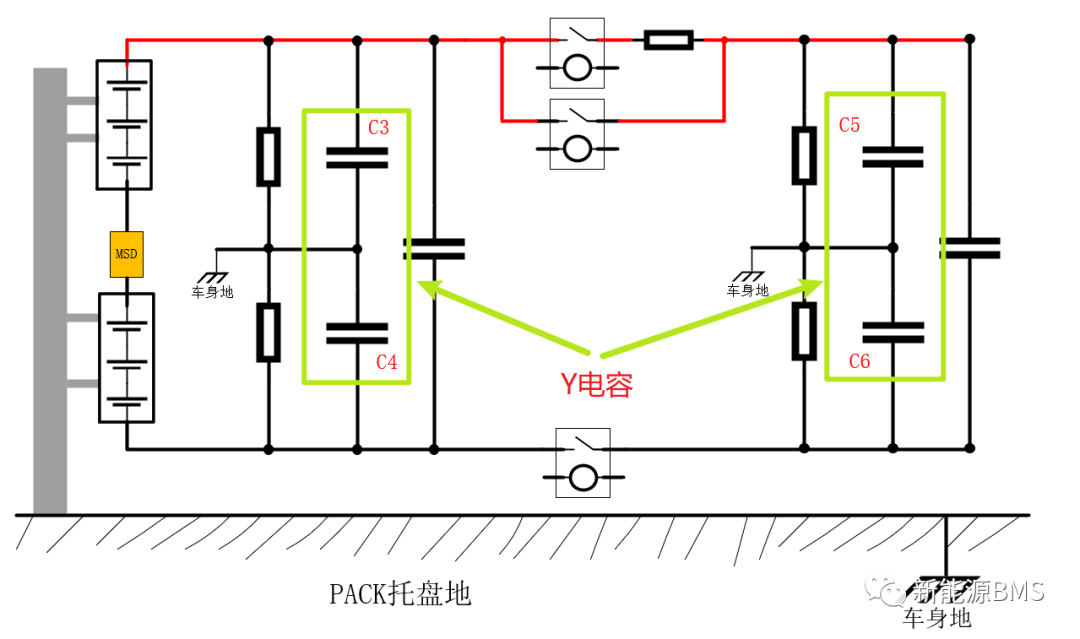

比如下图,就是海思3521芯片的PLL部分的参考电路。可以看到,是用100R/100MHz磁珠+1uF+0.1uF的电容构成。

通常,LC滤波用于一些要求略高的功能模块,模拟部分,PLL部分等。纯数字部分一般用储能电容+旁路电容的方式就能满足需求。

下图是海思3521芯片的PLL部分

下面两图是英特尔的某笔电平台所用(22uF,2.2uF,1uF)

pi型滤波

pi型滤波是SoC对电源要求更高的情况下才会使用的。

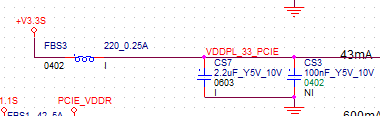

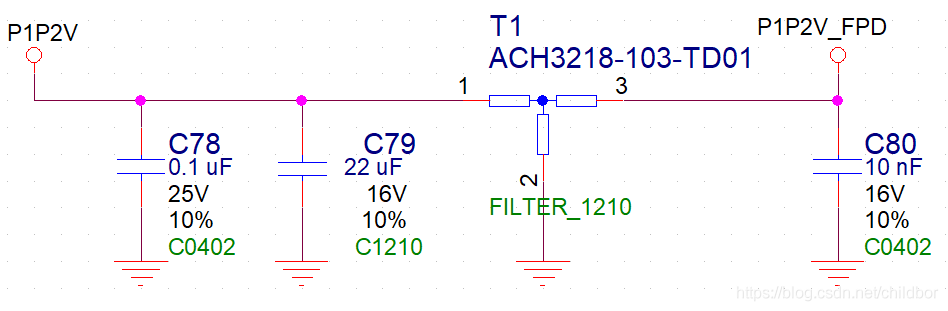

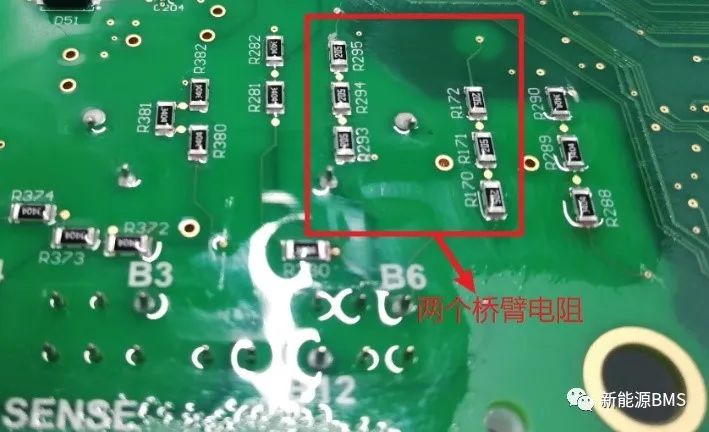

下图是英特尔某笔电平台的Audio Codec所用;

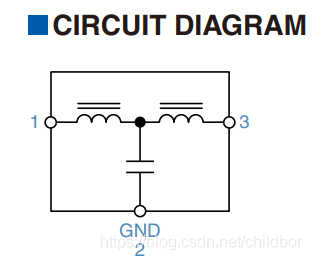

如果要求更高的话,还会用到三端滤波器,如下图所示。

RC滤波

RC滤波一般用的比较少,实在没办法才会用到。一般是用个几欧姆的电阻,比如5.1欧姆,后面是储能电容和旁路电容。一般来说,SoC工作的情况下,等效电阻也就是几欧姆,到十几欧姆,所以这种LC滤波虽然能有效减小纹波,但是也会容易导致压降比较大,芯片无法工作。

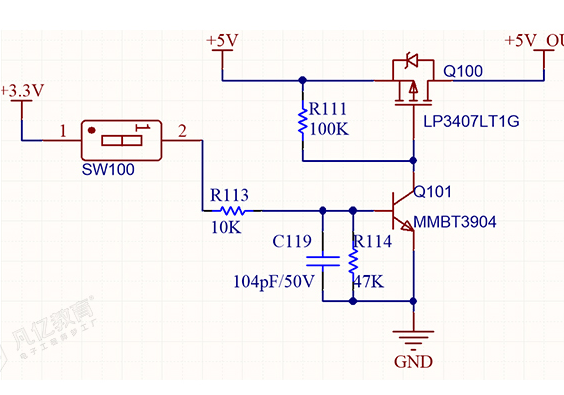

下图是英特尔某笔电平台所用,此处是0R,根据情况会做调整,一般不超过5.1R。

暂无评论