网上有很多的关于运放恒流源电路设计的电路,也都非常经典,目前实际项目中用到了这个经典的电路,还是记录一下经验心得和大家一起分享一下吧!

运放大家都不会陌生了吧,模拟电子中一个神一样存在的器件,可放大电压,可采样电流,电流采样又可以分为高端采样和低端采样,当然各有利弊,具体情况需要在实际电路中进行取舍,适合自己设计电路的才是最好的,没有完美的电路,所有的设计都是在性能和成本之间做出取舍,亦如人生都是在取舍之间,呃......有点扯远了,话归正题还是看看运放恒流源电路在实际应用中的操作吧。

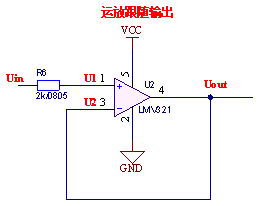

运放恒流源电路的由来我个人认为是由运放跟随输出演变而来的,我们可以先看一下运放跟随电路,如下图一示,这个就是运放跟随输出电路

图 一

运放理想放大倍数10万倍,供电电压一般是3V或者5V,运放放大的是输入信号的压差,放大10万倍的话,只能说明输入信号的压差非常接近,近似相等,我们称之为虚短。

因为运放的输入内阻无穷大,外接电阻上的电流非常小近似为0,所以运放输入端可以看做断开,称为虚断。

根据运放两大特性:虚断可知Uin=U1,因为运放内部输入阻抗可以认为是非常大,外面的2K电阻在它面前可以忽略不计(因为内阻不在一个量级上),因此可以认为运放1脚与运放内部是断开的,但是实际上是没有断开的。

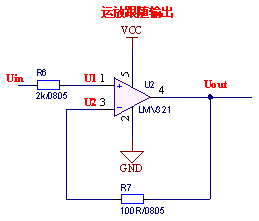

虚短:可以认为运放两个输入引脚是短接的,近似相等,可以得出U1=U2,那么有了Uin=U1=U2,Uout是不是和U2是相等的呀,所以得到Uin=Uout,称之为跟随,跟随电路的优点是带载能力增强,但是在实际应用中输出引脚不能直接和输入引脚直接相连,因为引脚直接相连会容易产生振荡,可能我们在实际设计过程中并没有发现问题,但是这并不代表问题不存在,所以在实际设计时候需要在输入和输出之间加一个R7电阻(如下图二),阻值不要太大,一般100R就可以,目的是破坏振荡条件。

图 二

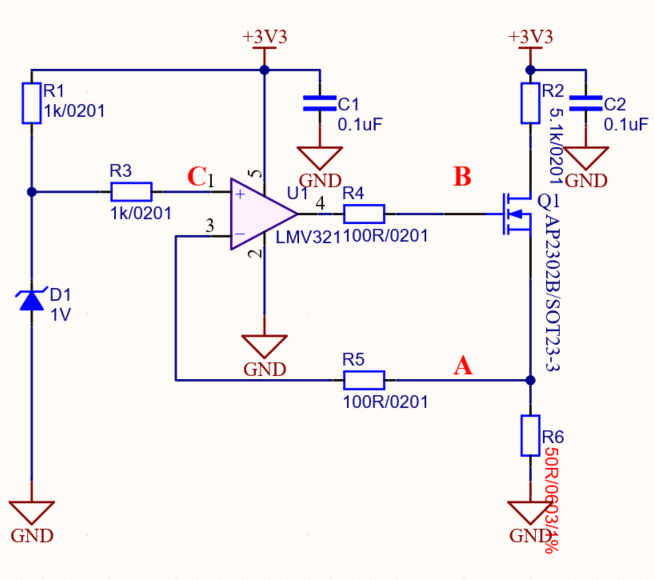

有了运放跟随电路的铺垫,我们一起来看下运放恒流电路图三示。

图 三

与运放跟随电路相比较增加了运放正输入端的输入电压,增加了后面的恒流负反馈电路。电路正常运行情况下C点电压等于1V,根据虚短特性A点电压等于C点电压等于1V,1V/50R=20mA,电路恒流为20mA,那这个电路目前可以正常工作吗?

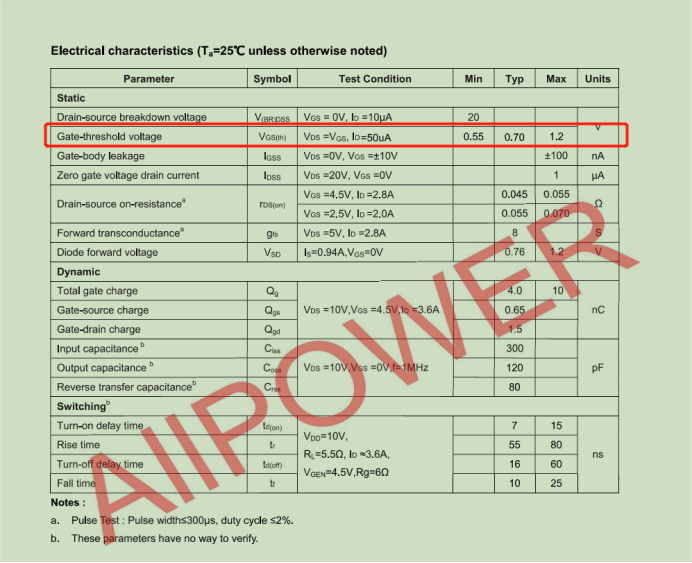

我们一起来分析一下:初始上电运放没有输出,Nmos管不通,A点电压为0V,随着开通时间延长,D1导通,C点电压逐渐建立,运放逐渐有输出电压B点电压什么时候达到Nmos管的Vgs导通阈值时,Nmos管才会导通,然后A点才会有电压,因为运放理想放大倍数是10万倍,所以要想运放输出稳定,需要C点电压等于A点电压,运用虚短概念。

当Vgs=0.55V时候Nmos管开始导通,此时Nmos管处于放大状态,假设此时A点电压等于C点等于1V,加上Vgs,那B=A+C=1V+0.55V=1.55V也就是说此时需要B点电压对地1.55V才能保证A点电压正常输出1V,但是实际上需要等到Vgs=0.7V时,A点的电压才能稳定到1V,也就是说需要B=1.7V才能稳定输出A=1V电压,且此时的运放供电电压要大于1.7+1V才能正常工作,否则A点无法正常输出1V,实战测试出来的效果,当A点输出1V时候电流恒定40mA,计算此时的Rdson乘上电流就是MOS管两端的压降,那负载供电电压减去A点和Vrdson上的电压即为负载两端的电压,Vr除以恒流电流,即为负载值。