1、模块整体布局时,WIFI模组要尽量远离DDR、HDMI、USB、LCD电路以及喇叭等易干扰模块或连接座;

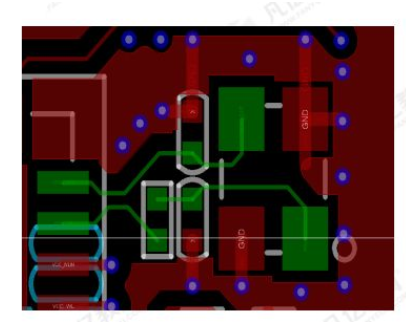

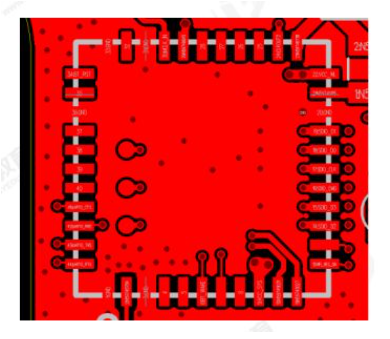

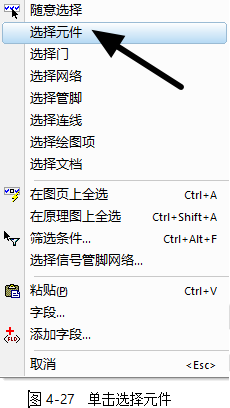

2、晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量天线区域;晶体以及时钟信号需要全程包地处理,包地线每隔100mil至少添加一个GND过孔,并且必须保证邻层的地参考面完整,如图1所示。

3、32.768k单独走线,并做包地处理,并且包地线每隔400mil,至少添加一个GND 过孔;

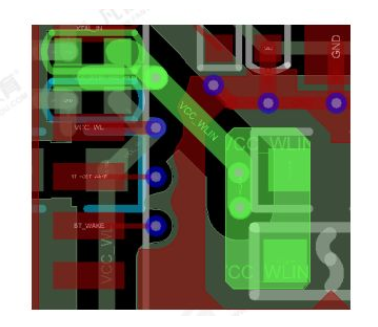

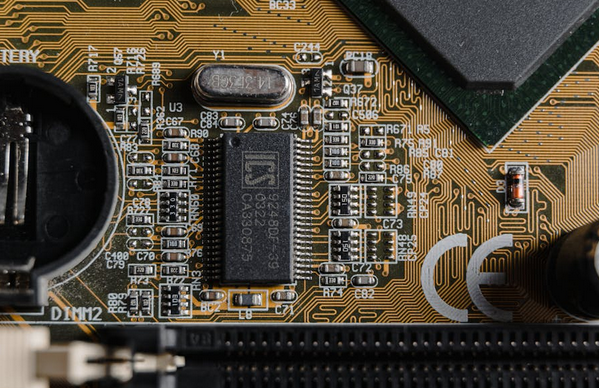

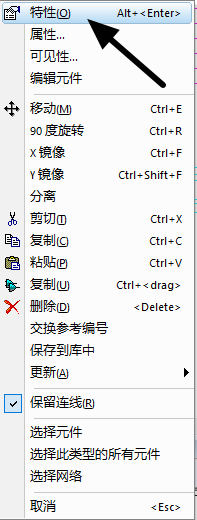

4、VBAT电源工作时电路较大,单天线模组600mA以上,整个供电主回路须20mil以上,接入管脚的走线跨度与PIN脚同宽,如需打孔至少两个过孔;VBAT的电源去耦电容必须靠近模组电源管脚,与旁边的晶体时钟走线用10mil左右的地线隔离,如图2所示。

图1 晶体的布局与布线

图2 VBAT去耦电容的放置

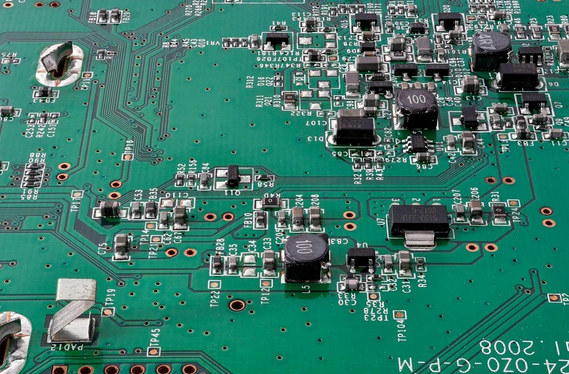

5、天线匹配电路必须靠近天线座,天线走线50欧姆(根据实际叠层情况可以做隔层参考),保证参考地的完整,下方不允许有其他信号线或电源;

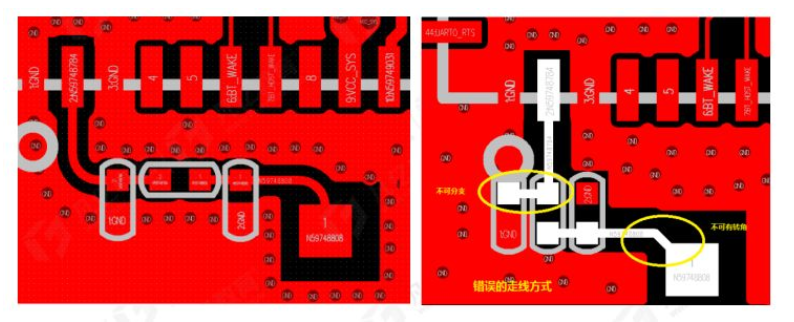

6、天线布线越长,能量损耗越大,因此在设计时,天线路径越短越好,不能有分支出现,尽量不换层;天线周围需要多打地过孔,天线走线有遇到需转向时,不可以用转角的方式,需用弧形走线。如图3所示。

图3 天线走线示意图

7、如果是2X2 MIMO天线接口,两个天线口之间的出线方向需要考虑两个天线的位置,两个天线的位置需要尽量远离避免干扰,并考虑垂直放置以避免互相干扰。

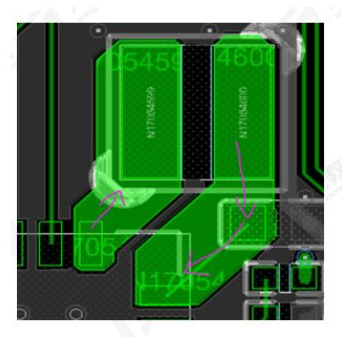

8、模组的电感布局时,请注意走线经电感出来后,先经过电容,再进入模组电源管脚,如图4所示。模组下方第一层保持完整的地,不要有其他信号走线,如图5。

图4 功率电感走线示意图

图5 功率电感走线示意图

9、SDIO_D0-D3、SDIO- CMD和SDIO_CLK 6根走线尽量要平行等长,走线长度相差控制在±25mil以内, 并且相邻层要远离其他电源和时钟走线,SDIO_CLK需要全程包地处理

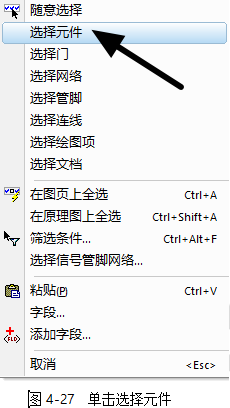

声明:本文凡亿教育原创文章,转载请注明来源!

暂无评论