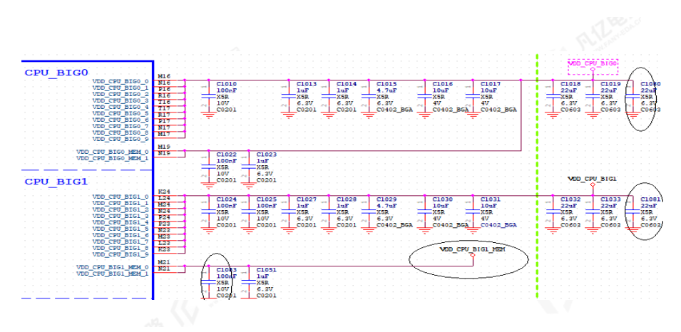

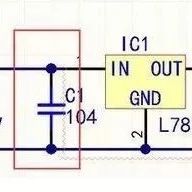

1、如图1所示的滤波电容,原理图上靠近 RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容GND PAD尽量靠近芯片中心的GND管脚放置,如图2所示。其余的去耦电容尽量摆放在3588芯片附近,而却需要摆放在电源分割来源的路径上。

图1 RK3588 芯片VDD_CPU_BIG0/1的原理图电源管脚去耦电容

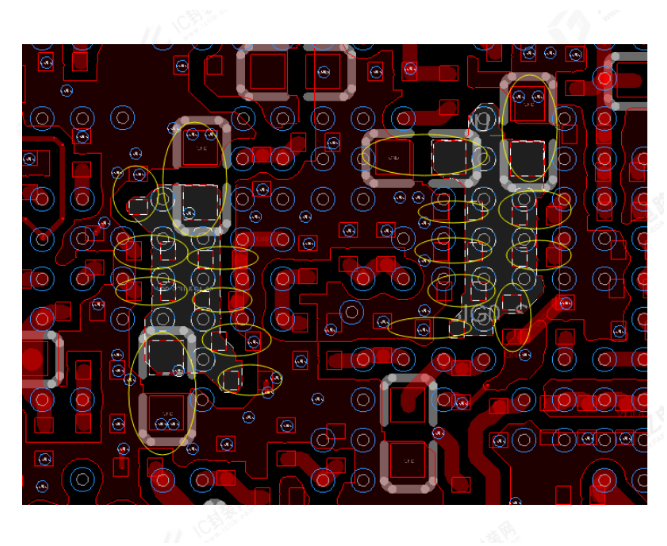

图2 芯片 VDD_CPU_BIG0/1的电源管脚背面去耦电容放置情况

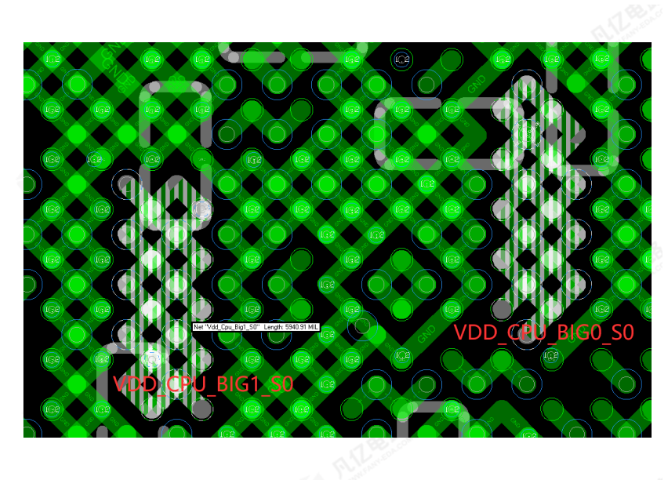

2、RK3588芯片VDD_CPU_BIG0/1的电源管脚,保证每个管脚边上都有一个对应的过孔,并且顶层走“井”字形,交叉连接,如图3所示,建议走线线宽10mil。

图3 RK3588 芯片 VDD_CPU_BIG0/1的电源管脚扇出走线情况

3、VDD_CPU_BIG0/1覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够;

4、VDD_CPU_BIG的电源在外围换层时,要尽可能的多打电源过孔12 个及以上0.5*0.3mm的过孔,降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用;

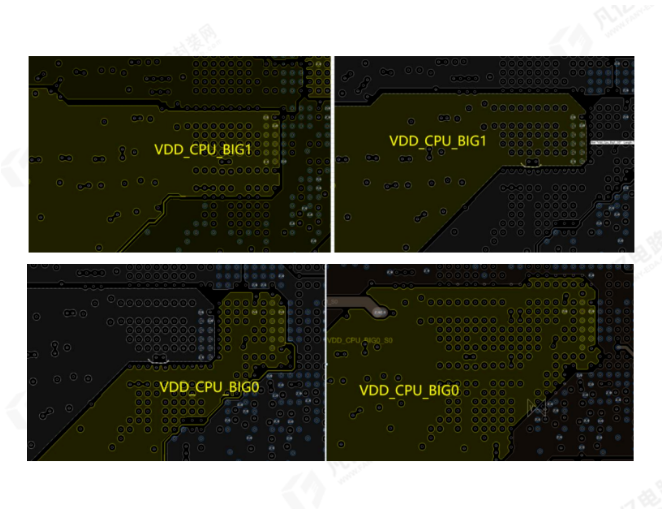

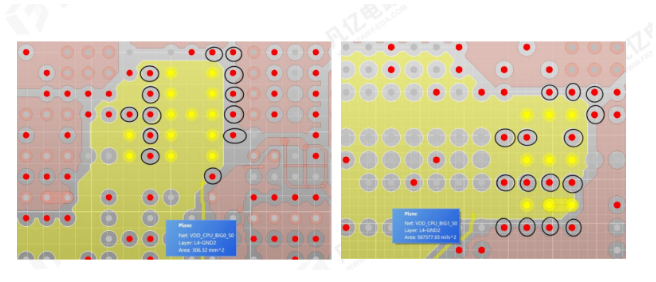

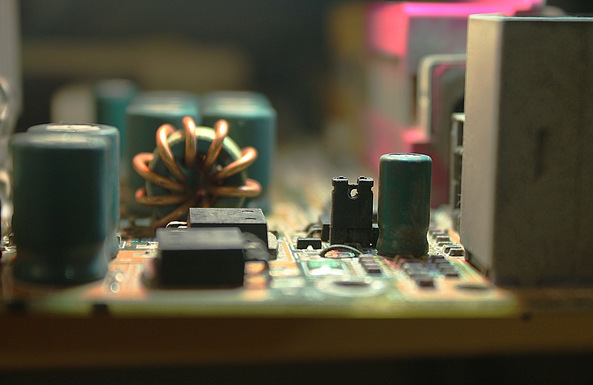

5、VDD_CPU_BIG电流比较大需要双层覆铜,VDD_CPU_BIG 电源在 CPU 区域线宽合计不得小于 300mil,外围区域宽度不小于 600mil,尽量采用覆铜方式,降低走线带来压降其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜,如图4所示。

图4 RK3588 芯片 VDD_CPU_BIG0/1电源层覆铜情况

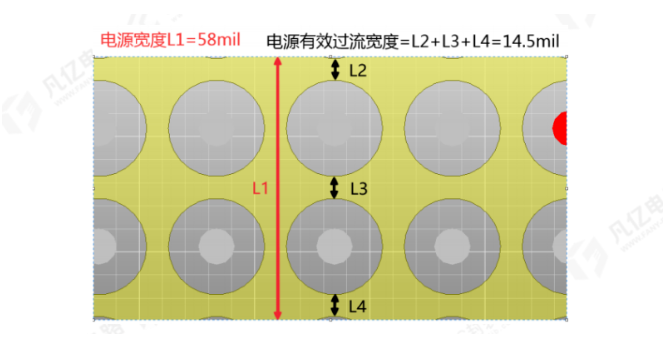

4、电源平面会被过孔反焊盘破坏,PCB设计时注意调整其他信号过孔的位置,使得电源的有效宽度满足要求。下图 L1 为电源铜皮宽度 58mil,由于过孔的反焊盘会破坏铜皮,导致实际有效过流宽度仅为L2+L3+L4=14.5mil,如图5所示。

图5 电源有效过流宽度示意图

7、BIG0/1电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧12个,如图6所示。

图6 BIG0/1电源地过孔放置图

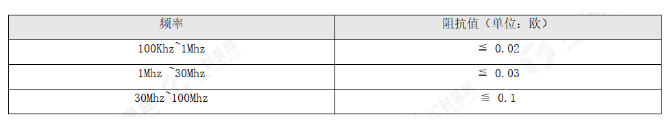

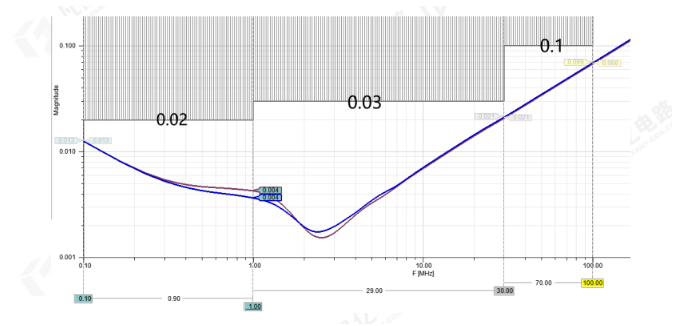

2、BIG电源PDN目标阻抗建议值如下表1所示和图7所示:

表1 BIG电源PDN目标阻抗建议值

图7 BIG电源建议PDN要求

声明:本文凡亿教育原创文章,转载请注明来源!

暂无评论