DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除反射是采用电阻并联的方式(还有很多种端接),今天我们一起来看一下在采用菊花链拓扑结构时,末端加匹配电阻和不加匹配电阻时信号的质量有多大的区别。

信号末端终端匹配电阻

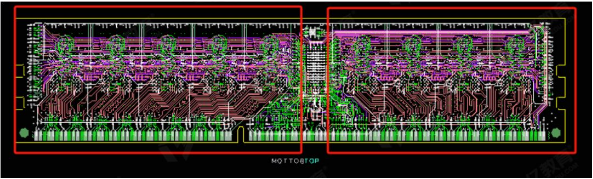

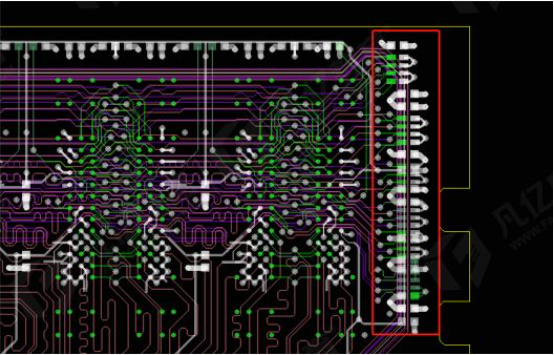

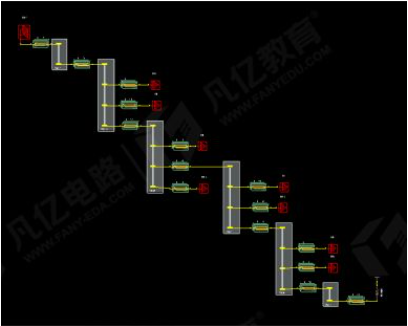

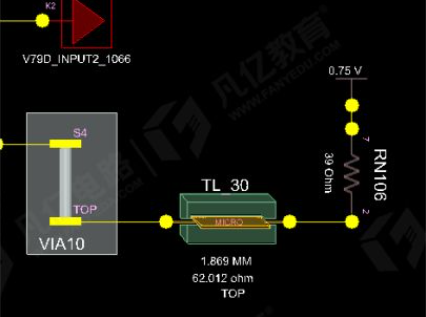

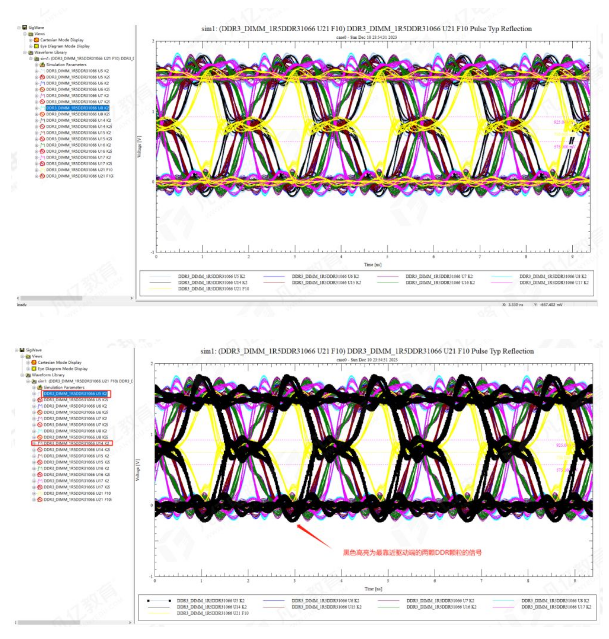

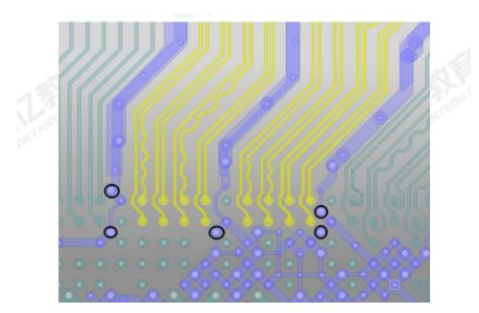

本次我们将从这个内存条PCB板中提取地址线拓扑以SigXplorer软件观察添加匹配电阻和不添加匹配电阻时信号的传输质量,本次案例为双通道DDR3一拖8正反贴菊花链拓扑结构,通过软件提取在经过我们整理之后的拓扑如下图所示

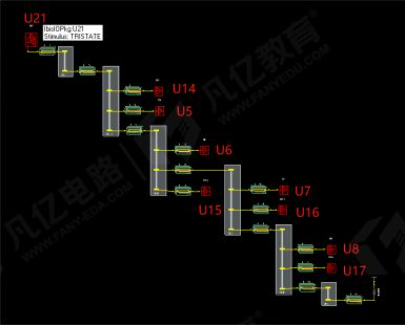

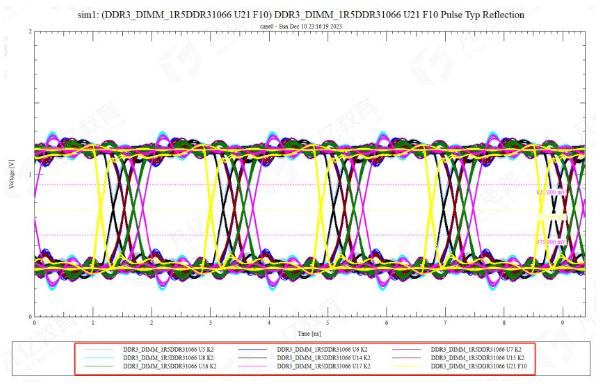

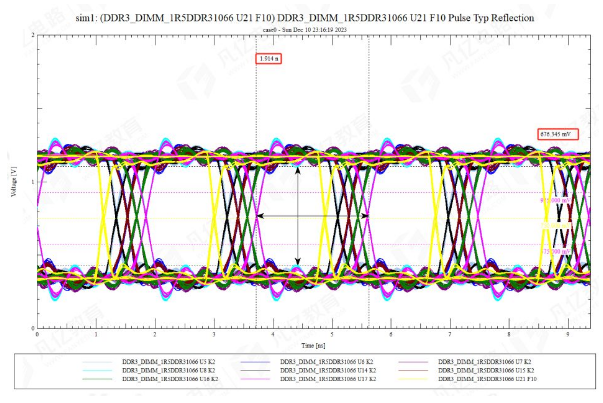

信号从驱动端U21开始传输,依次经过的DDR颗粒为U14和U5 U6和U15 U7和U16 U8和U17,最后接上39ohm终端匹配电阻RN106,我们提取了其中一根地址线A3,激励信号为533MHZ,观察他的眼图结果

以上为地址线A3的眼图情况,根据菊花链的信号流向我们可以分辨出最左边黄色信号为信号的驱动端,右边信号为8个DDR3颗粒的信号。

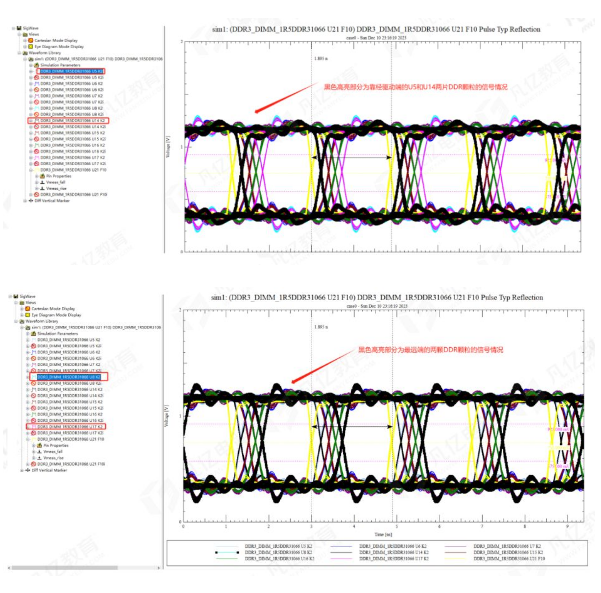

我们观察眼图结果会发现整体信号有效,可以很明显的观察到眼宽与眼高,在加了端接电阻之后,最靠近驱动端的两片DDR颗粒信号质量和靠近匹配电阻的两片DDR颗粒相对比会发现,靠近匹配电阻的两片DDR颗粒信号质量较差,过冲和下冲严重一些。但是信号质量合格没有出现跌破VIH和VIL的情况。

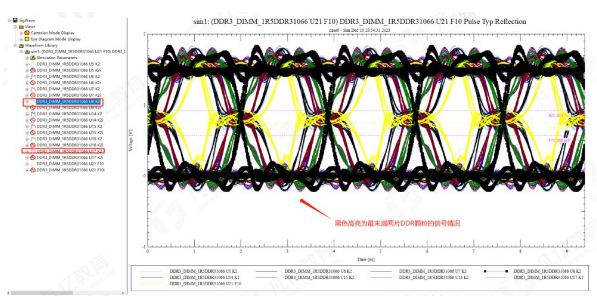

上图为不加端接电阻时的信号眼图结果,我们可以看到信号的眼宽与眼高非常的窄,信号的VIH和VIL过线之后保持时间短,信号质量差,我们再次观察了靠近驱动端的两个DDR颗粒的眼图结果和最末端的两颗DDR颗粒的眼图结果,我们会发现在不加端接电阻的时候眼图结果和加端接电阻的时候结果相反,靠近驱动端的两个DDR颗粒质量非常差,眼宽与眼高非常窄,然而最远端的两片DDR颗粒质量反而会好很多,虽然也有明显的上冲和下冲,但是眼宽和眼高相对来说比较清晰。

我们可以通过以上仿真结果分析出,在采用菊花链拓扑结构时,端接电阻是很有必要加的,端接电阻有非常明显的改善效果,但是需要注意的是,端接电阻务必要和传输线阻抗相匹配才可以达到最佳的改善能力。

声明:本文凡亿教育原创文章,转载请注明来源!

暂无评论