凡亿教育-乐乐

凡事用心,一起进步打开APP

公司名片DDR终端匹配电阻的长度多少合适?

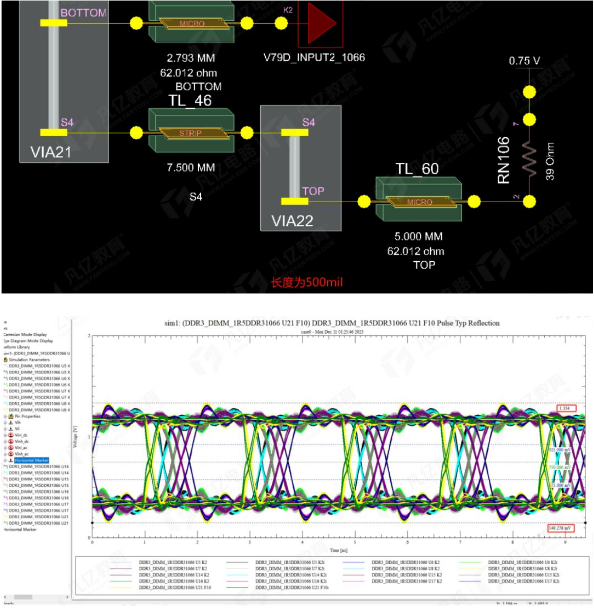

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。

本次采用的案例依旧是我们上期的DDR3一拖八正反贴菊花链拓扑结构。

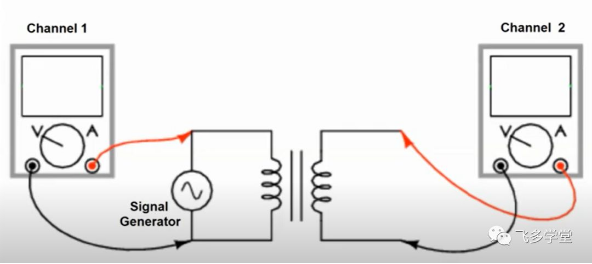

我们还是用同样的方法提取出根地址线A3的拓扑,激励信号为533MHZ.

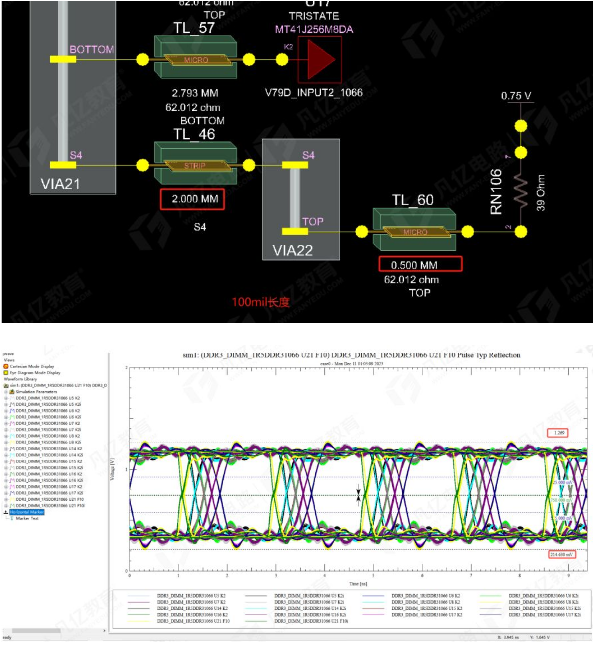

把最后一片DDR到终端电阻的距离设置成100mil的时候,可以可能到信号的眼图相对来说比较清晰,眼宽眼高明显,信号上冲和下冲较小。

当我们把距离加到300mil之后我们会发现,信号的过冲和下冲没有明显的增大,信号眼图达标。

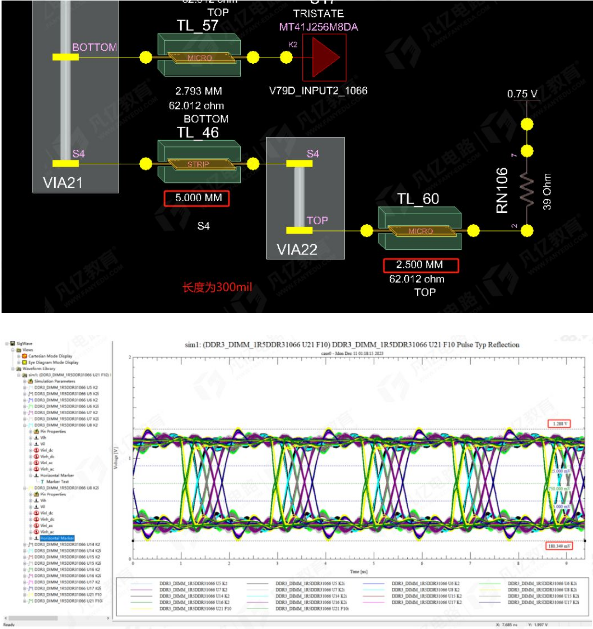

在距离为500mil的时候,虽然信号眼图也能符合要求,但是随着长度的增加信号的过冲和下冲会继续增大。

我们做最后一次仿真,把距离设置为1000mil的时候,可以发现其结果和我们之前的仿真结果类似,过冲和下冲都有增大,但是在把距离设置成1000mil的时候我们会发现其改善效果越来越差,信号的眼宽眼高都有一定程度的变窄,

综上所述,我们可以得出结论,在DDR末端的端接电阻距离最后一片DDR的长度越短越好,越短其信号质量越佳,以上仿真我们分别设置了4个不一样的长度距离,至少在500mil以内信号的眼图没有太明显的变化,在实际应用当中我们也是按照通用规范DDR末端的匹配电阻长度最好控制在500mil以内。

声明:本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论