关于滤波电容、去耦电容、旁路电容作用及其原理

从电路来说,总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流相对于正常情况来说实际上就是一种噪声,会影响前级的正常工作。这就是耦合。

去藕电容就是起到一个电池的作用,满足驱动电路电流的变化,避免相互间的耦合干扰。

旁路电容实际也是去藕合的,只是旁路电容一般是指高频旁路,也就是给高频的开关噪声提高一条低阻抗泄防途径。高频旁路电容一般比较小,根据谐振频率一般是0.1u,0.01u等,而去耦合电容一般比较大,是10u或者更大,依据电路中分布参数,以及驱动电流的变化大小来确定。

去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电流的大小、期望的纹波大小、作用时间的大小来计算。去耦电容一般都很大,对更高频率的噪声,基本无效。旁路电容就是针对高频来的,也就是利用了电容的频率阻抗特性。电容一般都可以看成一个RLC串联模型。在某个频率,会发生谐振,此时电容的阻抗就等于其ESR。如果看电容的频率阻抗曲线图,就会发现一般都是一个V形的曲线。具体曲线与电容的介质有关,所以选择旁路电容还要考虑电容的介质,一个比较保险的方法就是多并几个电容。

去耦电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是0.1μF。这个电容的分布电感的典型值是5μH。0.1μF的去耦电容有5μH的分布电感,它的并行共振频率大约在7MHz左右,也就是说,对于10MHz以下的噪声有较好的去耦效果,对40MHz以上的噪声几乎不起作用。

1μF、10μF的电容,并行共振频率在20MHz以上,去除高频噪声的效果要好一些。每10片左右集成电路要加一片充放电电容,或1个蓄能电容,可选10μF左右。最好不用电解电容,电解电容是两层薄膜卷起来的,这种卷起来的结构在高频时表现为电感。要使用钽电容或聚碳酸酯电容。去耦电容的选用并不严格,可按C=1/F,即10MHz取0.1μF,100MHz取0.01μF。

退耦原理:(去耦即退耦)

高手和前辈们总是告诉我们这样的经验法则:“在电路板的电源接入端放置一个1~10μF的电容,滤除低频噪声;在电路板上每个器件的电源与地线之间放置一个0.01~0.1μF的电容,滤除高频噪声。”在书店里能够得到的大多数的高速PCB设计、高速数字电路设计的经典教程中也不厌其烦的引用该首选法则(老外俗称Rule of Thumb)。但是为什么要这样使用呢?

首先就我的理解介绍两个常用的简单概念

什么是旁路?旁路(Bypass),是指给信号中的某些有害部分提供一条低阻抗的通路。电源中高频干扰是典型的无用成分,需要将其在进入目标芯片之前提前干掉,一般我们采用电容到达该目的。用于该目的的电容就是所谓的旁路电容(Bypass Capacitor),它利用了电容的频率阻抗特性(理想电容的频率特性随频率的升高,阻抗降低,这个地球人都知道),可以看出旁路电容主要针对高频干扰(高是相对的,一般认为20MHz以上为高频干扰,20MHz以下为低频纹波)。

什么是退耦?退耦(Decouple), 最早用于多级电路中,为保证前后级间传递信号而不互相影响各级静态工作点的而采取的措施。在电源中退耦表示,当芯片内部进行开关动作或输出发生变化时,需 要瞬时从电源在线抽取较大电流,该瞬时的大电流可能导致电源在线电压的降低,从而引起对自身和其他器件的干扰。为了减少这种干扰,需要在芯片附近设置一个 储电的“小水池”以提供这种瞬时的大电流能力。

在电源电路中,旁路和退耦都是为了减少电源噪声。旁路主要是为了减少电源上的噪声对器件本身的干扰(自我保护);退耦是为了减少器件产生的噪声对电源的干扰(家丑不外扬)。有人说退耦是针对低频、旁路是针对高频,我认为这样说是不准确的,高速芯片内部开关操作可能高达上GHz,由此引起对电源线的干扰明显已经不属于低频的范围,为此目的的退耦电容同样需要有很好的高频特性。本文以下讨论中并不刻意区分退耦和旁路,认为都是为了滤除噪声,而不管该噪声的来源。

简单说明了旁路和退耦之后,我们来看看芯片工作时是怎样在电源线上产生干扰的。我们建立一个简单的IO Buffer模型,输出采用图腾柱IO驱动电路,由两个互补MOS管组成的输出级驱动一个带有串联源端匹配电阻的传输线(传输线阻抗为Z0)。

设电源引脚和地引脚的封装电感和引线电感之和分别为:Lv和Lg。两个互补的MOS管(接地的NMOS和接电源的PMOS)简单作为开关使用。假设初始时刻传输在线各点的电压和电流均为零,在某一时刻器件将驱动传输线为高电平,这时候器件就需要从电源管脚吸收电流。在时间T1,使PMOS管导通,电流从PCB板上的VCC流入,流经封装电感Lv,跨越PMOS管,串联终端电阻,然后流入传输线,输出电流幅度为VCC/(2×Z0)。电流在传输线网络上持续一个完整的返回(Round-Trip)时间,在时间T2结束。之后整个传输线处于电荷充满状态,不需要额外流入电流来维持。当电流瞬间涌过封装电感Lv时,将在芯片内部的电源提供点产生电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN,Simultaneous Switching Noise;SSO,Simultaneous Switching Output Noise)或Delta I噪声。

在时间T3,关闭PMOS管,这一动作不会导致脉冲噪声的产生,因为在此之前PMOS管一直处于打开状态且没有电流流过的。同时打开NMOS管,这时传输线、地平面、封装电感Lg以及NMOS管形成一回路,有瞬间电流流过开关B,这样在芯片内部的地结点处产生参考电平点被抬高的扰动。该扰动在电源系统中被称之为地弹噪声(Ground Bounce,我个人读着地tan)。

实际电源系统中存在芯片引脚、PCB走线、电源层、底层等任何互联机都存在一定电感值,因此上面就IC级分析的SSN和地弹噪声在进行Board Level分析时,以同样的方式存在,而不仅仅局限于芯片内部。就整个电源分布系统来说(Power Distribute System)来说,这就是所谓的电源电压塌陷噪声。因为芯片输出的开关操作以及芯片内部的操作,需要瞬时的从电源抽取较大的电流,而电源特性来说不能快速响应该电流变化,高速开关电源开关频率也仅有MHz量级。为了保证芯片附近电源在线的电压不至于因为SSN和地弹噪声降低超过器件手册规定的容限,这就需要在芯片附近为高速电流需求提供一个储能电容,这就是我们所要的退耦电容。

所以电容重要分布参数的有三个:等效串联电阻ESR 等效串联电感ESL 、等效并联电阻EPR Rp 。其中最重要的是ESR、 ESL,实际在分析电容模型的时候一般只用RLC简化模型,即分析电容的C、ESR、ESL。因为寄生参数的影响,尤其是ESL的影响,实际电容的频率特性表现出阻抗和频率成“V”字形的曲线,低频时随频率的升高,电容阻抗降低;当到最低点时,电容阻抗等于ESR;之后随频率的升高,阻抗增加,表现出电感特性(归功于ESL)。因此对电容的选择需要考虑的不仅仅是容值,还需要综合考虑其他因素。

所有考虑的出发点都是为了降低电源地之间的感抗(满足电源最大容抗的条件下),在有瞬时大电流流过电源系统时,不至于产生大的噪声干扰芯片的电源地引脚。

电容的频率特性

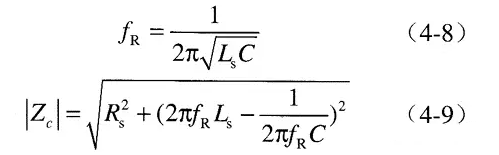

当频率很高时,电容不再被当做集总参数看待,寄生参数的影响不可忽略。寄生参数包括Rs,等效串联电阻(ESR)和Ls等效串联电感(ESL)。电容器实际等效电路如图1所示,其中C为静电容,1Rp为泄漏电阻,也称为绝缘电阻,值越大(通常在GΩ级以上),漏电越小,性能也就越可靠。因为Pp通常很大(GΩ级以上),所以在实际应用中可以忽略,Cda和Rda分别为介质吸收电容和介质吸收电阻。介质吸收是一种有滞后性质的内部电荷分布,它使快速放电后处于开路状态的电容器恢复一部分电荷。

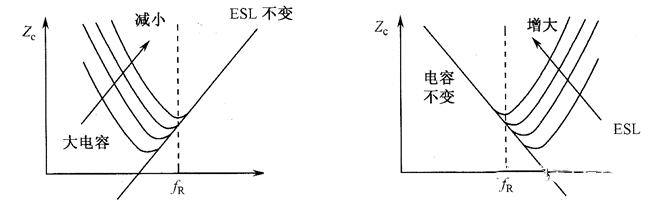

ESR和ESL对电容的高频特性影响最大,所以常用如图1(b)所示的串联RLC简化模型,可以计算出谐振频率和等效阻抗: 图1 去耦电容模型图

图1 去耦电容模型图

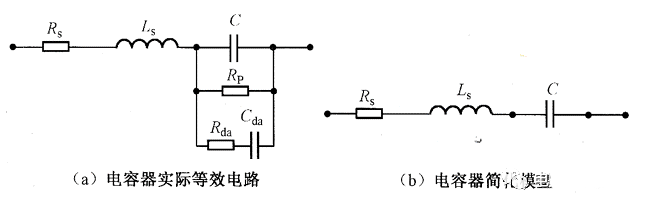

电容器串联RLC模型的频域阻抗图如图2所示,电容器在谐振频率以下表现为容性;在谐振频率以上时表现为感性,此时的电容器的去耦作用逐渐减弱。同时还发现,电容器的等效阻抗随着频率的增大先减小后增大,等效阻抗最小值为发生在串联谐振频率处的ESR。 图2 电容器串联RLC模型的频域阻抗图

图2 电容器串联RLC模型的频域阻抗图

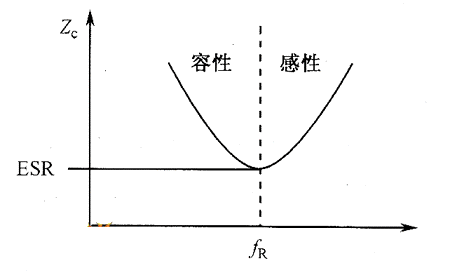

由谐振频率式(4-8)可得出,容值大小和ESL值的变化都会影响电容器的谐振频率,如图3所示。由于电容在谐振点的阻抗最低,所以设计时尽量选用fR和实际工作频率相近的电容。在工作频率变化范围很大的环境中,可以同时考虑一些fR较小的大电容与fR较大的小电容混合使用。

暂无评论