凡亿教育-媛媛

凡事用心,一起进步打开APP

公司名片防止串扰可不止3W规则,还有这些方法

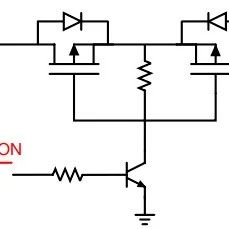

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。

串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用。

一般来说,是通过加大平行布线间距(3W规则)、在平行线间插入接地的隔离线和减小布线层与地平面的距离等来解决。

但在实际情况下,3W规则并不能完全满足串扰抑制要求。所以可以通过以下方法来解决:

1、对高速线路提供正确的终端;

2、尽量降低信号到地平面的间隔;

3、尽量使用平衡线、屏蔽线或同轴线;

4、可将高速周期信号布置在PCB内层;

5、尽量最小化元器件之间的距离;

6、尽量根据功能分类逻辑器件系列,保持总线结构被严格控制;

7、尽可能增大信号线间距离,以此减少容性串扰。

8、微带或带状线上的布线要互相垂直,以此防止层间的电容耦合。

9、可使用阻抗匹配以此保证信号完整性,降低过冲概率。

10、骚扰信号线和敏感线尽量做好滤波处理。

11、走线时尽量避免长距离且互相平行,要提供走线间足够的间隔,以最小化电感耦合。

12、分割和隔离高噪声发射源(时钟、I/O、高速互连),不同的信号分布在不同的层中。

13、对具有快速上升沿(tr≤3ns)的信号,进行包地等防串扰处理,将一些受EFTlB或ESD干扰且未经滤波处理的信号线布置在PCB的边缘。

14、对高频信号和敏感信号做包地处理,双面板中使用包地技术将获得10-15dB衰减。

15、高速信号线及元器件尽量远离I/O连接口及其他易受干扰耦合影响的区域。

声明:本文凡亿企业培训原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论