凡亿教育-雯雯

凡事用心,一起进步打开APP

公司名片还在头疼高速电路的传输效应?干就是了!

随着电子技术的飞速发展,高速电路的传输效应已成为一个不容忽视的问题,是很多电子工程师最为头痛的问题之一。本文将详细谈谈高速电路的传输效应,并给出合理的解决方案,希望对小伙伴们有所帮助。

高速电路的传输线效应是指系统工作在50MHz时,将产生传输线效应和信号的完整性问题。当系统时钟达到120MHz时,则必须使用高速电路设计只是才能使之正常工作,所以只有通过高速电路仿真和先进的物理设计软件,方可实现设计过程的可控性。

如何避免传输线效应?解决方法有以下:

1、严格控制关键网线的走线长度

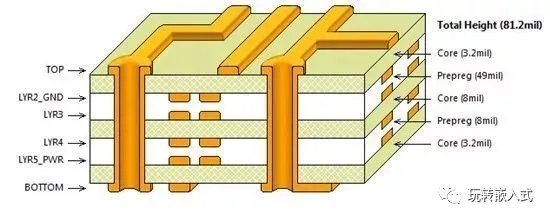

对于高速信号,其走线长度必须严格控制,以减少信号延迟和畸变。在PCB设计时,应使用等长线、对称结构和合适的层叠来确保信号的完整性。

2、合理规划走线的拓扑结构

根据实际需求选择合适的走线拓扑结构,如星型、总线型或菊花链型等。同时,应避免走线的直角和锐角,以减少信号反射和串扰。

3、抑制电磁干扰

通过使用有效的屏蔽、接地和滤波等手段,降低电磁辐射和耦合效应,从而减少串扰和电磁干扰。

4、添加去耦电容(降低其电压瞬时过冲)

在电路板的每个集成电路的电源和地之间添加去耦电容,可以有效降低电源和地之间的电位差,减少信号的电压瞬时过冲,提高信号质量。同时,去耦电容还可以吸收高频噪声,进一步抑制电磁干扰。

5、选择合适的端接方式

根据传输线的特性阻抗和终端设备的负载阻抗,选择合适的端接方式,如源端匹配、负载端匹配等,以此减少信号反射和失真。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论