SiP组件的失效模式主要表现为硅通孔(TSV)失效、裸芯片叠层封装失效、堆叠封装(PoP)结构失效、芯片倒装焊失效等,这些SiP的高密度封装结构失效是导致SiP产品性能失效的重要原因。

一、TSV失效模式和机理

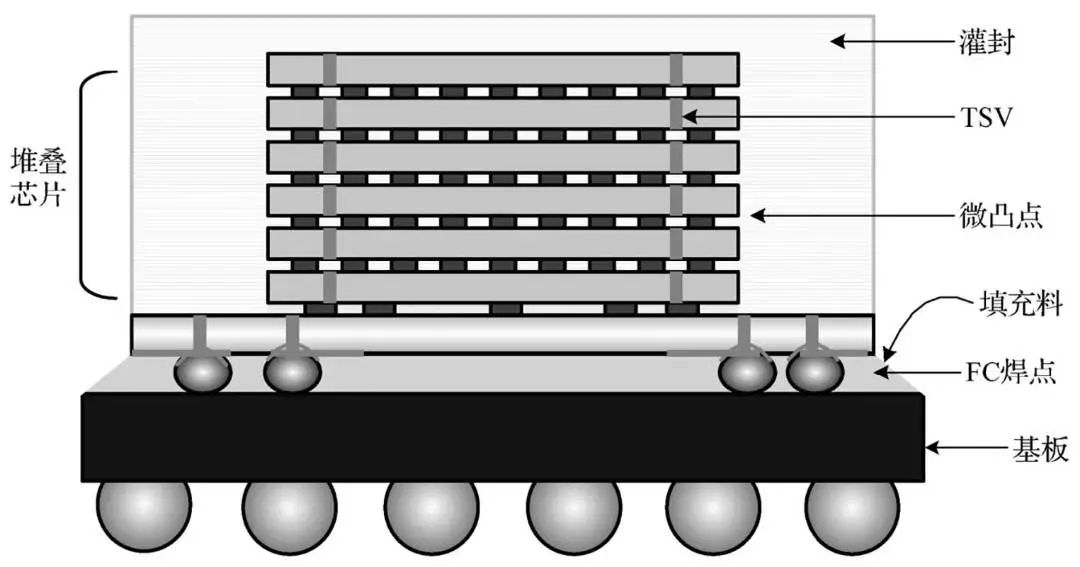

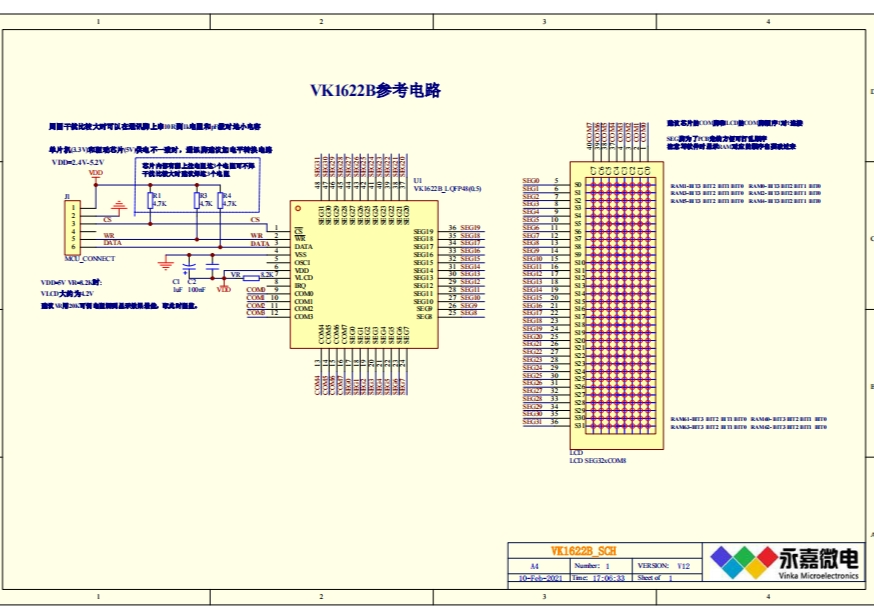

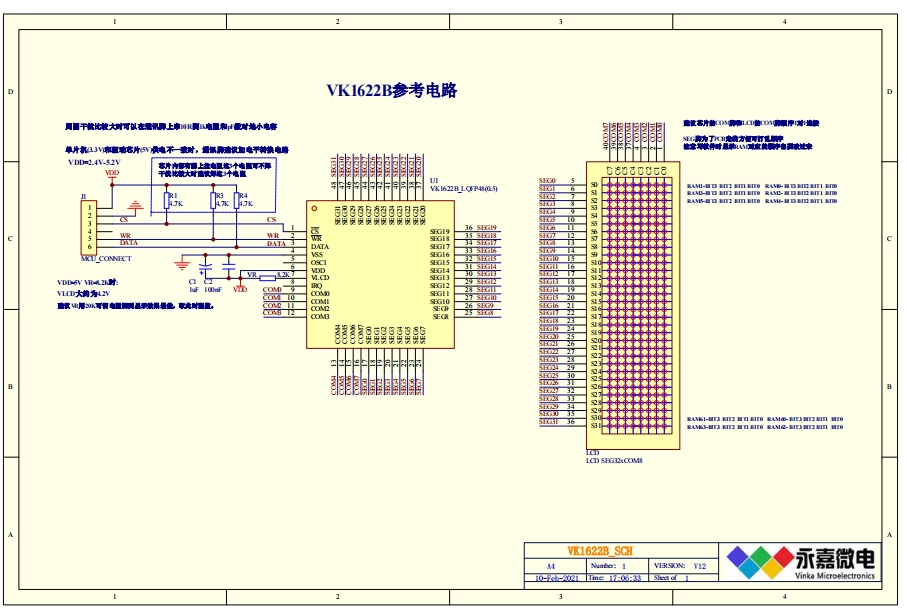

TSV是SiP组件中一种系统级架构的新的高密度内部互连方式,采用TSV通孔互连的堆叠芯片封装结构,如图1所示。TSV的工艺缺陷是导致其通孔互连失效的主要原因,有关TSV的工艺缺陷主要有以下3种模式。

图1 采用TSV通孔互连的堆叠芯片封装结构

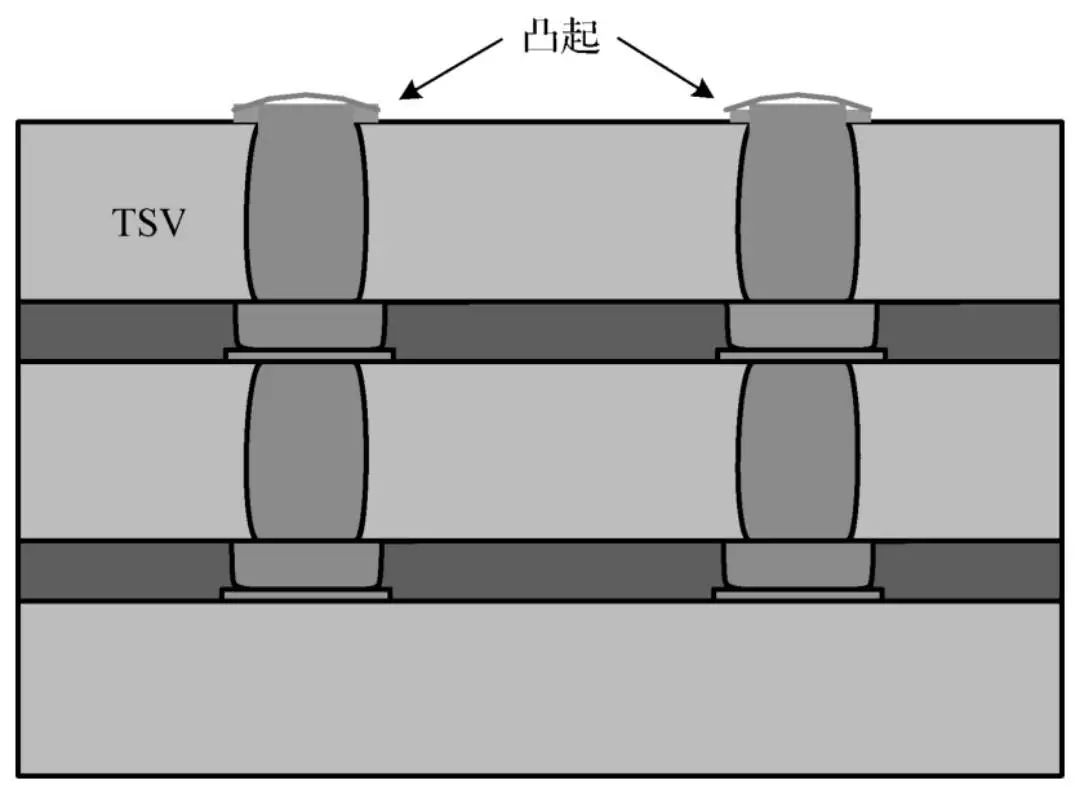

1.TSV凸起

TSV凸起,即出现在TSV表面的突出物,TSV表面的凸起示意图如图2所示,由于TSV凸起会损伤晶圆,对芯片堆叠结构的电互连构成潜在的风险。凸起的工艺缺陷原因在于,硅片通孔Cu电镀之后,晶片表面多余的Cu需要通过化学机械研磨去除并进行退火处理,退火前后温差较大,Cu与Si之间的热膨胀系数(CTE)失配,引起TSV内部电镀Cu材料产生较大的应力,而电镀Cu又受到周围Si衬底材料的约束,为了释放内部应力,电镀Cu只能垂直向外扩张,从而形成凸起。凸起缺陷产生于退火工艺,不同的退火条件对凸起的影响差异很大,退火温度越高,凸起越明显。另外,退火时间和TSV直径、深度、间距等参数对凸起的形成也起到一定的作用。

图2 TSV表面的凸起示意图

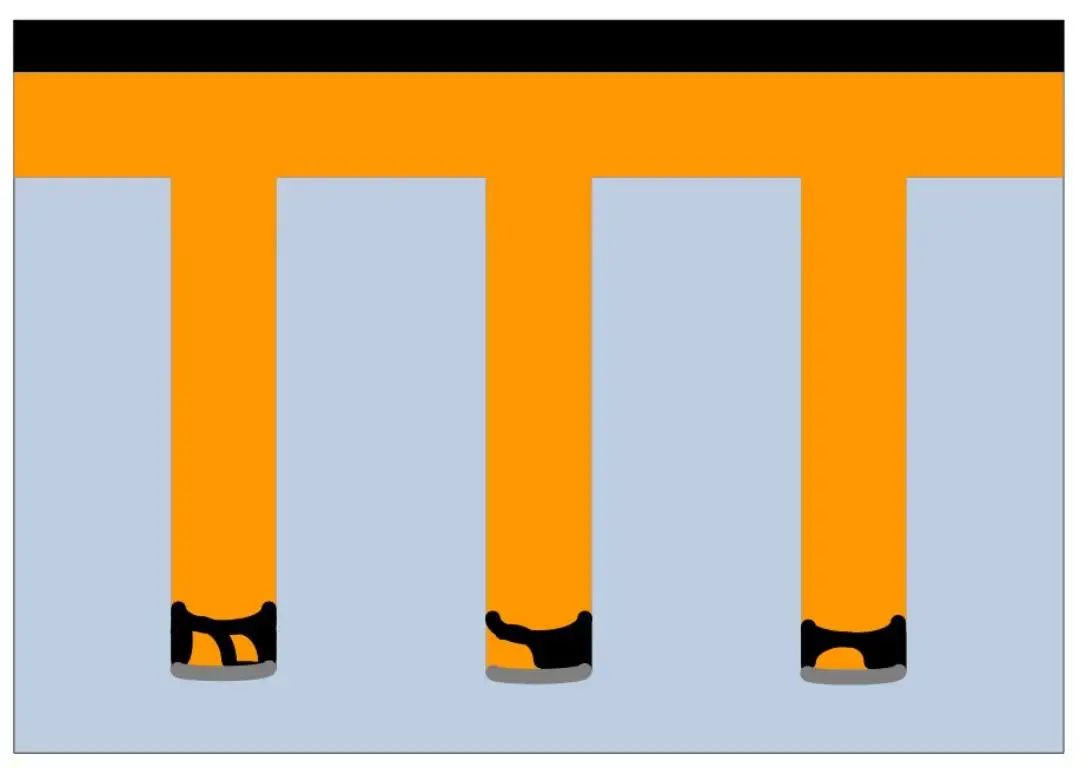

2.TSV填充空洞

TSV填充空洞缺陷,如图3所示。TSV填充空洞产生在TSV通孔填充结构中,将导致TSV互连电阻增加,甚至导致SiP组件开路失效,如果空洞产生在绝缘层内,如TSV的侧壁,将导致TSV和硅衬底间短路,产生漏电流。这种因填充不完全导致的空洞,是TSV工艺缺陷最普遍的问题。其主要原因在于,电镀时TSV通孔底部存在气泡,在TSV电镀Cu过程中,Cu填充过程是由侧壁向中间进行的,而Cu的沉积速率随电镀电流密度的增大而加快,由于TSV通孔口处的电镀电流密度较大,使得通孔口处的Cu比中间更早填充满,导致TSV通孔底部因不能继续填充而产生空洞,可以利用真空预处理显著改善TSV电镀效果。使Cu填充率接近100%。另外,刻蚀工艺产生的贝壳效应导致孔壁不平整、润湿不良,也是形成TSV填充空洞的一个关键因素。

图3 TSV填充空洞缺陷

3.TSV开裂分层

TSV填充材料和其他高温工艺的作用,还可能产生另一类高发缺陷—开裂分层。由于填充金属Cu、Si衬底和绝缘层SiO2之间的热膨胀系数不匹配,制造封装过程中的TSV内部将产生显著的热机械应力。在热机械应力的作用下,TSV微凸点将有可能发生开裂,凸点与通孔、焊盘之间有可能分层。微凸点是TSV互连的组成部分,实现上下堆叠层的电连接,微凸点的开裂缺陷引起凸点电阻增加,影响器件的电性能。

当TSV结构合理时,Cu区产生的应力很小,不会引起失效。然而这些应力的叠加与TSV的工艺缺陷结合极有可能产生失效,如瞬间界面分层、微凸点开裂和TSV开裂等。

二、芯片堆叠失效模式和机理

SiP组件的芯片叠层结构,大部分采用引线键合方式和引线键合/倒装焊混合的方式互连。叠层芯片封装的失效通常包括芯片开裂、分层、键合失效(开路或短路),以及其他与工艺相关的缺陷。

1.芯片开裂

造成叠层芯片开裂的原因主要有两个:一是过大的机械应力造成芯片开裂;二是温变应力和热失配,由于芯片和与其接触材料之间的热膨胀系数不匹配,在回流焊等温度变化大的情况下热膨胀程度不一样,在接触面会产生剪切应力和张应力,芯片有微小裂纹的地方受到应力作用极易开裂。

2.分层

分层可能出现在芯片与引线框、芯片与焊点、引线框与塑封料、芯片与塑封料、焊点与基板等位置。引起分层的原因有热机械失配、机械负载、体积收缩或膨胀、内部压力、界面反应(如氧化、潮湿、污染等)引起的黏胶剂脱落。

3.键合失效

键合失效表现主要为键合点开路和键合丝断。造成键合点开路的可能原因有金铝化合物失效、键合工艺不良、热疲劳开裂、腐蚀等。键合丝断的原因主要是大电流熔断和机械应力。

4.工艺缺陷

晶片减薄工艺造成的缺陷主要是粗糙与翘曲问题。减薄的晶圆厚度低,易断裂,并且因背面研磨常使芯片表面凹凸不平,容易在局部产生较大应力,晶圆划片的主要问题是崩裂、背崩现象。由于晶圆很薄、很脆,背崩就可能延伸到晶圆正面,发生崩裂;如果崩裂程度轻微,不易被发现,可能会在后期影响器件的可靠性。叠层芯片封装潜在的可靠性问题:因布局结构带来叠层芯片的受力不均;堆叠对准精度差,影响导电等性能;模塑封装工序使用的材料不当将会引入热失配、气密不佳和散热差等诸多问题。

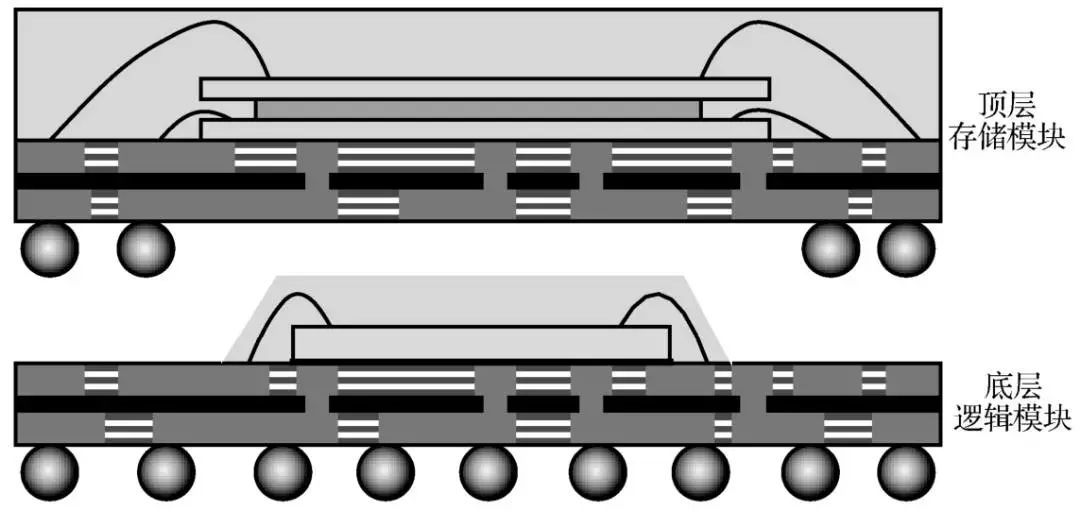

三、 PoP封装堆叠失效模式和机理

堆叠封装(PoP)又称为封装堆叠,是指在底部带封装的元器件上面再叠放一个带封装的元器件,例如,逻辑模块 存储模块,这种叠层通常在2~4层,存储型PoP可达到8层,SiP组件存储芯片封装和逻辑芯片封装的PoP结构如图4所示。

图4 SiP组件存储芯片封装和逻辑芯片封装的PoP结构

SiP组件中PoP封装结构的失效模式,主要有翘曲、焊点失效、下填充胶分层开裂、工艺缺陷。

1.翘曲

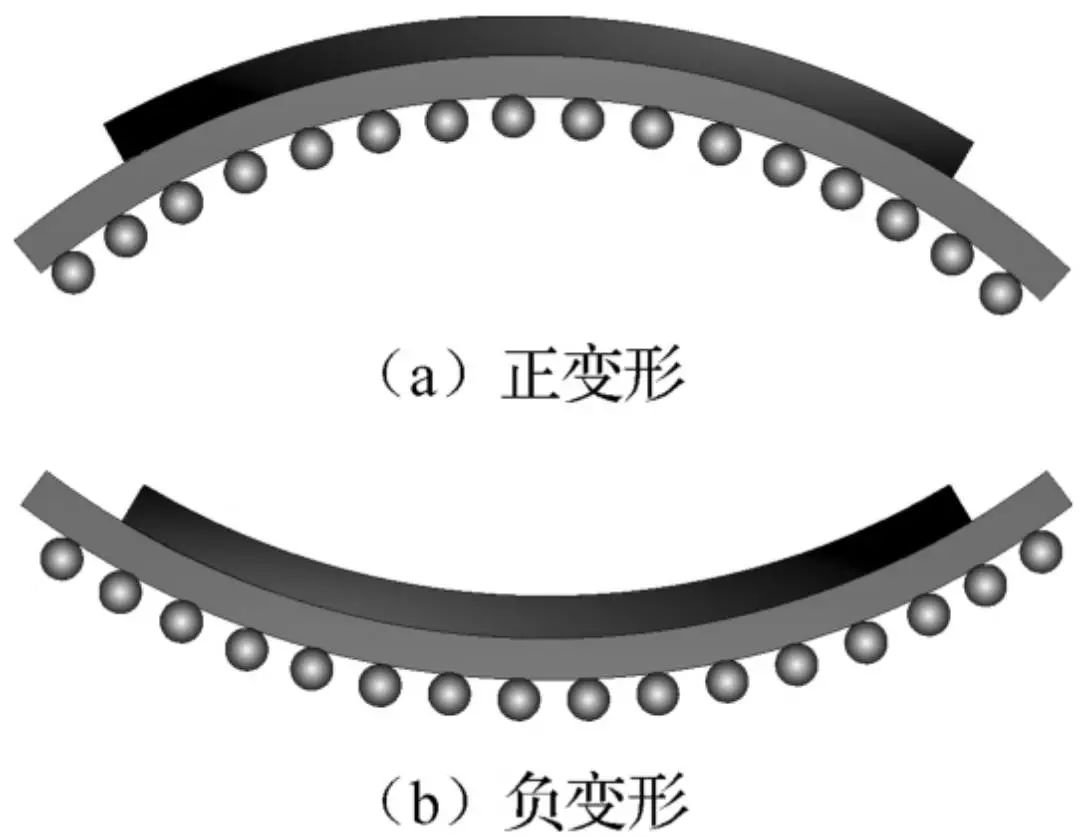

PoP面临的最严重的可靠性问题是翘曲,封装体由于受力不平衡引起弯曲变形。翘曲是因为材料间的热膨胀系数不匹配,再加上黏着力的限制,在外界温度变化的影响下,封装材料间应释放因温度影响而产生的内应力,故而通过翘曲变形来消除内应力。基板和芯片之间的热膨胀系数失配是产生翘曲变形的主要原因,常发生于温度变化大的回流焊工艺。翘曲分为正变形和负变形,向上凸为正变形,向下凹为负变形,PoP翘曲形状如图5所示。

图5 PoP翘曲形状

2.焊点失效

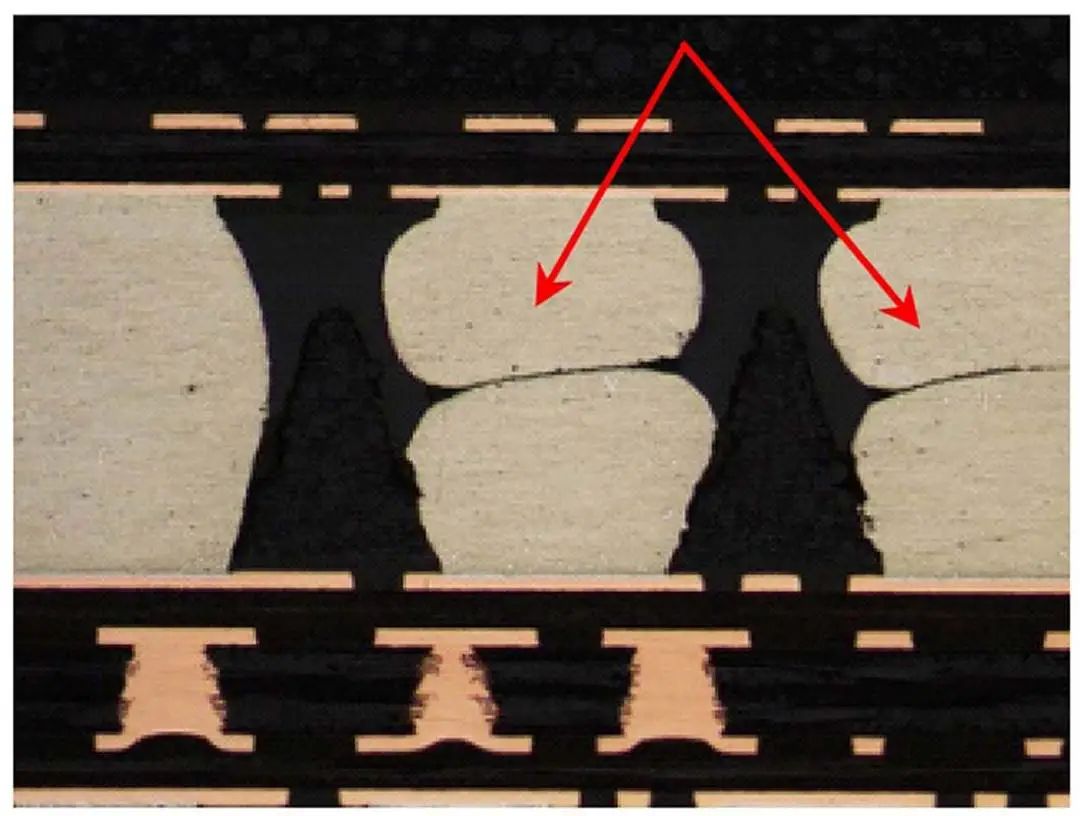

PoP焊点常见的工艺缺陷有空洞、开裂、未对准、桥连、枕头效应、间距问题等。当上下两个封装体进行堆叠时,顶层封装体的下表面焊点和底层封装体的上表面焊点进行融合,可能出现上下焊点没有完全融合的枕头效应,PoP焊点枕头效应微观形貌如图6所示。

图6 PoP焊点枕头效应微观形貌

如果底层芯片使用倒装焊连接,由于芯片和基板之间的热膨胀系数不一致,在热循环作用下,芯片和基板收缩和扩张的程度不同,焊点将承受周期性剪切应力从而引起焊点变形和蠕变失效,最终导致焊点开裂。

3.下填充胶分层开裂

由于塑性基板与芯片的膨胀系数相差比较大,两者在温变大的情况下将对焊点产生剪切应力。为了减小焊点承受的剪切应力,通常在缝隙之间会加入填充胶,而填充胶在热循环应力的频繁作用下会发生分层开裂。

4.工艺缺陷

在PoP焊接过程中可能出现的缺陷有底部元器件短路,可能的原因有锡膏印刷、贴装压力、元件受热变形;顶部元器件电气开路,可能的原因有元件受热变形、焊球高度差异、润湿不良、底部元件模塑过厚、回流温度过高;顶部元器件电气短路,可能的原因有助焊剂过多、热变形、贴装精度差等。

暂无评论