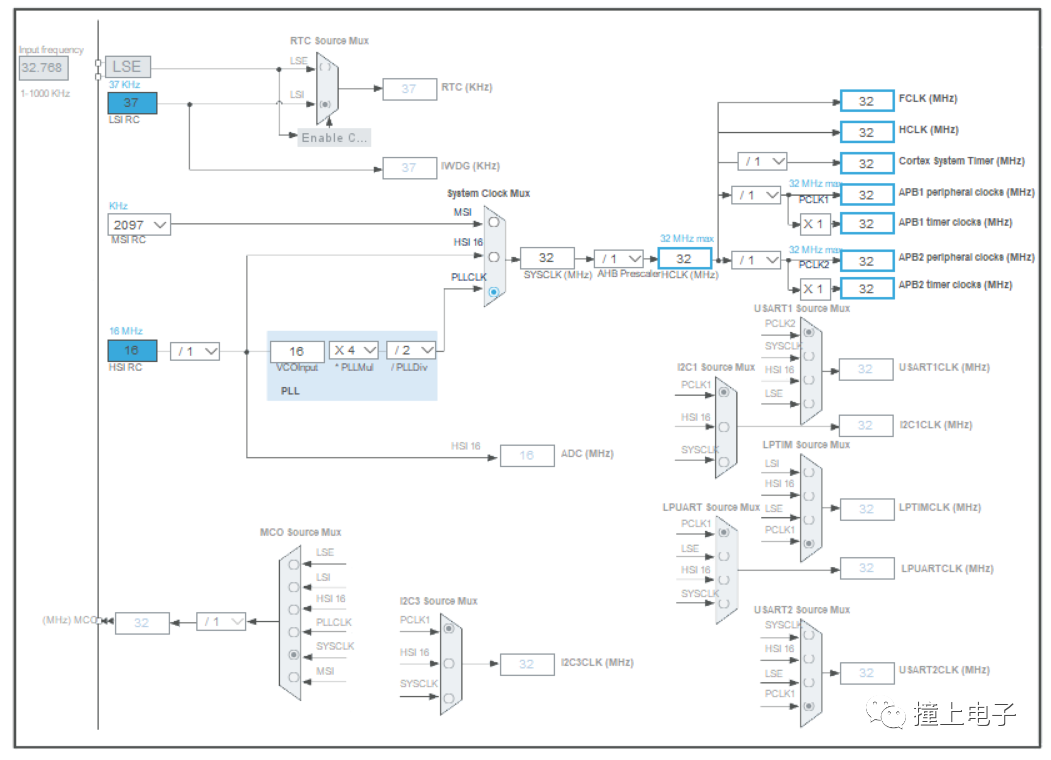

1,低速时钟

LSE是外部晶振作时钟源,主要提供给实时时钟模块,所以一般采用32.768KHz。LSI是由内部RC振荡器产生,也主要提供给实时时钟模块,频率大约为40KHz。(LSE和LSI)只是提供给芯片中的RTC(实时时钟)及IWDG(独立看门狗)使用。

2,中速时钟

MSI RC是“中速内部时钟”或“中速内部振荡器”,是STM32L系列独有的时钟,RC表示这个时钟源是通过RC振荡器实现的,它可提供7种频率的时钟源,范围:65.636kHz~4194KHz。可以直接选择为SYSCLK(系统时钟)的时钟源,也可以作为MOC(时钟输出)的时钟源。

3,高速时钟

HSI RC是内部高速时钟,可以直接选择为系统时钟,可以作为PLL(锁相环倍频输出)的时钟源,还可以作为ADC,USART1,USART2,I2C1,I2C3,LPTIM(低功耗定时器),LPUART(低功耗串口)和MCO(主时钟输出)的时钟源,是最重要的时钟之一。

4,锁相环

PLL代表锁相环,在STM32中PLL可以被用于倍频或者分频SYSCLK(系统时钟),其倍数可以是外部高速晶振的倍数。

5,系统时钟

SYSCLK是系统时钟,由MSI,HSI和PLLCLK提供,是整个系统的核心,SYSCLK的频率直接影响整个系统的运行速度。

6,AHB系统总线

AHB高级高性能总线,这是一种“系统总线”。主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。AHB系统由主模块、从模块和基础结构3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

7,HCLK主总线时钟

HCLK 是主总线时钟,由 SYSCLK 通过 AHB 分频器得到的,控制着主总线的时钟频率。HCLK驱动CPU核心、存储器(Flash和RAM)以及其他一些主总线上的外设。

8,FCLK自由运行时钟

FCLK是自由运行时钟,“自由”表现在它不来自系统时钟HCLK,在系统时钟停止时FCLK也继续运行。FCLK用作采样中断或者为调试模块计时。在处理器休眠时,通过FCLK可以采样到中断和跟踪休眠事件。Cortex-M内核的FCLK和HCLK互相同步、互相平衡,保证Cortex-M的延迟相同。

9,Cortex system timer

Cortex system timer是Cortex的系统时钟,常用作滴答定时器。

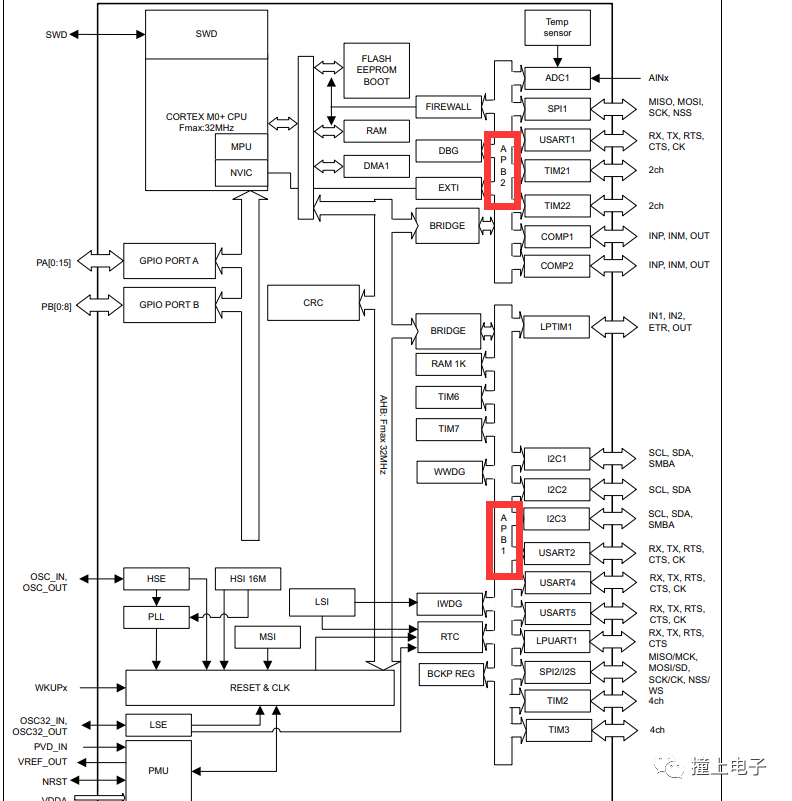

10,APB1和APB2

APB1 peripheral clocks与APB1 timer clocks分别是APB1的外设时钟和APB1的定时器时钟,同理,APB2 peripheral clocks与APB1 timer clocks分别是APB2的外设时钟和APB2的定时器时钟。那么APB1和APB2是什么呢?我们可以在数据手册上看到下面的方框图,图中介绍了各种外设的关系。比如APB1掌管TIM2,TM3,I2C3等。

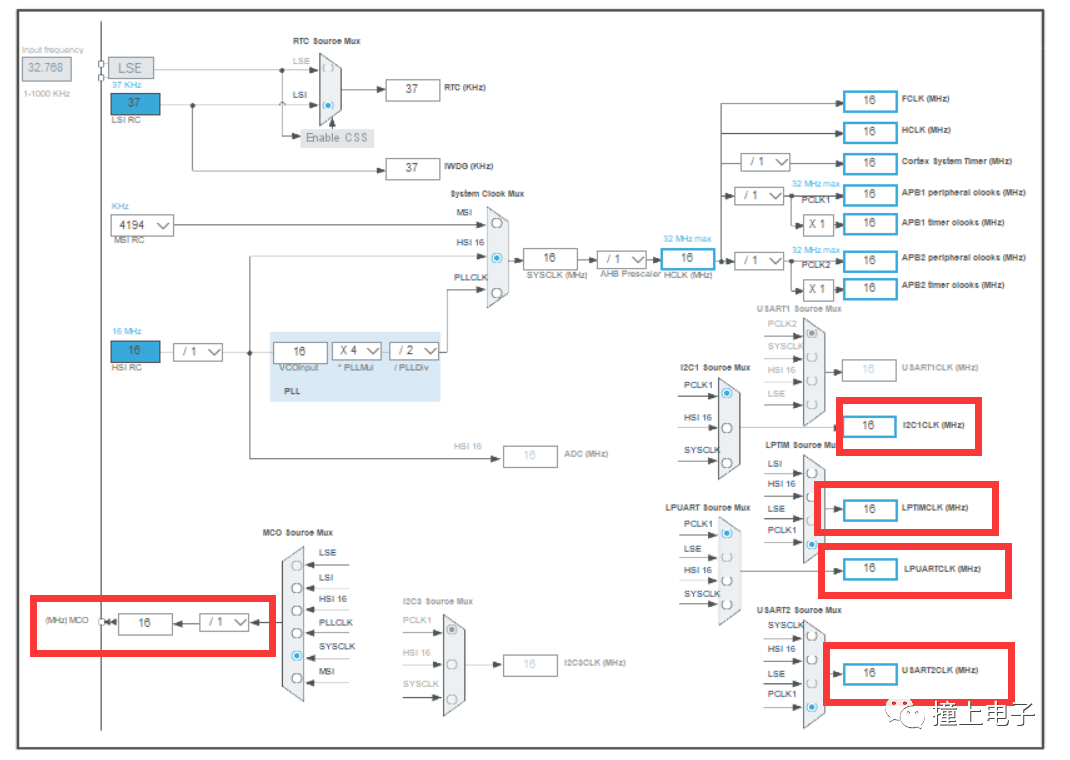

11,外设时钟

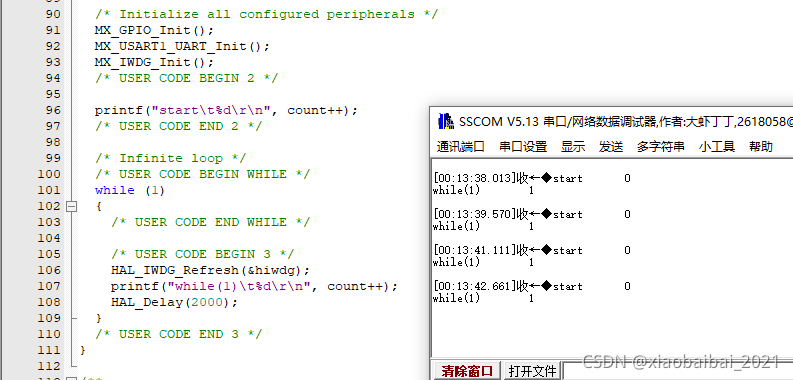

灰色部分的是因为STM32CubeMX没有激活该功能,激活后就会变成这样:

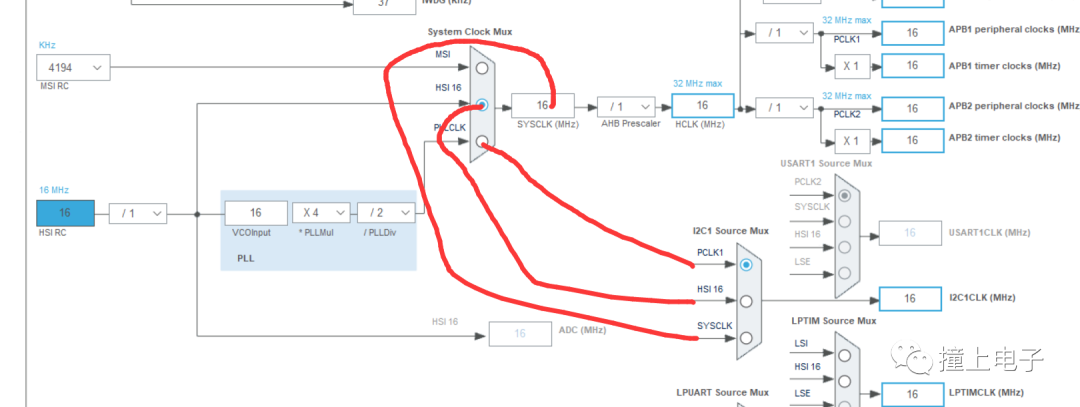

这些都是常见的外设,时钟来源也已经标注出来了,比如I2C1的时钟来源有PCLK1,HSI和SYSCLK。如下图:

暂无评论