锁相环(PLL)是一种反馈控制电路,通过不断比较外部参考信号和内部振荡信号的频率与相位,进而调整内部振荡信号的参数,以此实现两者之间的同步,在需要调整输出频率的倍数时,锁相环有特定技术来实现倍频功能,那么这个技术是如何实现?

1、锁相环的基本原理

锁相环属于闭环控制系统,用于使振荡器的相位与输入信号的相位保持同步,一般来说,PLL的组成结构主要分为三种,分别是鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)。

2、锁相环实现倍频的具体步骤

①设置基准信号

选择一个稳定的参考信号作为PLL的输入,其频率为f_ref。

②配置分频器

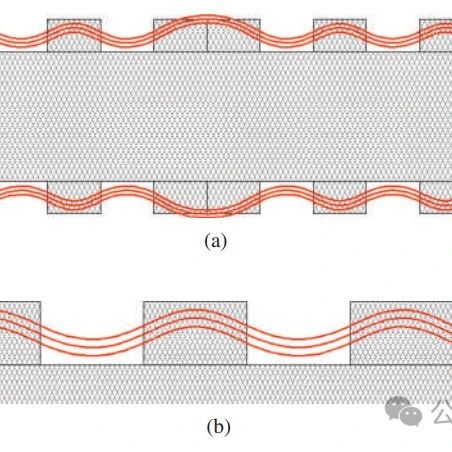

在PLL的反馈回路中设置一个分频器,其分频比为N(N是整数),该分频器将VCO的输出信号频率f_vco降低N倍,产生一个频率为f_vco/N的反馈信号。

③启动PLL

当PLL启动后,鉴相器会比较输入的基准信号与分频后的反馈信号的相位差,若两者之间存在相位差,鉴相器将输出一个与相位差成比例的电压信号。

④环路滤波器

鉴相器输出的电压信号经过环路滤波器进行滤波,产生一个平滑的直流控制电压Vc,该控制电压Vc将用于调整VCO的输出频率。

⑤压控振荡器(VCO)调整

Vc作用于VCO,使其输出信号的频率f_vco向减小相位差的方向调整,当f_vco/N与f_ref相等时,PLL达到锁定状态,此时f_vco为f_ref的N倍,即实现了倍频功能。

3、关键参数及注意事项

①分频比N

选择适当的分频比N是实现倍频的关键。N的值越大,倍频倍数越高,但系统的稳定性和带宽可能会受到影响。

②环路滤波器设计

环路滤波器的设计对PLL的性能至关重要。需要权衡滤波器的带宽、噪声抑制能力和相位裕量等因素。

③VCO性能

VCO的线性度、频率范围和稳定性都会影响PLL的倍频性能。因此,在选择VCO时需要考虑其性能指标。

本文凡亿教育原创文章,转载请注明来源!

暂无评论