以太网口是我们日常工程中常用的通信接口,以太网接口有很多种,本文将对常用以太网接口进行科普介绍。

1、GMII接口1.1 GMII接口概述

GMII接口属于源同步时钟类型(时钟与数据都是由同一芯片驱动),时钟速率125MHz,接口连接关系如图1所示,22根线,其中TX_EN, TX_ER, TXD<7:0>这些信号同步于TX_CLK;RX_DV, RX_ER,

图1 GMII接口原理框图

RXD<7:0>这些信号同步于RX_CLK。其它的两个信号CRS, COL只用于半双工模式,一般设计中不会用到,而且这两个信号与时钟是异步的,对这两个信号不做要求。各信号说明见表1。

表1 UTOPIA LEVEL 2接口信号说明

信号名称 | 信号说明 |

TX_CLK | 发送方向时钟信号 |

TX_EN | 发送方向使能信号 |

TX_ER | 发送方向错误指示信号 |

TXD<7:0> | 发送方向数据信号 |

RX_CLK | 接收方向时钟信号 |

RX_DV | 接收方向使能信号 |

RX_ER | 接收方向错误指示信号 |

RXD<7:0> | 接收方向数据信号 |

COL | 碰撞指示信号 |

CRS | 载荷检测信号 |

1.2 设计原则

1、要求同方向的时钟数据严格等长,即TX_EN, TX_ER, TXD<7:0>这些控制/数据信号与TX_CLK等长;RX_DV, RX_ER, RXD<7:0>这些控制/数据信号与RX_CLK等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于1cm(约0.1ns)。

2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)

4、因信号线较多,在布局允许情况下,PHY与MAC尽量靠近,减小高速信号受的串扰。

2、RGMII接口概述2.1 RGMII接口概述

RGMII属于源同步时钟类型,最初是由HP制定的一个GMII精简版专利标准,得到各大主流厂家的认可,成为一个普遍应用的关于xMII系列接口的标准。RGMII经历了1.0\1.1\1.2\1.2a\1.3\2.0几个版本。从2.0版本开始支持HSTL,之前的版本支持2.5V CMOS。

TXC/RXC时钟频率支持125MHz,25MHz,2.5MHz,可以适配1000M,100M,10M速率。在时钟的上升沿和下降沿均进行数据采样,相比GMII接口,数据信号线收发方向各减半变为4根,信号线总共有12根。如图2和表2说明。

图2 RGMII接口原理框图

表2 RGMII接口信号说明

信号 | 方向 | 说明 |

TXC | MAC-->PHY | 发送时钟信号 |

TX[3:0] | MAC-->PHY | 发送数据信号 |

TX_CTL | MAC-->PHY | 发送控制信号 |

RXC | MAC<--phy<> | 接收时钟信号 |

RX[3:0] | MAC<--phy<> | 接收数据信号 |

RX_CTL | MAC<--phy<> | 接收控制信号 |

2.2 设计原则

1、要求同方向的时钟数据严格等长,即TX_CTL,TXD<3:0>这些控制/数据信号与TXC等长;RX_CTL,RXD<3:0>这些控制/数据信号与RXC等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于0.5cm(约0.05ns)。

2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

4、因信号线较多,在布局允许情况下,PHY与MAC尽量靠近,减小高速信号受的串扰,线长最好小于4000mil。

3、SS_SMII接口3.1 SS_SMII 接口概述

SS_SMII(又叫S3MII)接口属于源同步时钟类型,接口原理框图如图3所示,时钟速率125M Hz;信号与时钟间的关系等同于GMII。

图3 S3MII接口原理框图

3.2 SS_SMII接口设计原则

1、要求TX_SYNC, TXD信号与TX_CLK等长;RX_SYNC, RXD信号与RX_CLK等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于1cm(约0.1ns)。

2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

4、在时间允许的情况下,尽量对接口进行仿真。

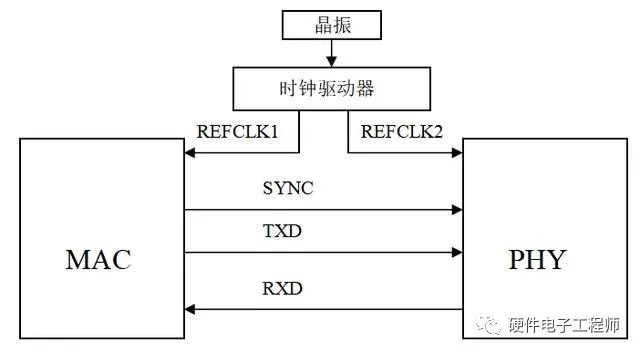

4、SMII接口4.1 SMII接口概述

SMII接口公共时钟模型(两端芯片的时钟来自共同的时钟BUFFER),时钟速率125M Hz,接口原理框图如图4所示;并不要求数据线与时钟等长。

4.2 SMII接口设计原则

设计时可以先考虑使REFCLK1, REFCLK2等长。

图4 SMII接口原理框图

2、要求SYNC,TXD,RXD这几个信号走线尽量短;(从芯片资料理论上看出这些线

的最大长度为1.5ns,21cm;但由于芯片差异性较大,因此实际布线中尽量走短)。

要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性;

信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

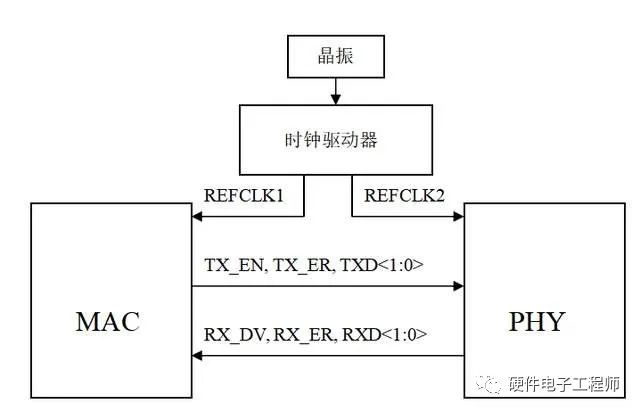

5、RMII接口5.1 RMII接口概述

RMII接口属于公共时钟传输模型,时钟速率50M Hz;并不要求数据线与时钟等长。图5所示为RMII接口的原理框图。

图5 RMII接口原理框图

5.2 RMII接口设计原则

设计时可以先考虑使REFCLK1, REFCLK2等长。

要求其它的数据/控制信号走线尽量短;(RMII规范规定信号的驱动能力在包含负载输入电容情况下不小于12inch,也就是30cm;但由于芯片差异,实际布线情况下尽量短)。

要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

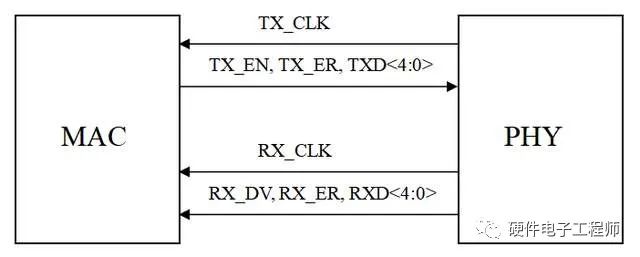

6、MII接口

MII接口属于公共时钟传输模型,时钟频率25M(100M以太网)或2.5M(10M以太网)。两个时钟都是由Phy发送给MAC的。接口框图如图6所示。另外,该接口的其它两个信号CRS、COL是异步信号,无特殊要求,故不在此图中画出。

对于MII信号,由于信号速率较低,因此在布线上无特殊要求,只要求Phy与MAC离的不要太远就可以了。

图6 MII接口原理框图

暂无评论