之前我们在“Buck振铃尖峰的实验与分析”一文中详细分析了buck振铃的来龙去脉,提到Snubber电路是解决这个问题的一种方式,不过没有具体说明具体该如何解决。最近在TI的网站上看到了 一个Snubber详细设计的文档,就直接转过来分享给兄弟们了,详细内容如下文。

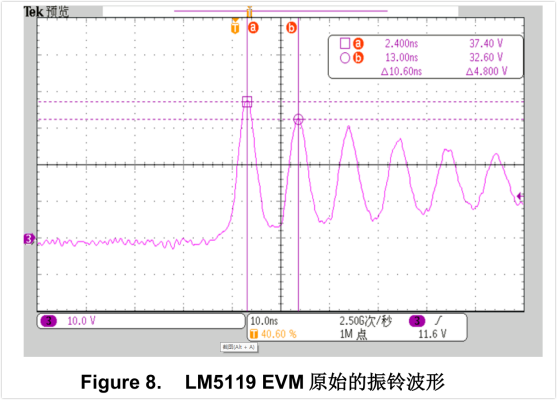

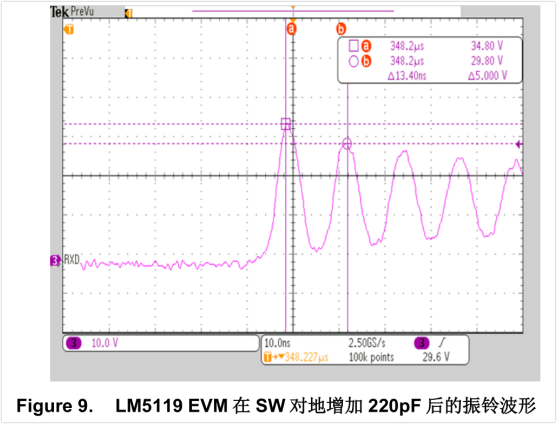

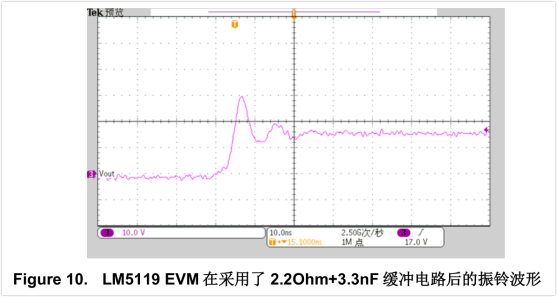

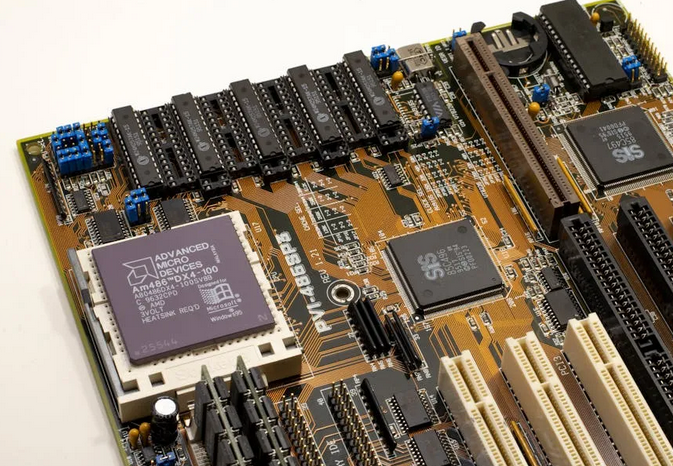

本应用报告首先给出了降压式开关电路(buck)在上管开通瞬间的的一个等效谐振回路模型。根据该模型推导出使得开关振铃最小化的阻容缓冲电路(snubber)的参数计算公式,并结合参数公式给出了一套 snubber 电路的快速设计方法,最后以 LM5119 的 EVM 为例给出了 snubber的设计过程和结果。

1、Buck 电路中snubber 的引入和参数计算

1.1、Snubber 电路的引入

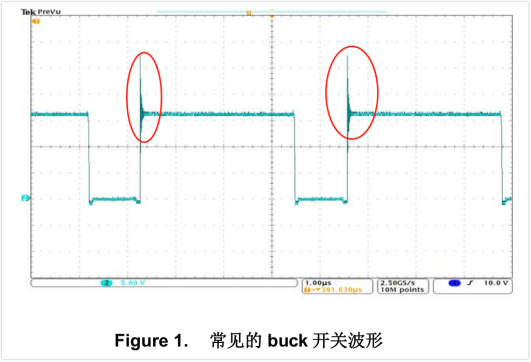

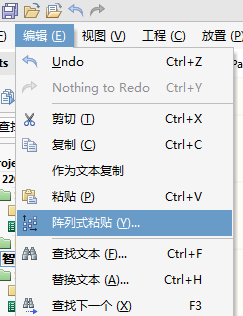

由于寄生参数的存在,开关电源电路在开关动作瞬间会产生开关振铃。Figure 1 为 buck 电路开关节点(两个开关与电感交汇点)的典型波形,可见在上管开通瞬间都有不同程度的振铃。

振铃的存在,可能使得开关管承受的电压超过其耐压值而发生击穿;另一方面,开关振铃为远超开关频率的高频振铃,并伴随很高的 dV/dt,会带来传导和辐射的 EMI 问题,可能会使得终端产品不能通过 EMI 标准测试,更严重时甚至会干扰开关电源自身的信号电路或临近的其他功能电路的正常工作。所以尽可能地抑制开关振铃是开关电源设计中一个很重要的环节。

常见的措施,包括布线的优化减小线路寄生参数;选用二极管反向特性好的器件;降低开关速度;在振铃回路中放置 snubber 等。其中,snubber 是最为常用的手段,特别是在以上其他措施因客观因素的限制而不能达到最佳效果时。Snubber 不仅能改变振铃频率,同时其电容效应会降低开关节点的 dV/dt,从而有效抑制 EMI。

本文以 LM5119 为实例讨论buck 电路的 snubber 的相关问题,但同样的设计思路和方法可以推导到其他非隔离拓扑中。

1.2、包含寄生参数的振铃回路等效

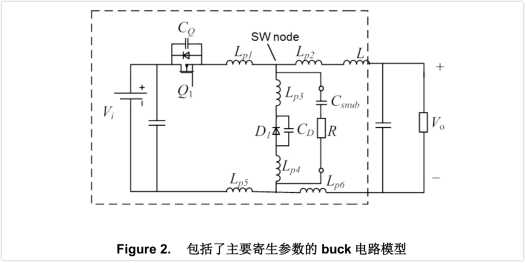

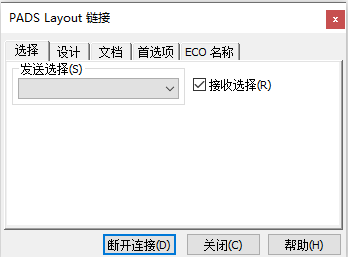

Figure 2 展示了包含主要寄生电感和电容的 buck 电路,RC snubber(R 和 Csnub)放置在开关节点和GND 节点之间。该电路主要用来抑制上管开通瞬间的振铃,而该振铃正是绝大多数过压问题和 EMI 问题的源泉。

首先由于开关过程在极短时间(从数个纳秒至数十个纳秒)完成,在此过程中电感 L 的电流几乎不变,故 L 和 Lp2(包括串联的 Lp6)不参与振铃。

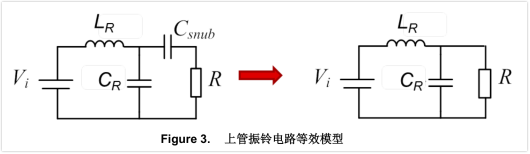

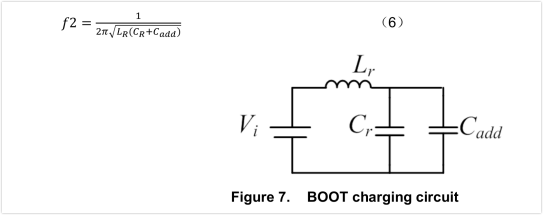

其次,在振铃使得幅值超过 Vi后,上管 MOSFET 的沟道已完全打开,CQ被短路,也不参与振铃。故最终的振铃回路由图 3 左虚线方框中电路组成。该电路可等效成图 3 中 LC 谐振电路,新的 LR和 CR为 Lp1、Lp5,Lp3, Lp4, CD等所有参与振铃的寄生感容的复合值。通常 Snubber 的 Csnub取值在数 nF 以上,在振铃频率 fR(加了 snubber 后)下的阻抗很小。

以Csnub=2.2nF, fR=150MHz 为例,阻抗为 1/(j*2πfR*Csnub)=-0.48jΩ。而 R 一般在数欧姆以上,故 figure 3左可进一步近似等效为 figure 3 右。

1.3、等效模型下的 snubber 参数计算

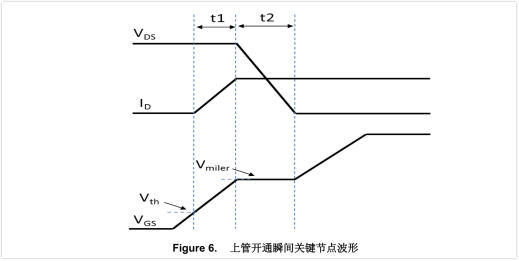

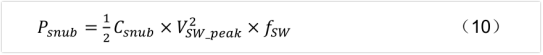

由 figure 3 电路,可得到:

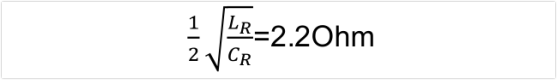

故为使电路电路为阻尼振铃,R 的取值为:

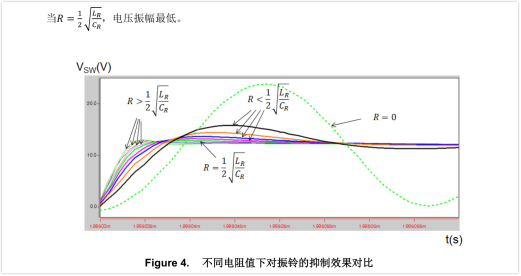

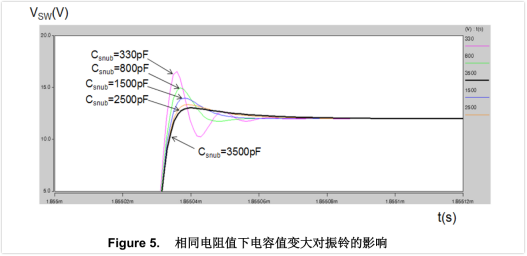

Figure 4 给出了不同电阻值的仿真对比。仿真条件为:Lp1=Lp5=10nH,Lp3=Lp4=2nH, Csnub=10nF,CD=200pF

同时,Csnub越大,在 RC snubber并联到CR后,实际等效的 CR会更大,意味着同样的阻尼电阻对振铃抑制效果越好。

Figure 5 给出了在相同 R(R=2.2Ohm,其他电路寄生参数如前文)下,不同 Csnub的仿真结果。电容越大,抑制振铃振幅效果越好。

而且当电容达到一定程度大小以后,电容的增加给振铃抑制的效果并不显著,比如图 x 中 2500pF 和 3500pF 对应的振幅对比。究其原因,在 RCsnubber 支路,电路电抗为 R 1/(j*2πfR*Csnub),当 C 达到使得 1/(j*2πfR*Csnub)<<>

暂无评论