啥意思,难道老wu要教唆大家剑走偏锋?打工是不可能打工的了?其实老wu这里说的盗铜,指的是 Copper Thieving啦。

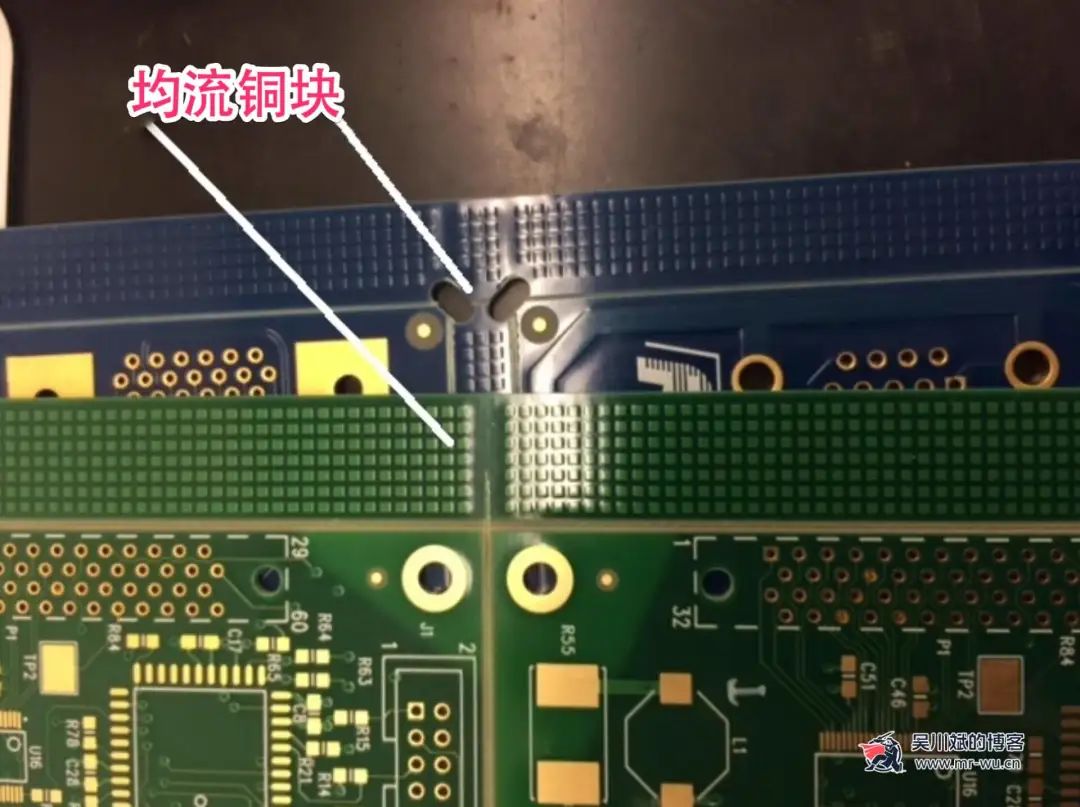

Copper Thieving 字面理解就是具有偷窃行为的铜,行内叫均流块,也称电镀块,指添加在多层PCB外层图形区、PCB装配辅条和制造面板辅条区域的铜平衡块。

Copper Thieving有什么用?在PCB生产过程中在外层电镀工艺这个环节时平衡电镀电流,避免在电镀工序因电流不一致而导致成品铜厚不均匀。也就是在电镀的过程中把电镀电流从铜箔密集区夺过来,让电流分布更平均,也就是避免成品铜厚的不均匀。

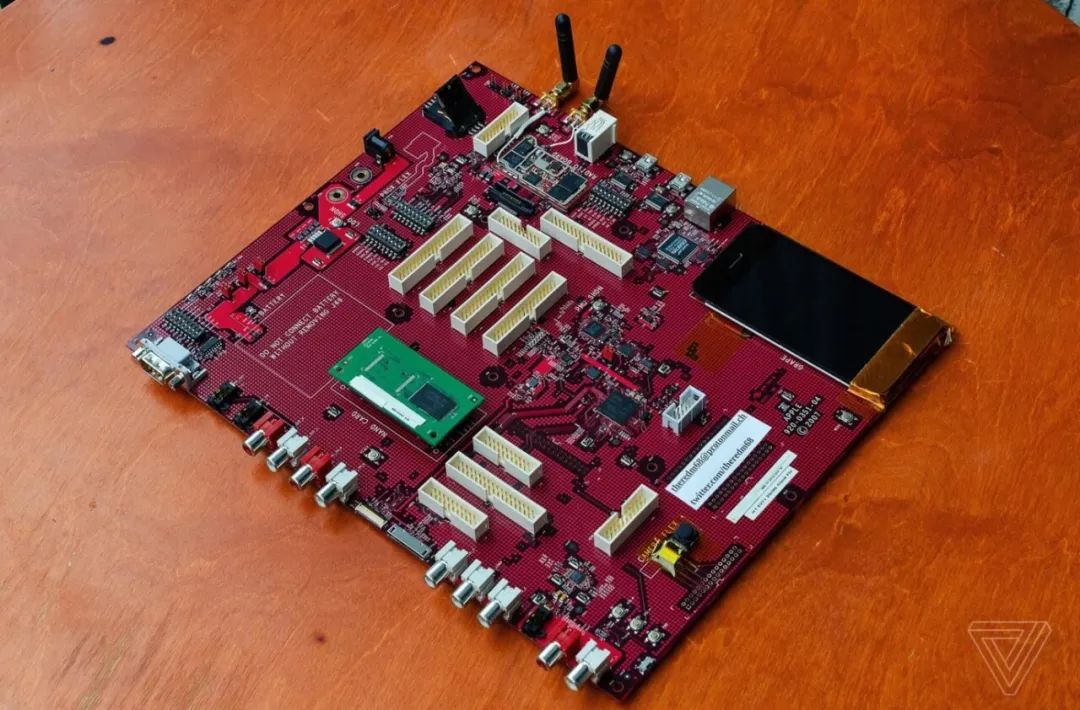

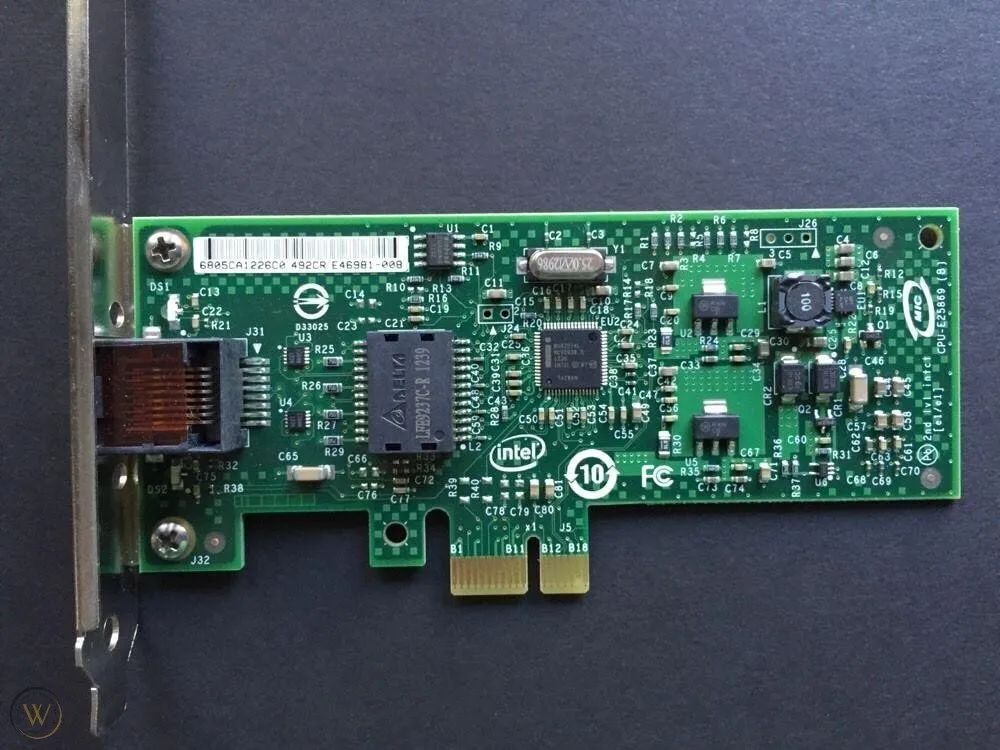

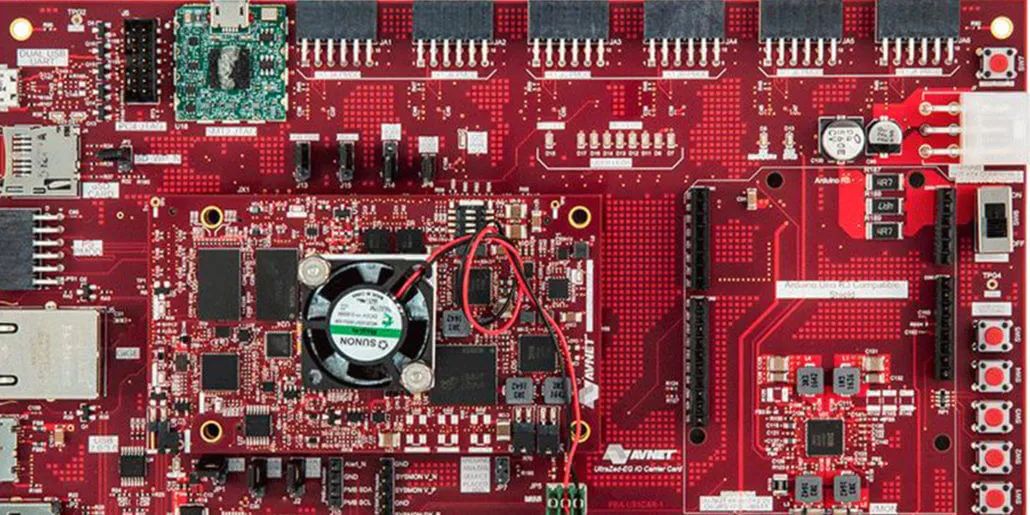

为什么要说这个?源于最近有小伙伴给老wu发来了据说是初代iPhone的原型开发板,板子非常漂亮,特别是其表面被很多小方格铜块所覆盖,非常有艺术气息,一下子就让人联想到了路易威登经典的棋盘格款式。

这些小铜块看起来像是覆铜但又有所不同,它是由许多个非常小的独立方格状铜块组成的,每个铜块都是独立的单体,不与电路板上的其他组件进行电气连接,比如我们所知的,PCB上的大面积铺铜至少要以所关注频率的1/10波长间距打金属化过孔,与PCB上主0V参考平面进行连接。

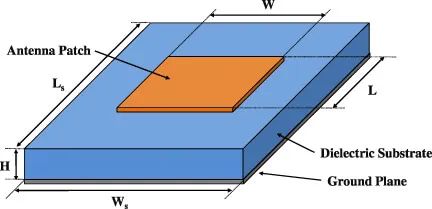

悬空的大面积铜箔,等效于Patch Antenna,如下图这样,板子上的共模电流很容易进入天线对外电磁辐射突突突,造成电磁兼容性问题

大面积铺铜孔打的不够,高阻抗,引起谐振,照样辐射电磁波突突突

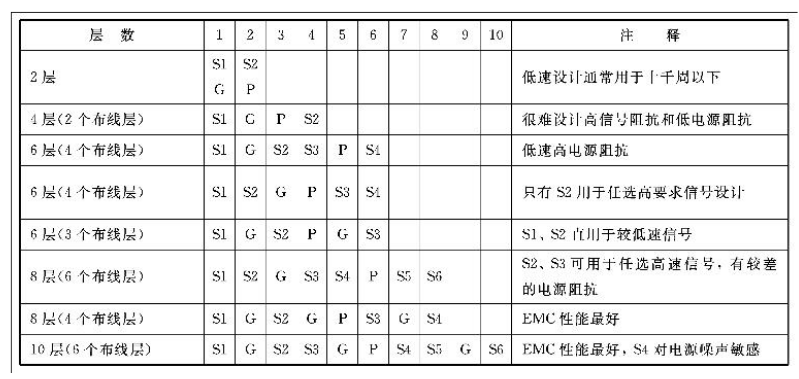

其实,以高速数字信号为主的具有低阻抗回流平面的PCB外层覆铜弊大于利,注意,老wu这里说的是【高速数字信号为主】而又【有低阻抗回流平面】,要注意这个前提,如果是双层板或者高阻抗的模拟电路,覆铜还是很有好处的。

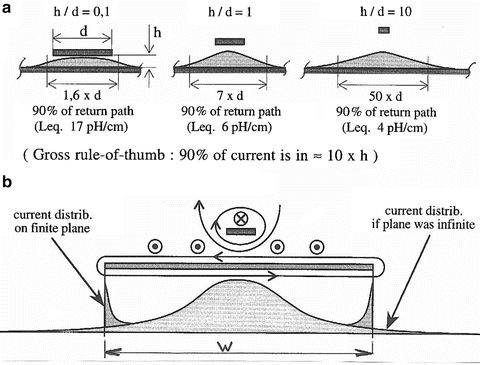

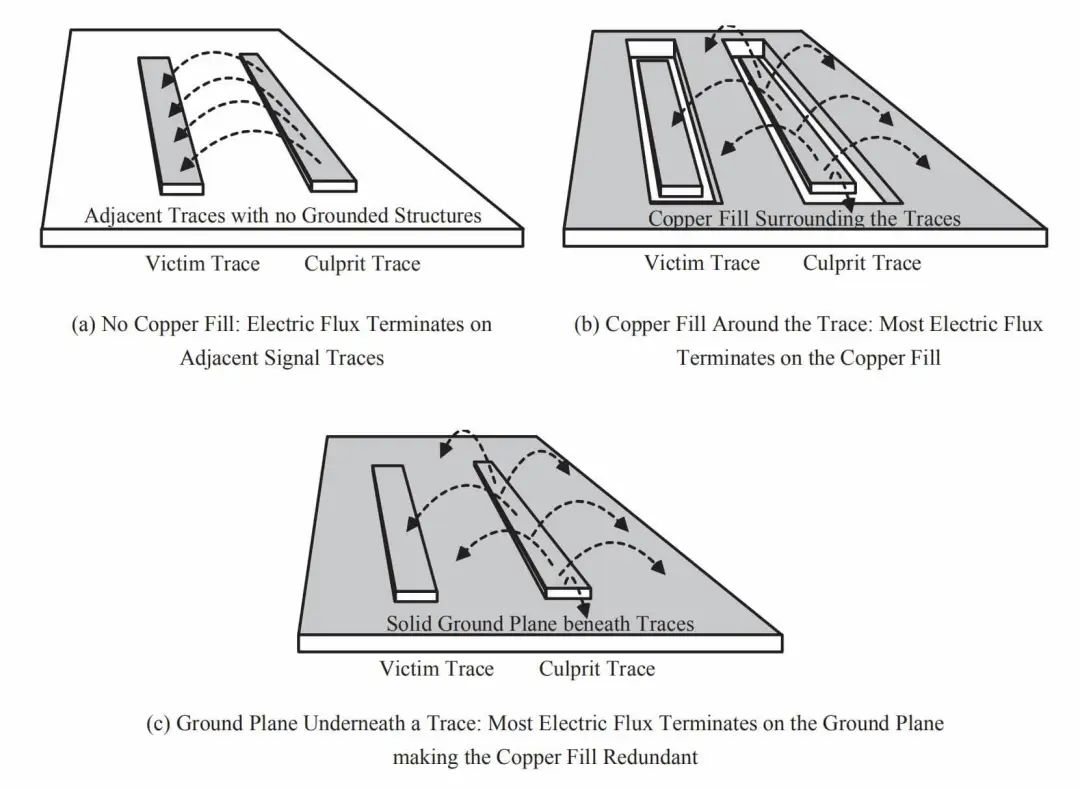

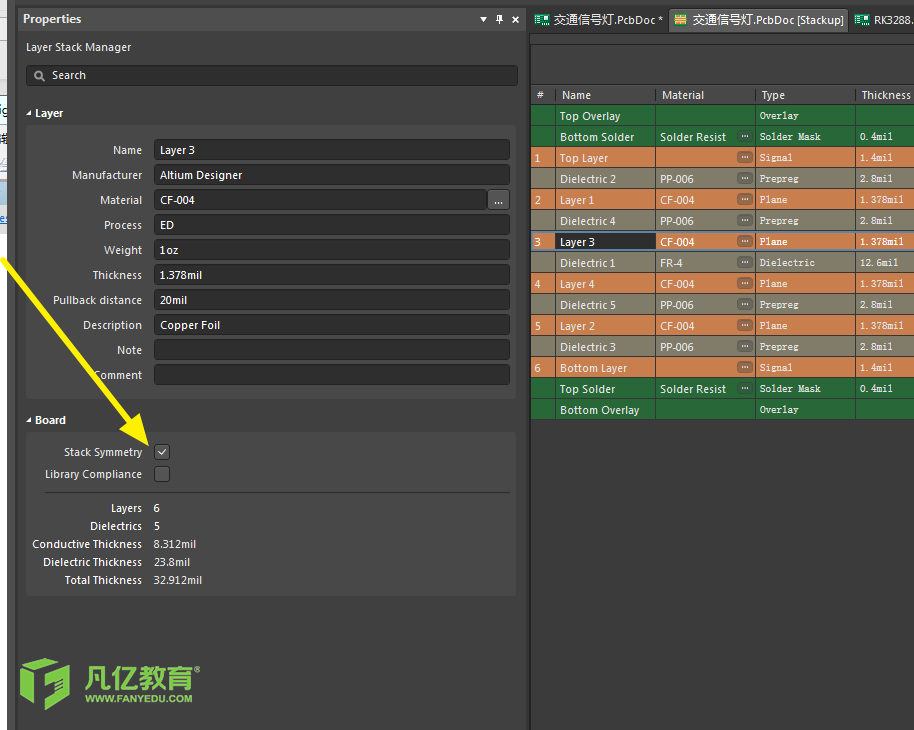

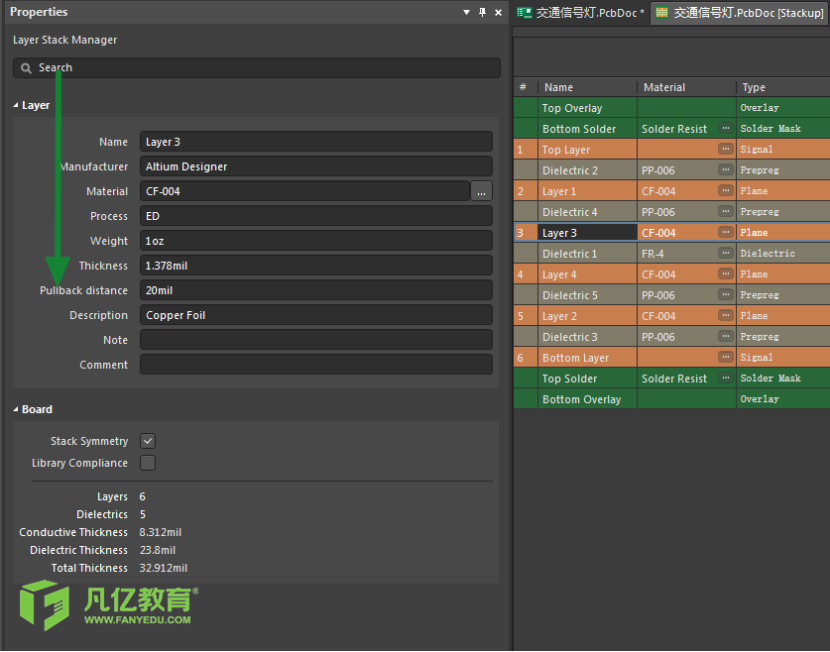

对于具有低阻抗回流平面的多层PCB来说,高数数字信号的回流会直接走阻抗最低的路径而不是直线距离最短从而电阻最小的路径,也就是大部分回流集中于信号对应的参考平面,走线与参考平面的距离H越小,回流电流在参考平面上越集中于与走线对应的区域,换句说话就是回流电流扩散的面积相对较小,可以降低串扰,回流耦合越紧密,越能减少差模辐射。所以,提高表层走线EMC性能的优选方法就是通过合理的叠层结构设计,使高速信号传输线与参考平面尽可能接近,让回流从低阻抗的参考平面走,而不是通过铺铜的方式构造另外的回流路径去弥补,也就是没覆铜他老人家啥事了。要覆铜的话,你还要打金属化过孔与0V参考平面连接,在犄角旮旯的地方,铺铜还容易形成意外的天线。打过孔的话,每个过孔又会挤占本来就很拥挤的内层走线空间,还有主电源/0V参考平面的完整性,本来越来越多的IC引脚和走线换层过孔已经把平面打成筛网了,再加上外层平面补打的那堆孔,对保持主平面的低阻抗越发的不利。同时,铜箔处理不当,在局部区域过于靠近需要控阻抗的传输线,也会造成传输线阻抗突变,在阻抗不连续的地方产生信号反射引发信号完整性问题。

当然,如果是外层有相对完整的铜箔,这些铜箔可以起到一定的屏蔽作用,或者可以提高PCB的层间电容,对于提升EMC性能会有所帮助,但对于高数数字信号为主的情况,外层布满了元器件和扇出过孔,很难形成完整平面的。

对于两层板,走线与它的参考平面距离太远了,同时,0V参考平面还要走线,很难保证平面的完整,这时候板子空余的地方铺铜并且多打孔与0V参考连接,构造低阻抗回流路径,对于提升EMC性能还是很有好处的。

对于有低阻抗参考平面的高数数字信号走线区域,老wu是不在外层铺铜的,但是,如果外层的残铜率太低的话,比如主控和周边的DRAM等BGA区域,相对铜箔密度较密,其它区域铜含量相对较少,不均匀的铜分布率在电镀工艺环节,BGA区域流经的电流密度过大,造成电镀成品铜厚不均匀,比如差分线,铜厚不均匀会对阻抗控制有不利影响,BGA引脚上的铜厚差异大,也会对SMT的良率有影响等等。

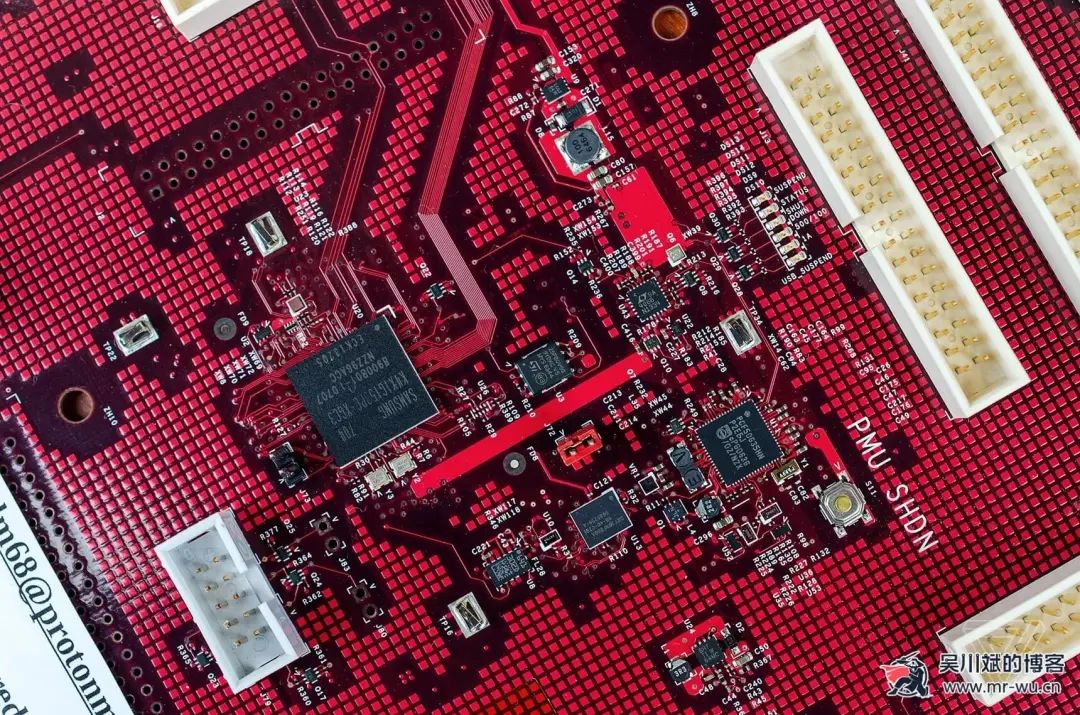

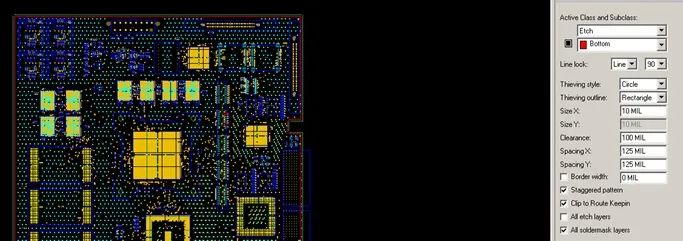

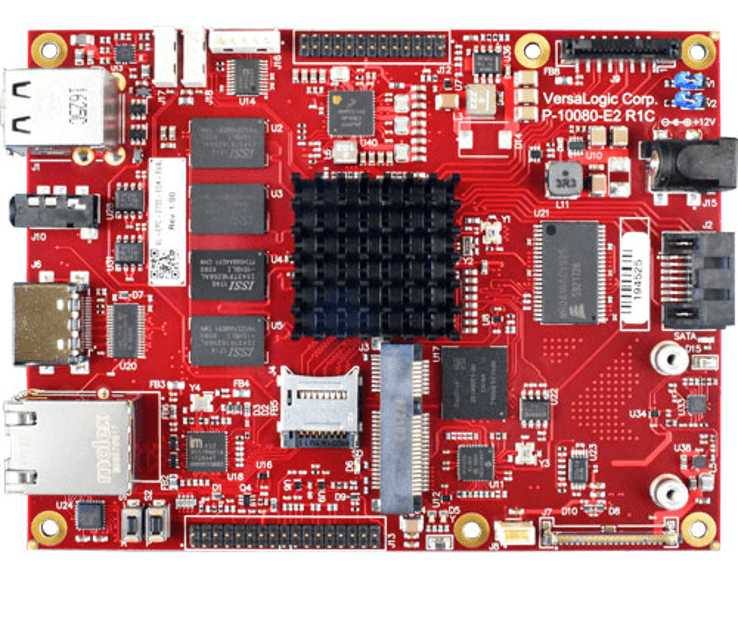

解决办法就是改善铜箔分布的疏密平衡,这种棋格状的小铜块就是不错的选择,当然,也有的是小圆点形状的,它的每个单体在物理尺寸上都远小于波长的1/4,很难形成有效的辐射天线,不用打过孔与0V参考平面连接,不用挤占拥挤的内层走线空间,唯一要注意的是Copper Thieving的下方不要有阻抗控制线,这些铜块会造成阻抗不连续。当然,也不要太靠近需要做ESD防护的地方。

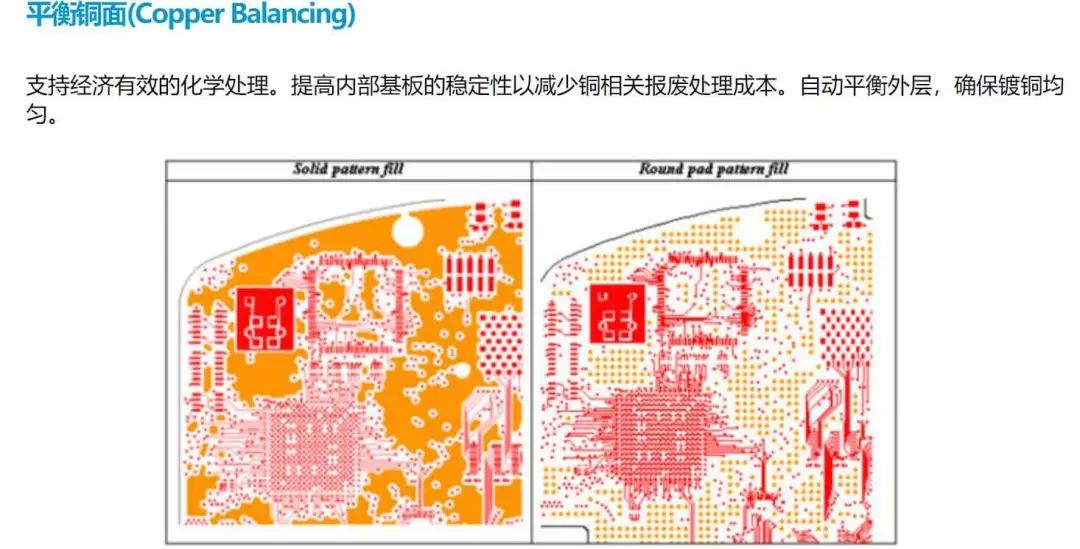

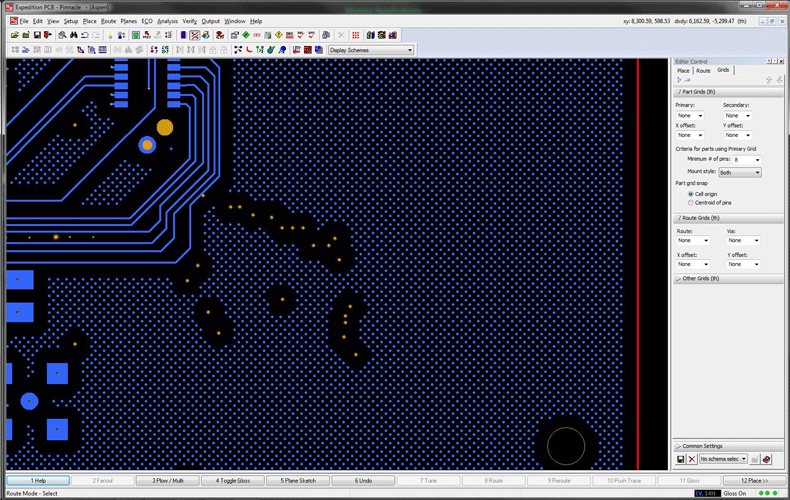

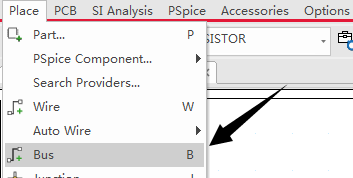

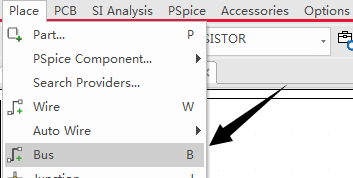

板厂会根据CAM软件计算出的残铜率,帮你加上平衡铜块然后发你确认,这时就要注意检查这些铜块是否会对阻抗造成不良影响,当然,最好是自己添加,避免与板厂工艺人员沟通出现偏差,像 cadence allegro 16.6以后的版本,mentor PADS Professional等主流EDA软件,都加入了添加Copper Thieving的功能。

还有一点要补充的是,Copper Thieving特指的是在外层的铜块,Thieving就是要盗取电镀电流使得外层铜厚电镀的更均匀,同样的铜块用于内层,就没有Thieving的作用啦,这时就是平衡铜,避免内层压合时内层树脂区域面积过大,造成空洞或者起泡,还有就是平衡不同层铜箔受热时产生的机械应力差。铜块依然是那么个铜块,只是起的作用不一样。

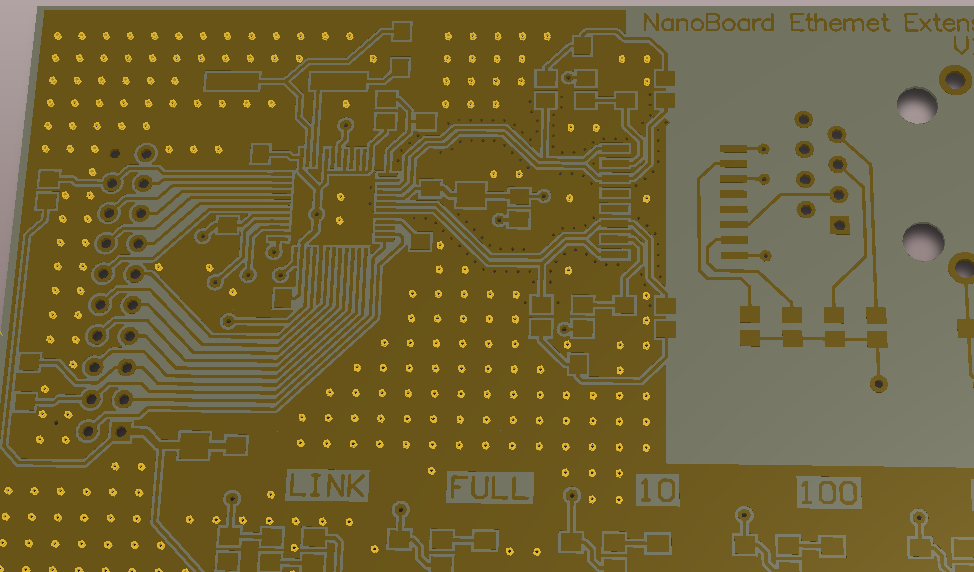

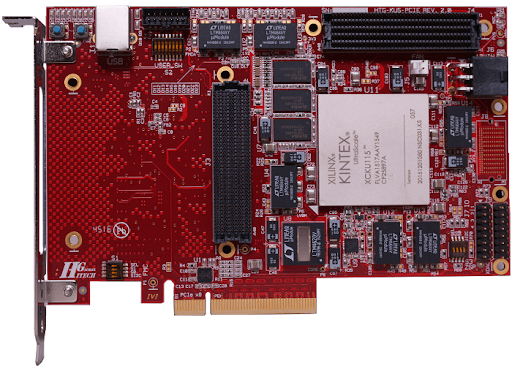

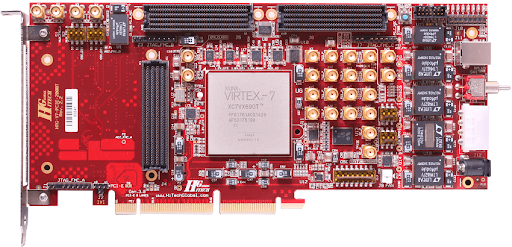

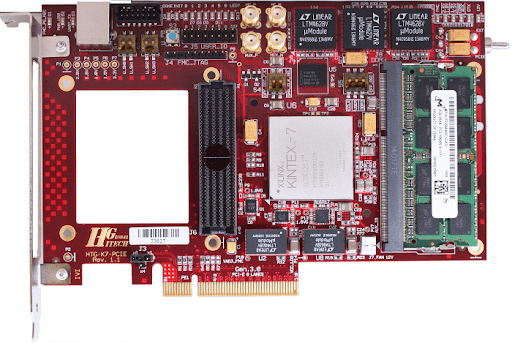

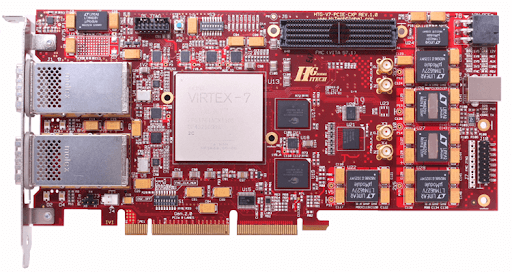

下边贴一些在外层应用Copper Thieving的图例,欣赏一下在PCB上盗铜的艺术

暂无评论