【摘要】

在某单板上,由于CPU芯片GMII接口的电源上只加了磁珠滤波,引起的故障:在网口通信时,当通信包的内容为低速码型(全0全1)时,没有丢包;当更改为伪随机包时(码型速率快),丢包严重。最终在磁珠后加电容,问题解决。

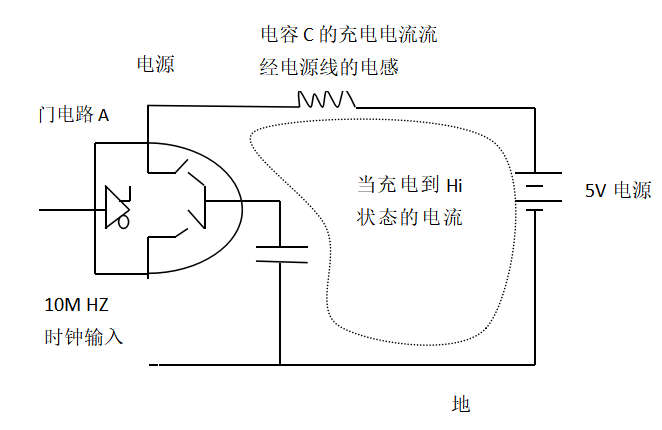

原因分析: 从电源的输出到所供电的逻辑电路之间的引线可能包括值得重视的阻抗,这个阻抗导致了一个与工作电流成正比的压降。其中,电源线上的电感产生的影响比电阻更严重。快速变化的电流(高速率码型)通过电源线的电感引起电源和所供电的逻辑电路之间的电压偏移。举例说明一下布线电感问题有多糟糕。图1的电路驱动一个大的容性负载。门电路A电源引脚的供电电流需求由每隔100ns的时钟高电平组成。时钟的高电平与门电路每次驱动容性负载为HI状态时相对应。驱动HI状态操作的电流路径如虚线所示。

图1 电源供电分配线的电感假设门电路的上升时间为5ns,则驱动器的最大dI/dt: 其中,△V=5V(驱动电压)

其中,△V=5V(驱动电压)

Tr10%-90%=5ns(驱动上升时间)C1=50pf(负载电容)

下一步,计算电源供电线路的电感:

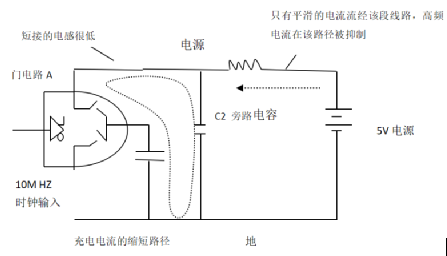

其中,X=10in(线路的长度) H=0.1in(线路之间的平均间距) D=0.04in L=电感/nH 最后得到噪声电压=(1.5X107)*(164*10-9)=2.5V噪声真的这么大吗?实际上,问题可能更严重。因为我们的假设并不精确。假设上升时间等于1ns,在这个电路中,电源供电电感非常大,以至于当门电路A试图驱动Hi时,该电路板电源的供电输入下降到接近零,随着电容C1经过电源线电感的充电,电压慢慢升起。当电源的供电下降的时候,门电路A在运行,或者进入振荡状态。 解决的办法是加如图2所示的旁路电容,如果电容C2的阻抗比电源的布线阻抗低,变化的电流将会流过电容而不是布线。当转换为Hi状态的时候,门电路A所经受的电源下降是C2阻抗的函数,而不是电源布线阻抗的函数。

图2 旁路电容在电源线中平滑电流的流动

总结:1.电源在低频时提供低的阻抗,局部的旁路电容在较高的频率上提供低的阻抗;2.对于可调电源输出(包含反馈端),反馈端会为电源提供在分配线远端测量到的电压,然后电源就能通过调整输出来适应布线引起的阻抗,而通常我们布线时,反馈电阻是放在电源近端的;3.旁路电容要靠近管脚放置。

暂无评论