凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片工程师如何应对PCB串扰问题?

随着电子产品向小型化、高速化趋势的加速发展,PCB设计中的串扰问题日益凸显,成为影响产品性能与可靠性的关键因素。串扰,即信号间的相互干扰,主要由电磁场耦合引起,对信号完整性构成严重威胁。工程师在应对这一问题时,需采取一系列具体而有效的措施,以确保电路的稳定运行。以下是几个关键策略。

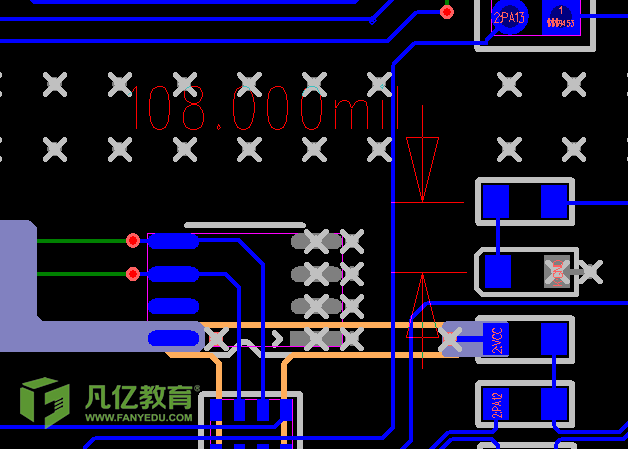

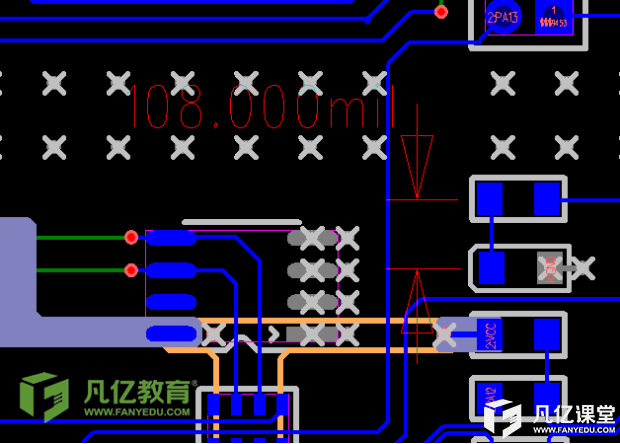

1、增大线间距

直接且有效地减少线间电容和电感耦合,是降低串扰的首要方法。在布局时,应尽可能增大信号线之间的物理距离,特别是在高频信号线之间,以削弱电磁场耦合效应。

2、优化信号层与参考层布局

确保信号层与其对应的参考层(如地平面)紧密相邻,形成低阻抗回路,有助于减少辐射和接收到的串扰。同时,合理设计参考层的完整性,避免分割或中断,以维持良好的回流路径。

3、垂直布线

当不同层的信号线存在潜在干扰时,采用垂直布线策略。这种布局方式下,电场和磁场方向相互垂直,从而显著降低层间串扰。通过合理规划层叠结构,实现信号线的正交布局。

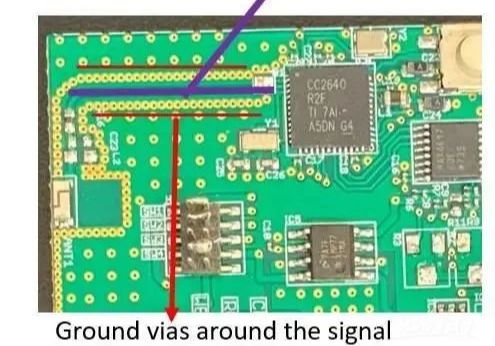

4、使用防护布线(Guard Traces)

在关键信号线周围布置防护布线,形成屏蔽层,以隔离外部干扰。确保防护布线宽度足够,并通过过孔与参考层短接,以提供连续的屏蔽效果。

5、控制信号上升/下降时间

较快的信号边沿会加剧串扰现象。通过调整驱动电路或使用缓冲器,适当延长信号的上升/下降时间,可以降低高频分量,减少串扰的发生。

6、仿真验证

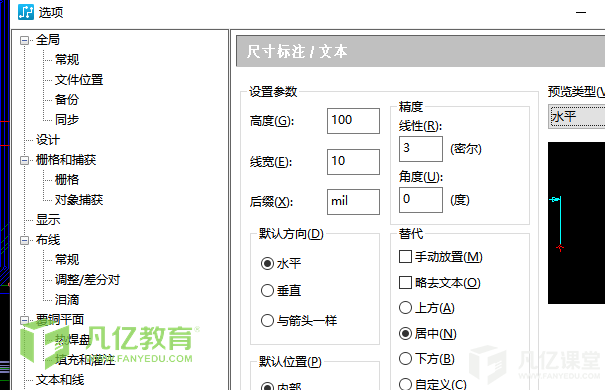

利用专业的PCB仿真软件进行信号完整性分析,提前发现并解决潜在的串扰问题。通过模拟不同条件下的信号传输情况,优化布线策略和参数设置。

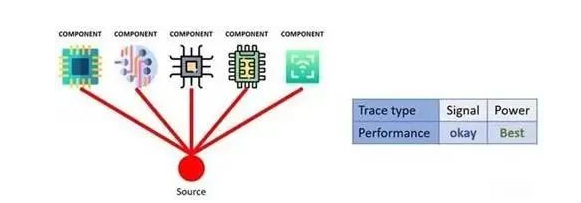

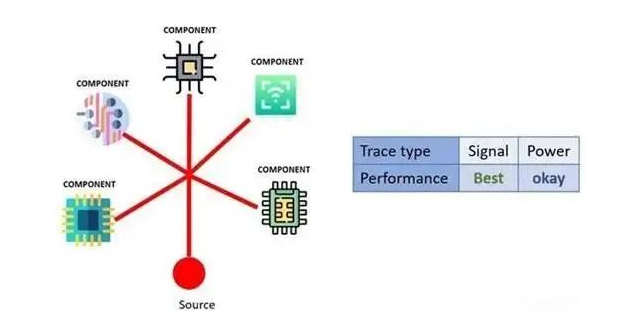

7、实施去耦和滤波

在电源和地之间添加去耦电容,以及在信号线上使用滤波器,可以有效抑制高频噪声和串扰信号,提高信号质量。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论