本文要点

理解电路中的杂散电容。

了解杂散电容如何影响电子电路。

探索减少电路中杂散电容的策略。

杂散电容就像被遗弃的宠物流浪在街道和巷子里一样,它们潜伏在电路中。本文将了解电子电路中的杂散电容是如何产生的、如何影响电路的性能,以及如何在设计中减少杂散电容。

什么是杂散电容?

基础电子学对电容的定义是:在具有不同电压电位的两个端点上积累的电荷的测量值。这也是电容器的制造原理。杂散电容是指电路或非电容性元件中出现了预期之外的电荷。

就像流浪的狗或猫一样,杂散电容只是由于环境的原因而恰好出现在那里。在电路上制造杂散电容是很容易的。所需的只是两个导电元件,它们在绝缘体上足够封闭,因而表现得像一个电容器。

杂散电容就像是电路上存在着看不见的电容。

杂散电容可能存在于电感、晶体管或二极管等元件上。即使是 PCB 上的两个平行导体,也总会有一些杂散电容存在。我们也会在导体中发现相对于接地面的杂散电容。

在书面上,杂散电容用公式 C = Q/V 表示,用于测量微分电位上积累的电荷。在 PCB 设计中,我们会发现公式 C= ϵA/D,体现了绝缘体的介电常数、面积和导体之间的距离与电容值的关系。

杂散电容是否会影响电路性能?

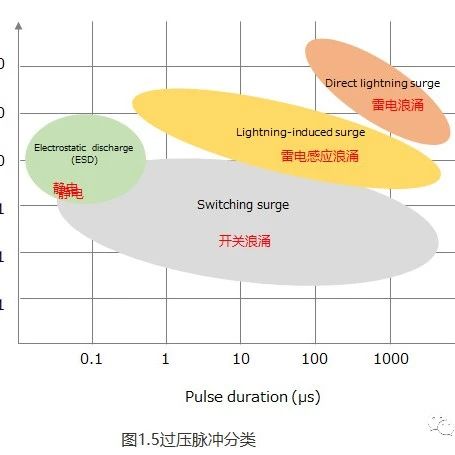

大多数流浪的动物通常没有什么危害。杂散电容的影响则取决于频率。如果在电路上放置一个电容器,在低频下,电容器会造成开路。随着频率的增加,电容器会逐渐允许电流通过。

杂散电容的影响在高频率下十分明显。

因此,如果我们正在进行低频设计,杂散电容并不会造成严重问题。例如,一个简单的 LED 闪光灯不会受到杂散电容的影响。当设计涉及到高频时,问题会悄然而至,这可能会大大降低杂散电容的电抗。

在高频率下,具有杂散电容的元件往往像短路或虚拟电阻一样。杂散电容的影响是运算放大器设计中一个难题,特别是在放大器的输入和输出之间。杂散电容创造了一个反馈路径,会不准确地增加增益和改变峰值频率。

在传输线中,导体之间的杂散电容会导致传输损失。这意味着传输功率和信号质量会下降。杂散电容也会在导体和相邻的接地平面之间产生,这将导致高频率下出现信号完整性问题。多余的电容也会造成串扰和 EMI 噪声。

如何减少杂散电容?

我们并非对杂散电容束手无策。虽然杂散电容不能完全消除,但有一些方法可以将电路中的杂散电容降到最低。

1. 让导体彼此分开

无论是 PCB 上的走线还是并排放置的电缆,都可以通过增加它们之间的距离来减少杂散电容。电容与距离成反比,这是减少杂散电容的一条重要原则。

让铜走线彼此分开可以将杂散电容降到最低。

2. 屏蔽导体

如果担心相邻的走线会产生杂散电容,可以在走线之间增加一条接地的铜线。该铜线可以发挥屏蔽作用,进而防止电荷堆积。

3. 减少走线宽度

当导体的横截面积增加时,电容也会增加。因此,要尽量减少走线宽度,尤其是传导高频信号的走线。

4. 移除内层接地平面

大片的内层接地平面可能有助于散热和降低 EMI,但却不利于减少杂散电容。在为设计添加接地平面时,一定要考虑到这一点。

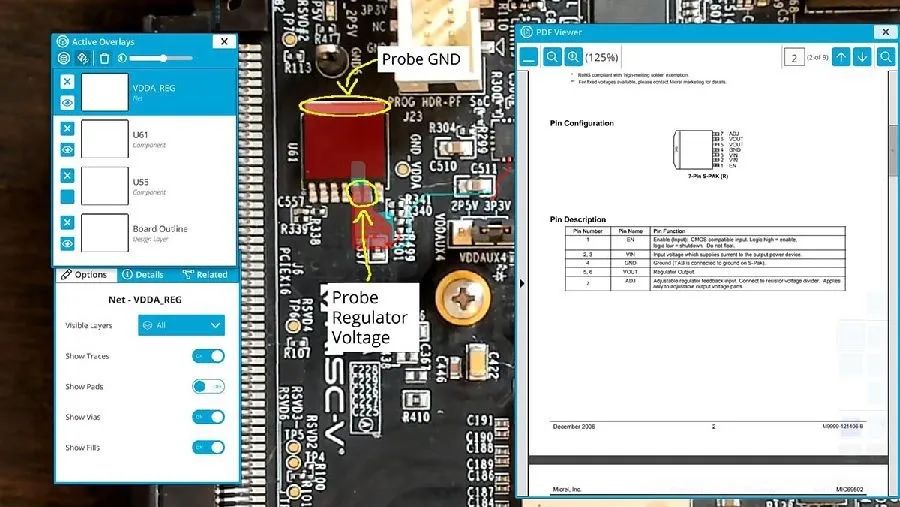

借助合适的 PCB 设计软件,可以确保电路设计不受杂散电容的影响。通过使用 inspectAR™工具,利用增强现实(AR)技术以交互性的方式评估和改进 PCB,轻松准确地进行 PCB 检查、调试、返工和组装。

inspectAR软件中直接将 AR 叠层对应在 PCBA物理板上

上图显示了inspectAR 软件中 AR 叠层制造的 PCBA物理板的交互。利用AR技术,工程师或制造技术人员可以在制造过程中的任何时候将单个器件、走线、子电路或整个电路板与设计规格进行比较,并随时查看技术手册、添加留言、注释。

暂无评论