凡亿教育-媛媛

凡事用心,一起进步打开APP

公司名片PCB时钟如何布线?记住这些要点!

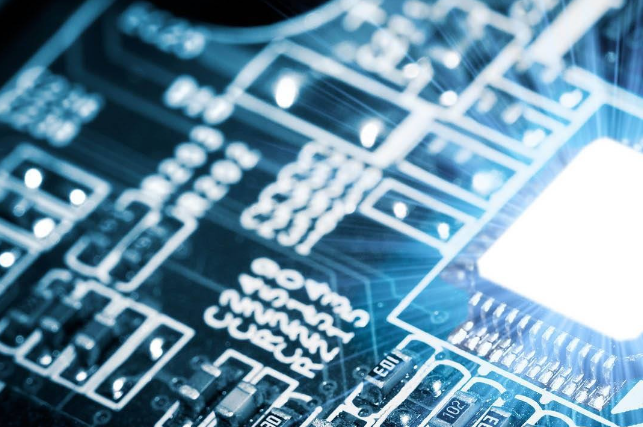

在PCB设计中,时钟信号是极为关键的敏感信号,若设置不当很容易干扰到系统稳定,电磁干扰更加严重。所以工程师必须慎重对待时钟信号,遵循其高频特性和对时序的严格要求,确保其布局布线顺利。

1、减少过孔数量

时钟线上应尽量减少过孔的使用,因为过孔会增加信号路径的阻抗不连续性,可能会导致信号反射和辐射干扰。

2、避免并行布线

时钟线应避免与其他高速信号线或敏感信号线并行走线,这样可以降低串扰和耦合噪声。

3、远离一般信号线

时钟线应布局在远离一般信号线的区域,特别是模拟信号线和低速数据线,减少对它们的干扰。

4、远离电源部分

时钟线应避开PCB板上的电源模块和电源走线,放置电源噪声对时钟信号的干扰,同时也减少时钟信号对电源网络的辐射,

5、时钟芯片下方铺铜

若板上有专门的时钟发生芯片,其下方不应有走线,而应铺设完整的接地铜层,以提供良好的电磁屏蔽效果。对于需要更高隔离度的场合,可考虑对时钟芯片区域进行专门的地层分割(割地)。

6、晶振下方铺铜隔离

多数芯片使用的参考晶体振荡器(晶振)下方同样不应有走线,应铺铜进行隔离,以减少对晶振信号的干扰和保障振荡的稳定性。

7、使用差分时钟

在允许情况下,采用差分时钟信号传输方式,可有效抵抗外界干扰,提高信号完整性和抗干扰能力。

8、等长布线

对于需要同步的时钟信号,应采用登场布线策略,确保时钟信号到达各接收点的时间差最小,维持系统的时序一致性。

9、考虑信号衰减

长距离时钟线需考虑信号衰减问题,必要时可采用缓冲器或驱动器增强信号强度。

10、遵循设计规则

严格遵守PCB设计软件的时钟信号布线规则和制造商的推荐布线规范,确保设计满足性能要求和工艺标准。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论