某产品EMC辐射骚扰测试超标,通过近远场扫描配合定位分析,逐步找出骚扰源、传播路径,最终通过修改 PCB 走线切断传播路径解决此问题。

1 故障现象

某产品在进行 EMC 研发摸底测试时发现,整机辐射骚扰垂直方向测试超标,超标点频率为 150M Hz,同时伴有 20M Hz 间隔的脉冲骚扰。

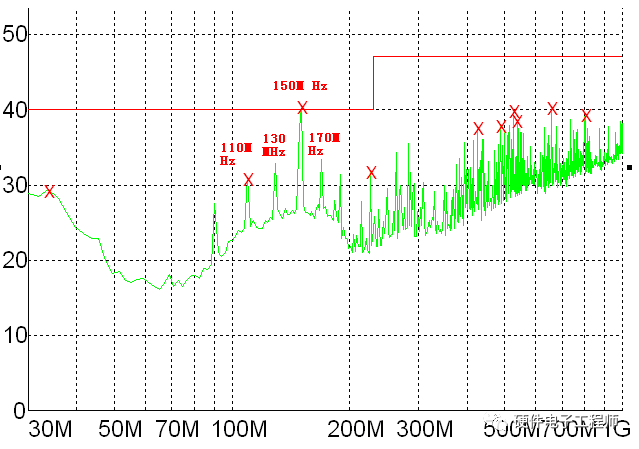

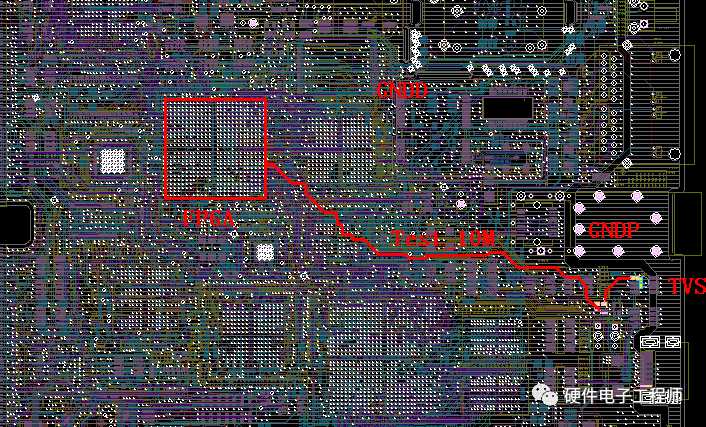

在实验室辐射骚扰的远场扫描图(垂直方向)如下图 1 所示:

图 1 某产品辐射骚扰远场扫描图(垂直)

2 故障分析

首先通过将系统单板逐一下电后扫描的排除法将 150MHz 频点骚扰源定位在系统某单板上,该单板(后文简称 A 单板)在系统中完成的功能为时钟及通信控制。A 单板对外接口主要有以太网接口、光口和 HDMI 接口,其中 HDMI 接口为调试与时钟级联接口,辐射骚扰测试时不外接线缆。以太网接口测试时使用屏蔽网线通过电波暗室隔离底盘和辅助设备相连。拔掉A 单板网线重新进行测试,测试结果通过。但是从测试数据中可以看出,150M Hz 的骚扰频点仍然存在,只是幅值降低了 6.8dB。

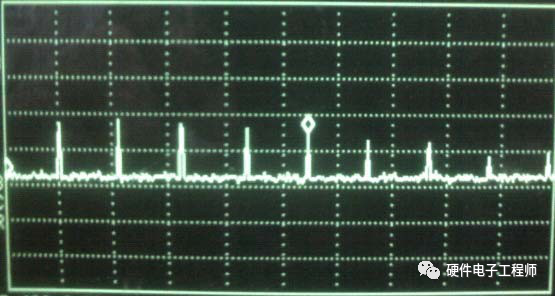

通过频谱分析仪搭配近场探头对单板进行近场扫描,发现单板面板处靠近 HDMI 口和以太网口附近 150MHz 的骚扰较强,同时单板保护地和屏蔽网线上也有较大的骚扰。将频谱仪扫描频段设为从 1MHz 到 200MHz 展开,发现骚扰从 10MHz 开始出现,并且是 10MHz 的奇次谐波(10、30、50...130、150、170)。这些频点和图 1 远场扫描100M Hz~200M Hz之间的骚扰频点完全吻合。近场扫描图如下图 2 所示:

图 2 该单板网口附近近场扫描图

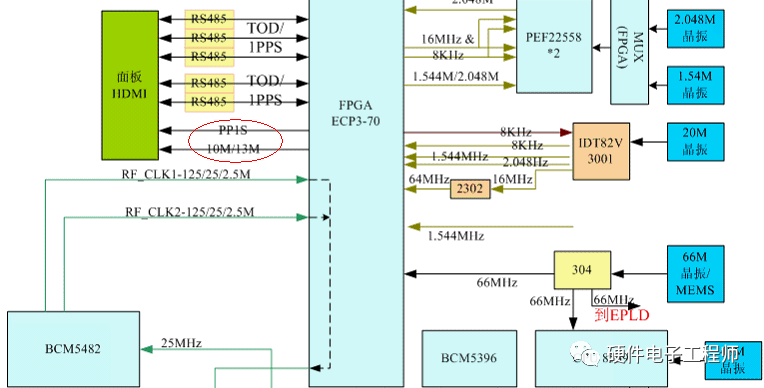

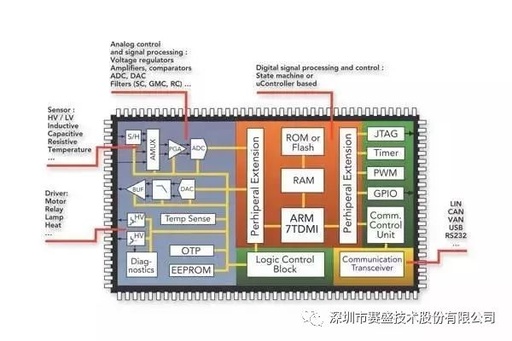

分析该单板的时钟拓扑,单板上电后,FPGA 逻辑控制 10MHz 基准时钟输出到 HDMI 接口作为调试和级联输出(如下图 3)。从近场扫描数据分析,骚扰源极有可能是单板上的这个 10M 时钟输出。为了进一步确认骚扰是由该时钟引起,我们通过修改单板逻辑将输出到HDMI 口的 10M 时钟关闭,近场扫描 150MHz 骚扰完全消失。问题定位到此骚扰源得到具体确认。

图 3 A 单板时钟拓扑图(部分)

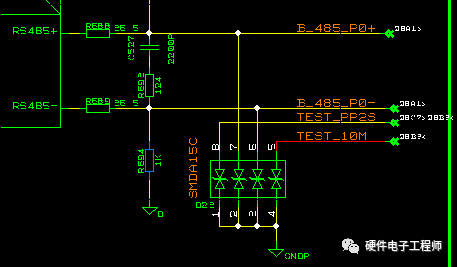

10M 时钟骚扰如何通过网线辐射出来?查看单板原理图,为了对 HDMI 接口信号进行静电防护,10M_TEST 时钟信号输出到外部时增加了一个对保护地的 TVS(如下图 4 所示)。该 TVS 参数为截止电压 VRWM=15.0V, 击穿电压 VBR=16.7V, 结电容 C0=80pF。

图4 A单板HDMI 10M_TEST 时钟电路

分析 A 单板 PCB(如下图 5),Test_10M 时钟从 FPGA 出来后通过内层走线引到 HDMI接口,途中经过 TVS 进行静电防护,该 TVS 接单板保护地。单板保护地和数字地隔离,保护地靠近单板板边及接口,为一狭长区域。数字地为一完整地平面,FPGA 参考地采用数字地。

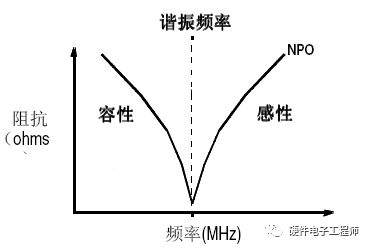

图5 A单板10M 时钟骚扰传播路径 根据傅立叶(M.Fourier)分析原理证明,任何重复的波形都可以分解为含有基波频率和一系列为基波倍数谐波的正弦波分量。 根据傅里叶公式 f(t)= A0/2 A1cos(ω1t ψ1) A2cos(2ω2t ψ2) A3cos(3ω3t ψ3) … Ancos(ωnt ψn) …展开,10M Hz 时钟基频会产生不同分量的高次谐波。从近场扫描数据来看,情况也是如此。 同时我们知道,电容在其谐振频率点具有阻抗最小的特性(如下图 6 所示)。如果 10M 时钟的产生的高频谐波分量频率位于 TVS 结电容的谐振频率点附近,则谐波骚扰电流将通过 TVS 结电容,则会形成上图 5 所示的 FPGA-TEST_10M-TVS-GNDP-FPGA 的回流路径。当单板插入屏蔽网线后测试,有一部分共模骚扰电流将流过网线屏蔽层,形成天线效应造成辐射骚扰测试超标。为了验证此想法,将 TEST_10M 时钟对保护地的 TVS 去除,插上网线后在暗室远场扫描,测试结果通过,150M 频点完全消失。

图 6 理想电容的频率特性

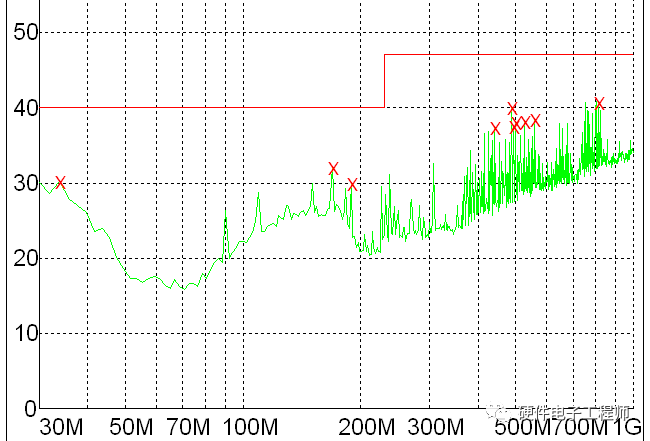

3 故障解决 EMC 的三要素为骚扰源、传播路径和敏感受体。骚扰源和传播路径得到确认后,整改的措施就变得简单起来。我们从传播路径入手,将 TEST_10M 时钟的 TVS 由保护地接到数字地,通过这样改变了骚扰电流的回流路径:FPGA-TEST_10M-GNDD-FPGA。骚扰电流不能再通过保护地流入到外接屏蔽线缆。经过上面整改措施后,整机的辐射骚扰结果得到了非常有效的改善,PCB 改动后的远场测试结果如下图 7 所示(仅列出之前不通过的垂直方向,水平方向经测试一直可以通过)。同时对改动后的单板进行了接口静电放电和浪涌试验,达到的指标和未改动前一致,保证 PCB 改动对 EMC 抗扰设计没有影响。

图7 整改后的系统远场扫描图(垂直)

图7 整改后的系统远场扫描图(垂直)

4 总结 上面的案例分析和解决过程,总结出了以下几点经验:(1)PCB 设计时注意地平面的完整性,同时尽量避免设计成狭长形状;(2)TVS 结电容对时钟信号产生的高频谐波电流可能形成通路,在设计时需要注意它的接地 ;

暂无评论