简介

单光子雪崩二极管(SPAD)凭借其在近红外领域的高灵敏度和高速度,已成为飞行时间测量、面部识别和遥测等应用中不可或缺的光电探测器。光子探测概率(PDP)是 SPAD 器件的关键性能指标之一,它代表了 SPAD 的灵敏度,被定义为被吸收的入射光子产生雪崩事件的概率。

在本文中将探讨创新方法,以提高集成到全贫化硅绝缘体(FD-SOI)CMOS 技术中的 SPAD 的 PDP。通过对光敏区上方的浅沟槽隔离(STI)层进行纳米结构处理,可以产生建设性干扰,从而提高正面照明的光灵敏度。

SPAD FD-SOI 结构和建设性干扰

SPAD FD-SOI 在埋入式氧化物(BOX)层下面实现,而电子逻辑电路则插入到 BOX 层上面的薄硅层中,从而为背面照明(BSI)提供了一个固有的三维堆栈和更高的填充因子。然而,对于正面照明(FSI)而言,BEOL 层的存在会对透光率产生不利影响。

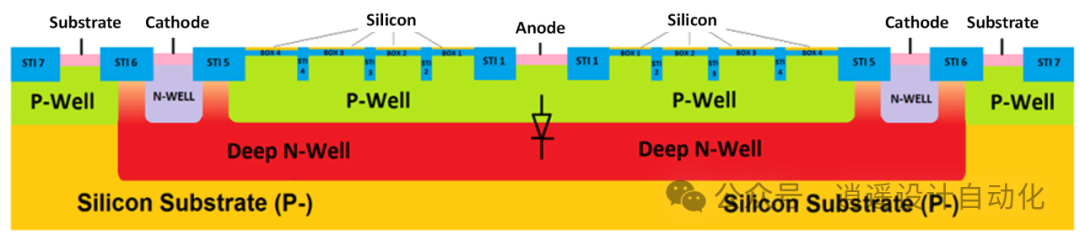

为了改善 FSI 的 PDP,可以利用 SPAD 单元中因技术设计规则而存在的 STI 沟槽。通过优化 STI 层布局(尺寸和周期),我们创建了一个光子晶体层(衍射光栅),它能产生建设性干扰效应,并在雪崩触发概率最高的空间电荷区(SCR)产生最大干扰。图 1 展示了 SPAD FD-SOI 的横截面示意图和 STI 图案化的建设性干涉概念。

图 1. 单个 SPAD FD-SOI 的截面示意图。STI 纳米结构优化

图 1. 单个 SPAD FD-SOI 的截面示意图。STI 纳米结构优化

优化过程包括两个步骤:找到 STI 图案的最佳填充因子 (FF),以最大限度地提高透光率;提取最佳空间周期,以实现 SCR 中的建设性干涉。

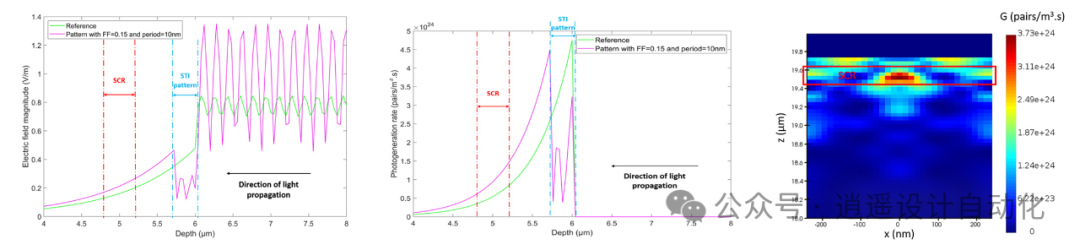

第一步,模拟特定波长下的各种 FF 值,以确定与参考结构相比,图案化 STI 的抗反射效果。图 2 显示了电场幅度和光生成率的曲线,表明图案化 STI 具有显著的抗反射效果。

图 2 比较了无图案参考 SPAD 和填充因子 (FF) 为 0.15、周期为 10 纳米的图案 SPAD,显示了 FF 为 0.15、周期为 0.48 微米时的电场幅值剖面图(左)、光发电率剖面图(中)和光发电率制图(右)。第二步的重点是优化图案周期,以定位 SCR 中的最大干扰。我们进行了无数次模拟,改变每个 FF 值的图案周期。图 2 展示了周期图案的光生成率,清楚地显示了图案的衍射效应和 SCR 中热点的存在。

图 2 比较了无图案参考 SPAD 和填充因子 (FF) 为 0.15、周期为 10 纳米的图案 SPAD,显示了 FF 为 0.15、周期为 0.48 微米时的电场幅值剖面图(左)、光发电率剖面图(中)和光发电率制图(右)。第二步的重点是优化图案周期,以定位 SCR 中的最大干扰。我们进行了无数次模拟,改变每个 FF 值的图案周期。图 2 展示了周期图案的光生成率,清楚地显示了图案的衍射效应和 SCR 中热点的存在。

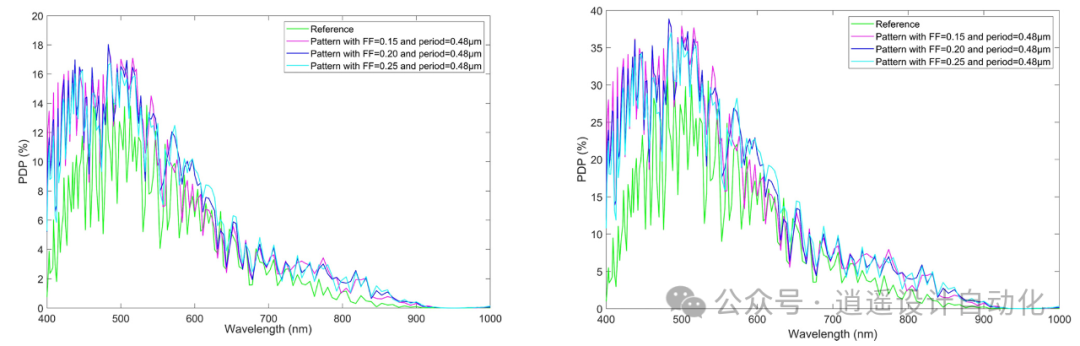

这些模拟随后扩展到更大的波长范围(400-1000 nm),以研究可见光到近红外线的改善情况。图 3 显示了不同过剩电压下的 PDP 曲线,显示出在较短和较长的波长下,PDP 有明显的相对改善,在特定波长下的相对增益可能达到 700%,而在所考虑的波长范围内,平均相对增益超过 100%。

图 3 显示了参考和图案化 SPAD 在 0.6 V(左)和 1.5 V(右)过剩电压下的光子探测概率 (PDP)。测试芯片展示

图 3 显示了参考和图案化 SPAD 在 0.6 V(左)和 1.5 V(右)过剩电压下的光子探测概率 (PDP)。测试芯片展示

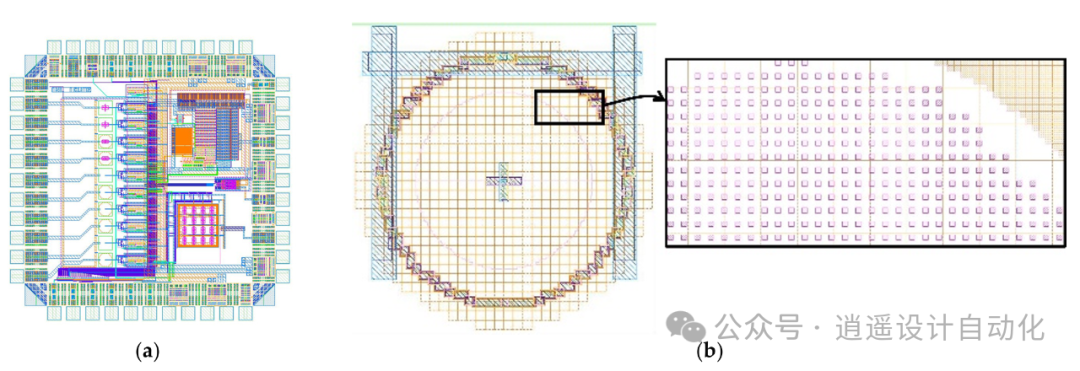

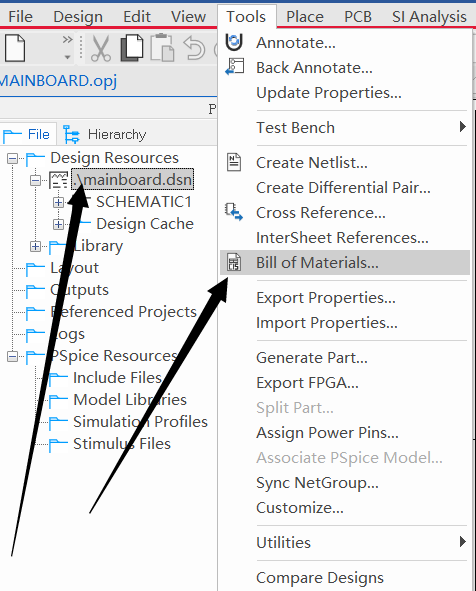

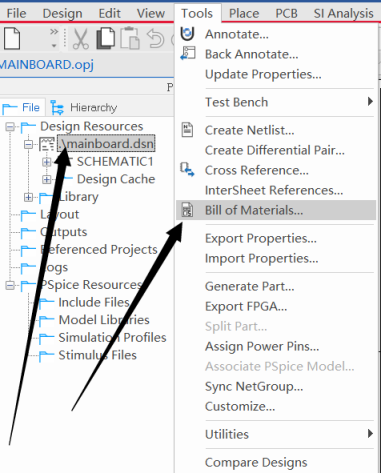

测试电路采用 28 纳米 CMOS FD-SOI 技术设计和制造,包含多种 SPAD 变体(参考、带有各种 FF 的 STI 图案化等)以及用于主动淬火和充电的相关电子器件。图 4 显示了测试芯片的布局视图和一个 SPAD 单元布局示例,其插图缩放显示了光敏区上方的 STI 图案。

图 4 显示了测试芯片的布局: (a) 不带后端线 (BEOL) 层的整体布局视图;(b) SPAD 单元的详细视图,显示光敏区上方的 STI 图案。

图 4 显示了测试芯片的布局: (a) 不带后端线 (BEOL) 层的整体布局视图;(b) SPAD 单元的详细视图,显示光敏区上方的 STI 图案。

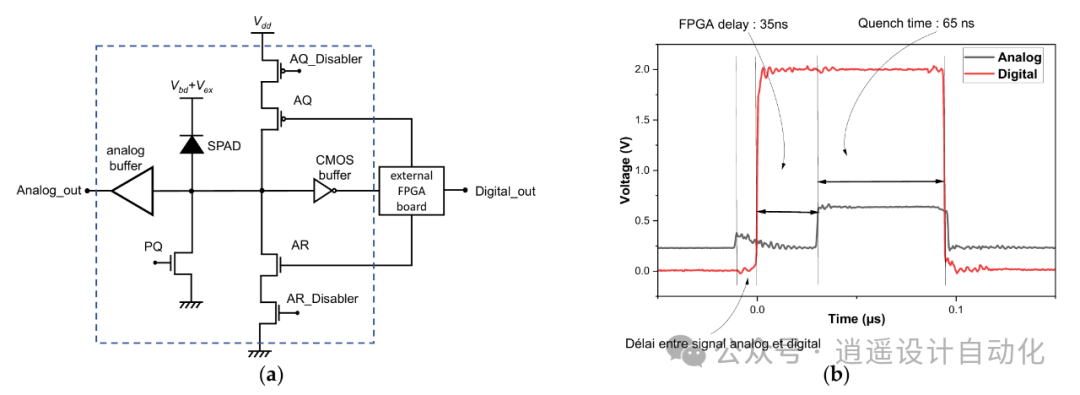

图 5 展示了 SPAD 电子元件:(a) 带有外部 FPGA 的电路原理图,用于主动淬火、充电和死区时间控制;(b) 模拟和数字信号波形,淬火时间为 65 ns。实验结果与讨论

图 5 展示了 SPAD 电子元件:(a) 带有外部 FPGA 的电路原理图,用于主动淬火、充电和死区时间控制;(b) 模拟和数字信号波形,淬火时间为 65 ns。实验结果与讨论

暗计数率(DCR)实验结果:

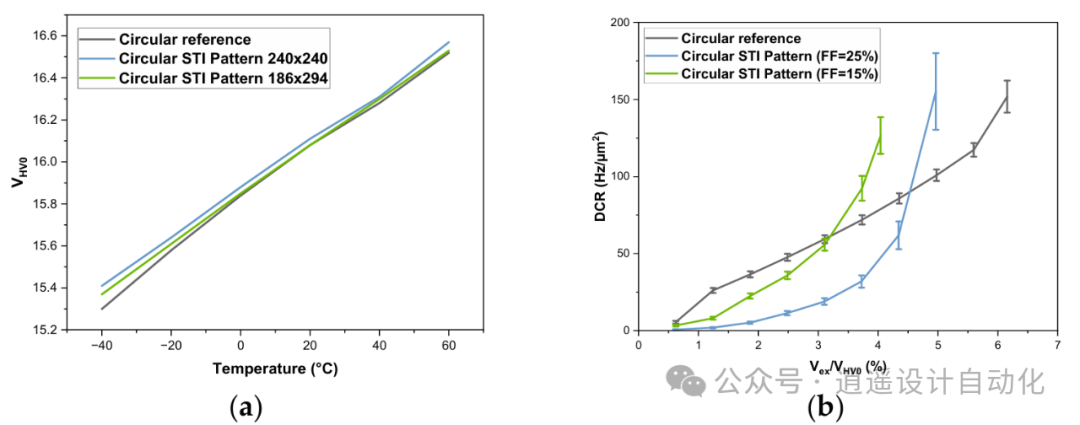

对参考和图案化 SPAD 的 DCR 进行了测量,DCR 代表 SPAD 的噪声水平。图 6 显示了测得的 DCR 与过剩电压和温度的函数关系,揭示了图案化 SPAD 的 DCR 随着过剩电压的增加而增加,这是由于后脉冲失控造成的。

图 6 显示:(a) VHV0 与温度的函数关系;(b) 参考和图案化 SPAD 在 20°C 不同过剩电压下的暗计数率 (DCR)。

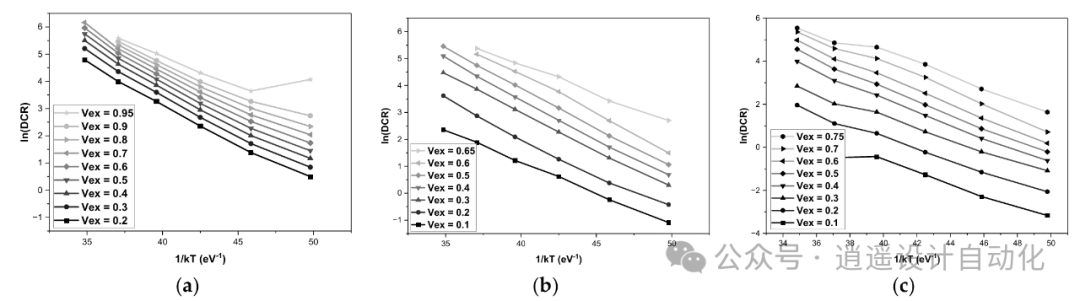

图 6 显示:(a) VHV0 与温度的函数关系;(b) 参考和图案化 SPAD 在 20°C 不同过剩电压下的暗计数率 (DCR)。 图 7 显示了 (a) 参考 SPAD、(b) FF = 15% 的图案化 SPAD 和 (c) FF = 25% 的图案化 SPAD 的 DCR 测量结果的 Arrhenius 图。光子探测效率 (PDP) 实验结果:

图 7 显示了 (a) 参考 SPAD、(b) FF = 15% 的图案化 SPAD 和 (c) FF = 25% 的图案化 SPAD 的 DCR 测量结果的 Arrhenius 图。光子探测效率 (PDP) 实验结果:

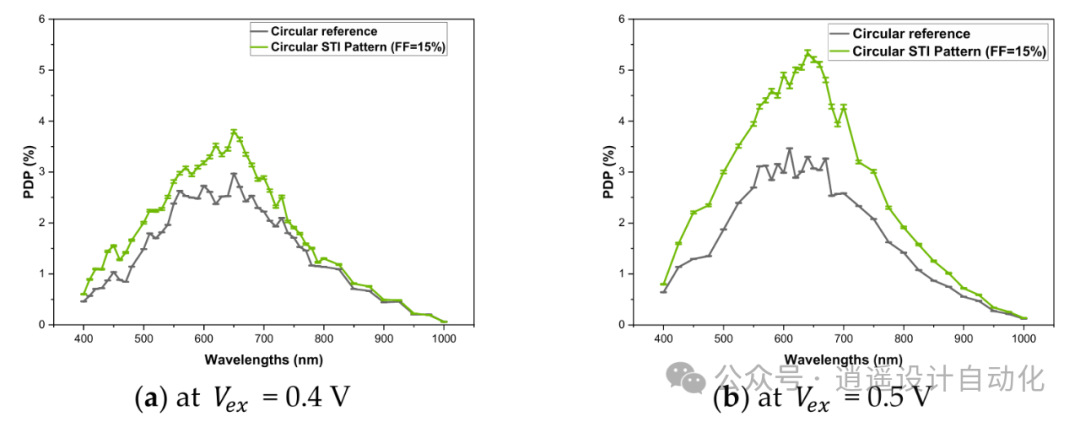

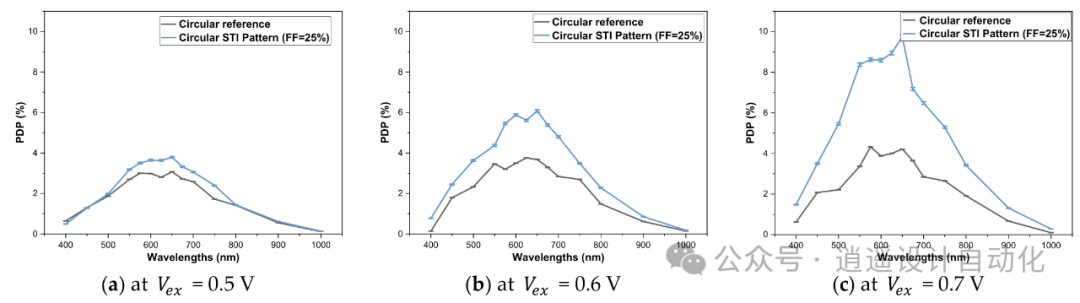

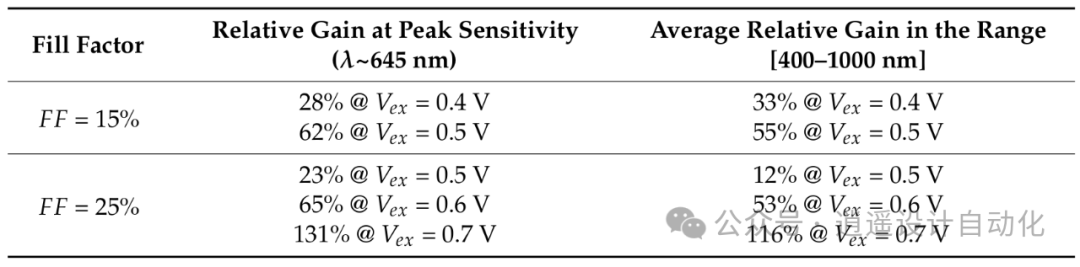

图 8 和图 9 证实了 STI 图案化与参考 SPAD 相比的优势。表 1 总结了峰值灵敏度时的 PDP 相对增益,以及不同过剩电压和与 STI 图形相关的 FF 时光谱上的平均 PDP 相对增益。

图 8 显示了在 Vex = 0.4 V (a) 和 0.5 V (b) 条件下,参考准圆形 SPAD 和具有 STI 沟槽图案(FF = 15%)的类似形状 SPAD 的 PDP 测量结果。

图 8 显示了在 Vex = 0.4 V (a) 和 0.5 V (b) 条件下,参考准圆形 SPAD 和具有 STI 沟槽图案(FF = 15%)的类似形状 SPAD 的 PDP 测量结果。

图 9 显示了在 Vex 值为 0.5 V(a)、0.6 V(b)和 0.7 V(c)时,参考准圆形 SPAD 和具有 STI 沟槽图案(FF = 25%)的 SPAD 的 PDP 测量值。表 1 总结了各种过剩电压和填充因子下的实验 PDP 相对增益。

图 9 显示了在 Vex 值为 0.5 V(a)、0.6 V(b)和 0.7 V(c)时,参考准圆形 SPAD 和具有 STI 沟槽图案(FF = 25%)的 SPAD 的 PDP 测量值。表 1 总结了各种过剩电压和填充因子下的实验 PDP 相对增益。

讨论

图案化结构的 PDP 实验性提高证实了通过 STI 纳米结构实现的建设性干扰的好处。然而,测量的 PDP 改进值大于模拟值,这可能是由于在模拟中考虑了正常入射、在量化 SCR 外部光生载流子时采用了近似值,以及后脉冲对高估 PDP 增益的潜在贡献等因素造成的。

尽管 PDP 有了明显改善,但其绝对值仍然低于最先进的 SPAD,这是因为采用的是标准 CMOS 工艺,没有防反射涂层或微透镜等光子专用功能。不过,如果采用针对光子应用进行优化的工艺,STI 纳米结构方法将更加有效。

结论

在本文中探索了创新方法,用于提高集成到全贫化硅绝缘体(FD-SOI)CMOS 技术中的单光子雪崩二极管(SPAD)的光子探测概率(PDP)。通过对光敏区上方的浅沟槽隔离(STI)层进行纳米结构处理,我们产生了建设性干扰,提高了正面照明的光灵敏度,同时保持了等效的暗计数率(DCR)。

通过模拟和实验结果,证明了这种方法在 PDP 方面实现显著相对增益的潜力,尤其是在较短和较长的波长上。虽然 PDP 绝对值仍然受到使用标准 CMOS 工艺的限制,但 STI 纳米结构技术与光子学专用工艺相结合,有望进一步提高性能。

这项研究推进了开发灵敏度更高的高性能 SPAD 阵列,该阵列可广泛应用于飞行时间测量、面部识别、遥测以及科学和医学成像等领域。

暂无评论