凡亿教育-香老板

凡事用心,一起进步打开APP

公司名片射频电路不增加噪声?可以做到!

在射频(RF)电路设计中,噪声问题毫无疑问是无数电子工程师最怕遇到的问题,因为任何额外噪声都可能严重影响信号质量和系统性能,所以必须设置一系列具体的降噪措施。

1、VCO控制线处理

确保VCO控制线下的地是实心的,避免噪声引入。

VCO控制线应牢固连接到主地,并与其他噪声源隔离。

VCO电源需充分去耦,以减少对其他电路的干扰。

VCO可考虑布放在RF区域末端,并使用金属屏蔽罩进行保护。

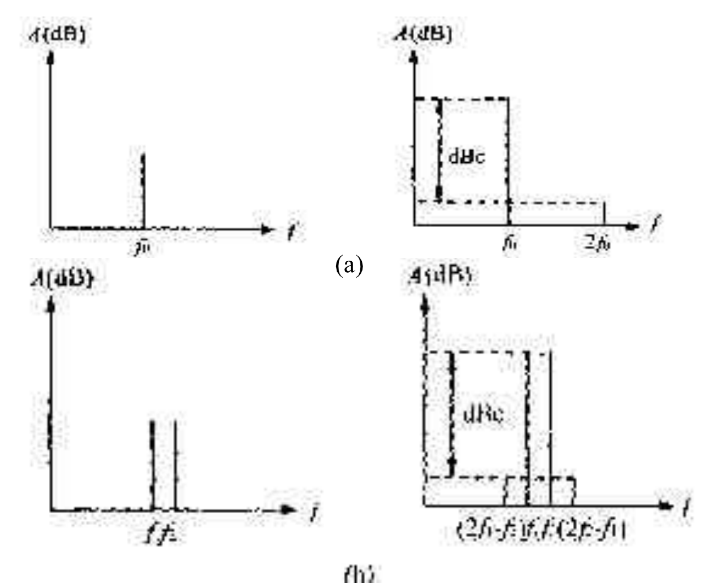

2、谐振电路设计

谐振电路元件布局应紧凑,以减少噪声敏感性。

遵循VCO设计原则,确保谐振电路稳定性。

谐振电路周围应布置足够的接地铜皮,以减少噪声干扰。

3、信号引脚与元件布局

信号引脚应排列紧密,并靠近相关电感和电容。

电感和电容位置需靠近控制环路,以减少噪声传递路径。

控制环路应尽量远离RF、IF或高速数字信号走线。

4、自动增益控制(AGC)放大器设计

AGC放大器设计需遵循良好的模拟电路设计技术。

运放输入引脚和反馈路径应尽可能短,并远离噪声源。

确保AGC电路的带宽适当,避免引入过多噪声。

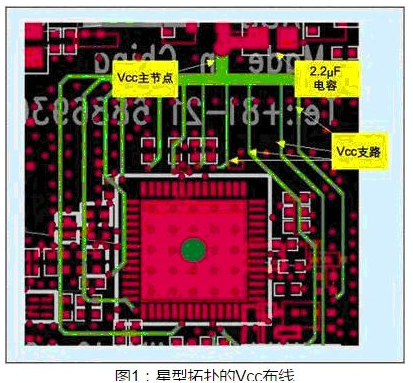

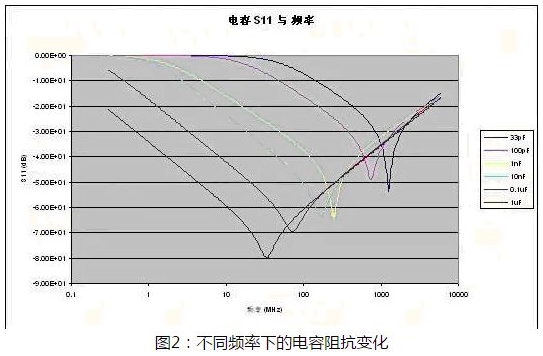

5、接地与去耦

接地应良好,确保所有电路都连接到主地。

芯片电源需得到充分去耦,以减少电源噪声。

在RF走线和其他关键电路周围布置接地铜皮,以减少噪声干扰。

6、信号线布置

如果需要在输入或输出端走长线,优先选择输出端,因为输出端阻抗较低,不易感应噪声。

避免在RF走线上穿过其他信号线,如必须穿过,则应在它们之间布置接地层,或确保它们是十字交叉的,以减少容性耦合。

7、PCB布局布线

数字电路与模拟电路应尽量远离,以减少相互干扰。

RF线路应远离模拟线路和关键数字信号。

在RF走线、焊盘和元件周围布置足够的接地铜皮,并连接到主地。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论