Cadence Allegro是一款广泛应用在电子设计行业的专业EDA软件,因此很多电子工程师选择学习Allegro软件,选择成为Allegro工程师,在项目中承担着重要的角色和责任,那么你知道Allegro工程师平常做什么,在项目中具体负责做什么吗?下面来看看吧!

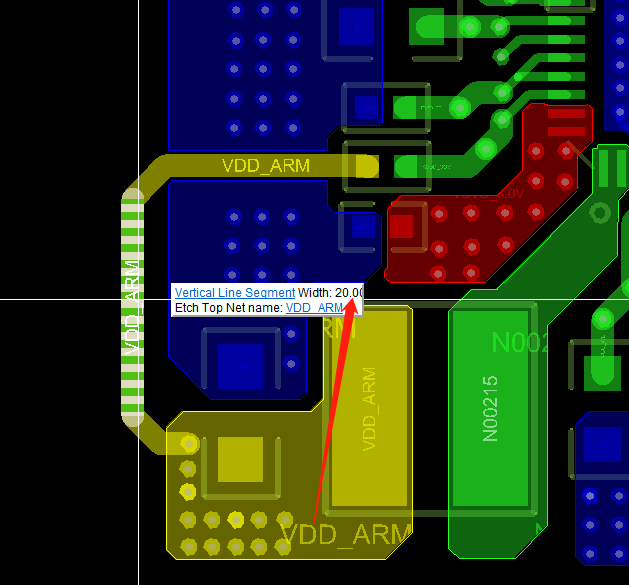

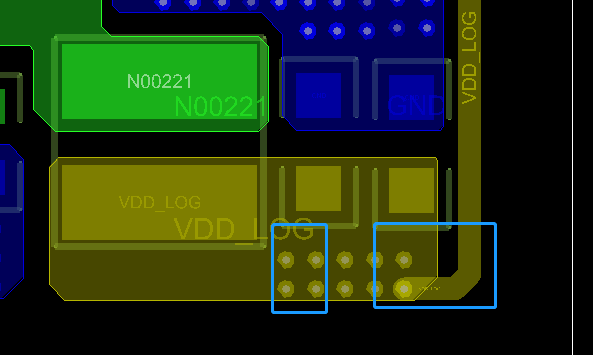

1、高速PCB设计:从DDR到25G+信号的全链路控制

①DDRx设计规范:

DDR3/4 T型拓扑布线:线长匹配公差≤10mil,间距≥3倍线宽,阻抗控制50Ω±10%;

等长组设置:基于Allegro Constraint Manager定义Pin Pair,误差范围±5ps(25Gbps信号);

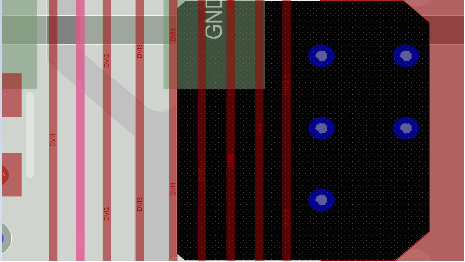

②BGA扇出优化:

0.5mm pitch BGA强制使用8/16mil盲埋孔,优先选择③Via-in-Pad工艺(深南电路标准);

通过Tools→Padstack→Replace批量替换默认过孔,适配国产PCB厂商工艺(如嘉立创盘中孔规范)。

2、制造文件输出:工厂对接的生死线

①钻孔文件(NC Drill):

勾选Leading/Trailing Zero Suppression,匹配CAM350单位设置(英制→公制转换误差≤0.01mm);

强制生成Tool List,标注钻头编号与孔径对应关系(避免板厂误用钻头)。

②Gerber优化:

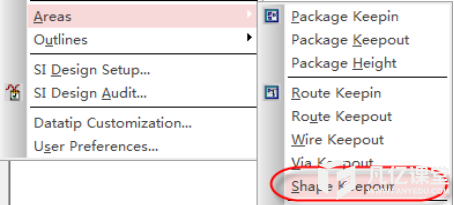

关闭冗余层:通过Manufacturing→Ncdrill_Figure隐藏钻孔标注,减少文件体积;

钢网层处理:Paste Mask尺寸比焊盘缩小5%,防止锡膏过量(华秋DFM标准)。

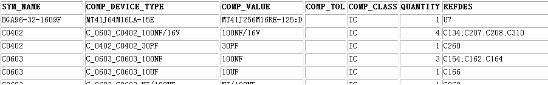

3、国产替代专项:元器件与工艺适配

4、设计验证:从DRC到量产风险评估

①DRC规则定制:

添加3W/3H规则:高速信号间距≥3倍线宽,距参考层高度≤3倍介质厚度;

定义Net Class:区分电源、时钟、普通信号,设置独立间距/线宽规则;

②仿真验证:

使用Sigrity PowerSI完成DDR4眼图仿真,眼高≥200mV,眼宽≥0.7UI;

通过Clarity 3D Solver验证25G+高速连接器阻抗连续性(ΔZ≤±5Ω)。

5、中国工程师必备技能

①Skill脚本开发:

自动生成BOM对比工具:匹配立创商城与国外器件价格/库存(Tcl脚本实现);

一键导出华秋DFM报告:检查线宽/间距、孔铜厚度、阻焊桥等工艺限制;

②设计流程优化:

使用AutoDRC脚本批量修复常见DRC错误(如丝印重叠、焊盘间距违规);

通过Batch DRC功能,夜间自动执行全板检查,生成PDF报告。

本文凡亿企业培训原创文章,转载请注明来源!

暂无评论