在硬件设计领域,最令人头痛的往往不是那些显而易见的难题,而是潜伏在细节中的隐形陷阱,这些陷阱如同暗礁,在项目看似风平浪静时突然出现,导致整个设计"触礁沉没",必须重点注意解决。

1、“完美参考设计”的幻想

典型案例:某智能手表项目严格遵循TI参考设计,却在量产时出现30%的短路率

问题根源:

忽视PCB基板0.1mm的微小翘曲

BGA焊球与PCB的热膨胀系数(CTE)差异超过5ppm/℃

未考虑大批量生产时的工艺波动

解决方案:

进行完整的DFM(可制造性设计)分析

实测材料CTE参数,确保匹配度

增加预生产验证阶段,评估工艺边界条件

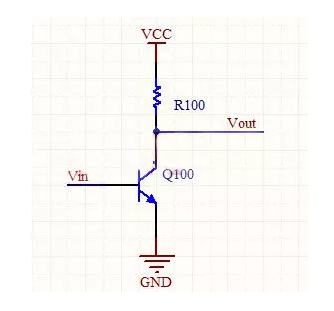

2、仿真模型的“理想陷阱”

典型案例:工业电源项目仿真完美,实测却频繁炸机

问题根源:

MOS管模型未考虑1.5nH封装寄生电感

仿真未包含PCB走线寄生参数

模型未覆盖极端工作条件

解决方案:

建立包含封装参数的完整器件模型

对关键器件进行实测验证

在仿真中加入20%的安全裕量

3、EMC的“玄学困境”

典型案例:

医疗设备通过3颗M3螺丝重构接地,EMI降低12dB

军工设备显示屏贴便利贴消除GHz干扰

问题根源:

忽视机械结构与电磁场的耦合效应

未考虑非对称布局造成的寄生辐射

接地系统阻抗不连续

解决方案:

采用3-5-7规则布置固定螺丝

保持接地系统的低阻抗连续性

进行近场扫描找出辐射热点

4、热设计的“隐形失效”

典型案例:服务器散热片间距误差导致电容寿命缩短70%

问题根源:

未考虑空气湍流导致的局部热点

热仿真模型过于理想化

忽视元器件温度降额要求

解决方案:

采用红外热像仪进行实测验证

在仿真中加入湍流模型

关键器件工作温度控制在额定值80%以下

5、信号完整性的“微小误差”

典型案例:5G基站因0.5Ω阻抗偏差导致误码率飙升

问题根源:

未考虑铜箔粗糙度导致的额外损耗

阻抗计算未涵盖生产工艺波动

未进行全频段阻抗连续性分析

解决方案:

使用TDR实测阻抗曲线

设计时预留±10%的阻抗容差

关键信号线进行端到端仿真

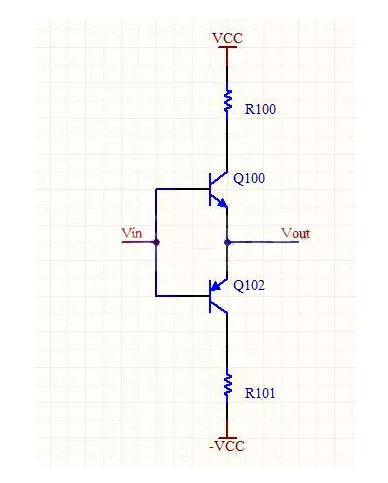

6、电源完整性的“低频噪声”

典型案例:智能音箱因去耦电容布局不当产生"嘶嘶"声

问题根源:

退耦电容的布局电感过大

电源平面谐振未有效抑制

未考虑不同频段的噪声特性

解决方案:

采用分布式电容矩阵布局

电源平面添加适形分割

使用频域分析法优化去耦方案

7、机械应力的“时间炸弹”

典型案例:车载设备BGA焊点在振动测试后断裂

问题根源:

未考虑长期机械疲劳效应

PCB支撑结构设计不合理

材料抗振性能不足

解决方案:

进行加速振动寿命测试

优化机械支撑点布局

采用高韧性焊料合金

8、环境因素的“慢性腐蚀”

典型案例:户外设备因冷凝水导致PCB腐蚀

问题根源:

未评估昼夜温差导致的凝露

防护涂层存在薄弱点

材料耐候性不足

解决方案:

采用三防漆处理

设计排水和透气结构

增加湿度检测和保护电路

9、供应链的“黑天鹅事件”

典型案例:关键MCU停产导致数百万损失

问题根源:

单一来源采购

未跟踪元器件生命周期

缺乏替代方案准备

解决方案:

建立多源供应体系

监控元器件EOL通知

设计时考虑pin-to-pin替代方案

10、人为因素的“低级错误”

典型案例:0603与0805封装混淆导致批量返工

问题根源:

设计审查流程缺失

库管理不规范

人为疲劳导致判断失误

解决方案:

建立三级设计审查制度

实施标准化元件库管理

使用自动检查工具验证封装

当然,如果你想要了解更多的硬件设计知识,短时间内成为硬件工程师,也可以关注凡亿教育的硬件线下培训班。

机构正规、课程可靠、名师优秀

三个月带你速成技术,拿高薪offer,学涨薪路线

巩固电子基础 / 积累高质项目经验 / 学透电子设计

硬件线下培训班第五期

仅剩3个名额

开班日期:6月11日

扫描二维码报名咨询。获取详细目录大纲

本文凡亿企业培训原创文章,转载请注明来源!

暂无评论