凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片USB电路EMC设计:不能错过的十大关键细节

USB接口因高速差分信号特性,极易成为EMC问题的“重灾区”,是不少电子工程师头痛的头号问题,本文将聚焦硬件级干扰抑制与信号完整性,谈谈USB电路EMC设计的十大关键细节,以供参考。

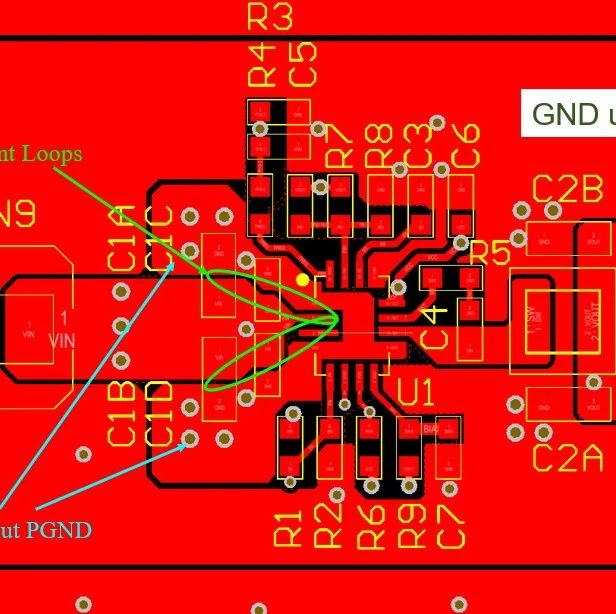

1. 差分对走线“三线等长”

正负信号线长度误差需控制在±5mil内,GND参考层紧邻差分对,避免信号耦合辐射。

2. 终端电阻精准匹配

主机端90Ω差分电阻必须贴片放置,距离USB连接器≤5mm,阻值误差≤1%。

3. 电源去耦电容黄金组合

连接器附近并联100nF(0402封装)陶瓷电容+10μF钽电容,ESR≤0.1Ω,抑制高频噪声。

4. 磁珠选型硬指标

电源线上串联600Ω@100MHz磁珠(如Murata BLM18PG601SN1),替代传统0Ω电阻,阻断共模电流路径。

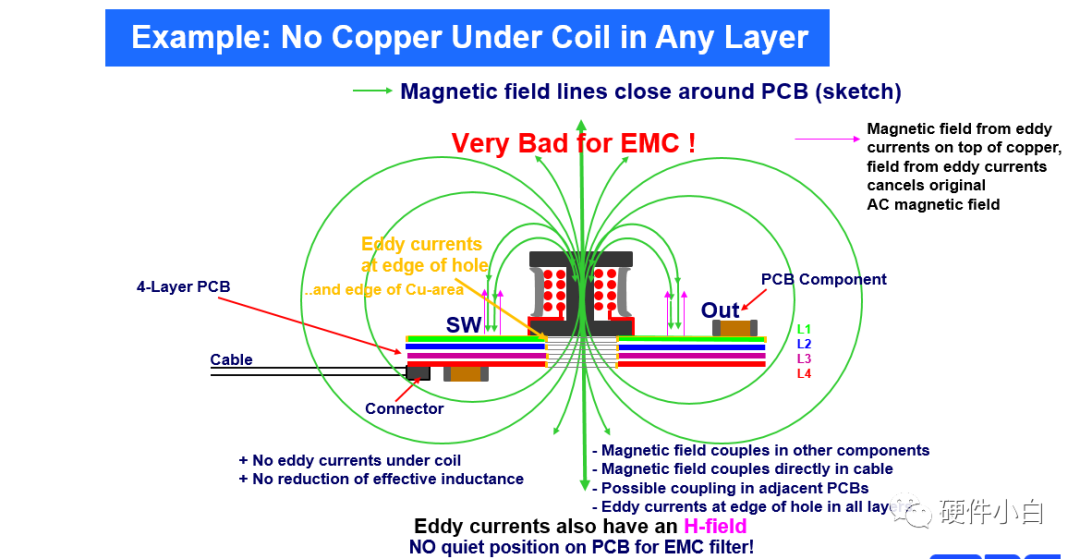

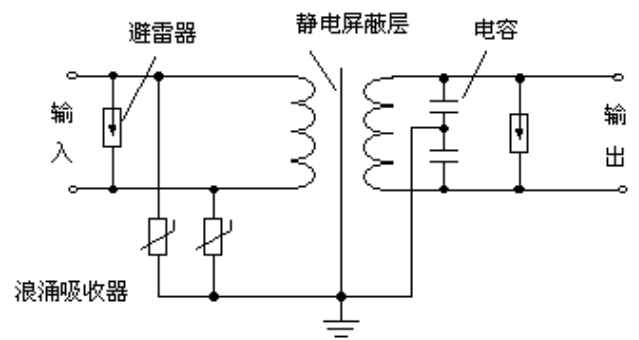

5. 共模电感强制标配

USB2.0使用10μH共模电感(如TDK NFE61PT472C1H9L),USB3.0及以上需升级为20μH,扼制差模干扰。

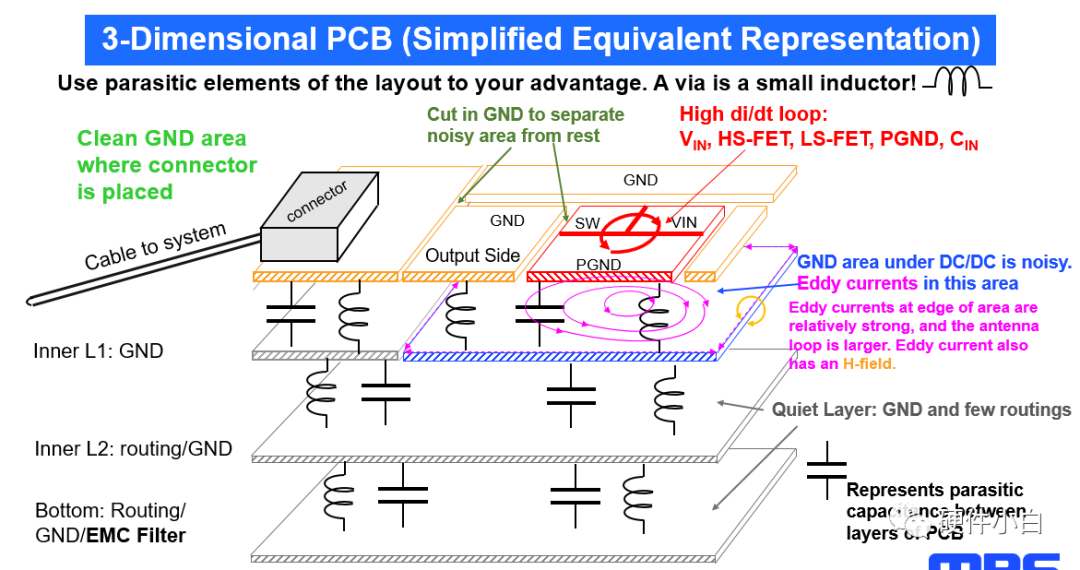

6. 屏蔽层360°接地

金属外壳USB连接器必须与PCB地层单点接地,屏蔽层焊盘间距≤0.5mm,杜绝“浮空”设计。

7. ESD防护器件选型法则

选用超低电容TVS(如SMAJ5.0A,电容≤3pF),寄生参数比传统ESD二极管降低80%。

8. 晶振辐射专项治理

USB主控时钟晶振远离连接器(间距>20mm),外壳增加导电泡棉接地,抑制时钟谐波泄漏。

9. 层叠设计铁律

4层板采用SIG-GND-PWR-SIG结构,差分对走内层,相邻层铺铜间距≥4倍线宽。

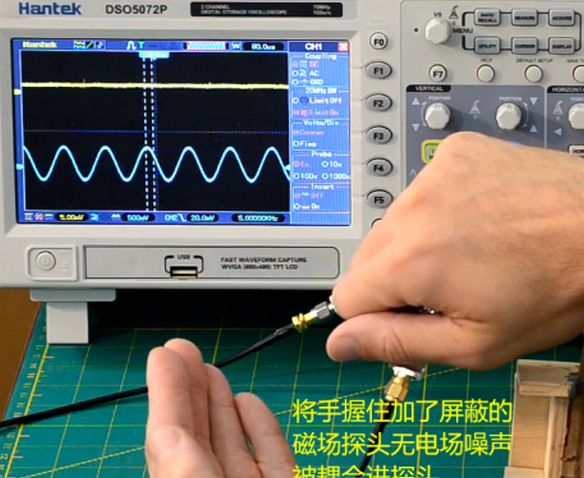

10. 测试验证临界点

辐射测试重点关注30MHz-1GHz频段,差分信号眼图交叉点抖动需<200ps,过冲幅度≤200mV。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论