如果你想要PCB产品顺利上市,降低整改成本,最好建议是在产品研发初期植入EMC设计思维,这样做可以减少70%以上的整改成本。

1、硬件设计军规

①滤波电路预埋

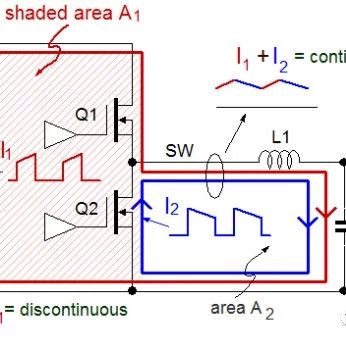

电源端口强制预留X电容(1μF起)、共模电感(按150kHz差模干扰选型)

时钟电路采用π型滤波,晶振距离板边>25.4mm,输出端串联22Ω电阻

②器件布局红线

数字/模拟地平面分割间距>2mm,单点接地采用0Ω电阻连接

开关电源与ADC芯片间距>500mil,大功率器件保持20H以上电源平面内缩

③高速信号专区

DDR4总线采用菊花链拓扑,ODT终端匹配电阻紧贴芯片放置

1GHz以上信号线换层时,每层增加2个地过孔形成回流路径

2、PCB布局军规

①叠层结构标准

6层板推荐SIG-GND-PWR-PWR-GND-SIG结构,关键信号走内层

电源平面比地平面内缩40mil,相邻信号层间距≥5mil

②布线禁区清单

关键信号禁止跨电源分割,过孔数量≤2个/inch

差分线间距保持3W原则,禁止在晶振下方走线

③电容部署规范

0.1μF去耦电容距电源管脚≤50mil,10μF滤波电容成④对角线布置

每颗IC至少配备1大1小组合电容,布线长度差<100mil

3、结构防护军规

①模块隔离标准

IGBT与控制板间距>20mm,高压铜排回路面积<100mm²

高低压线束垂直交叉,夹角≥60°,并行长度<50mm

②滤波组件预留

输入/输出端口预留磁环安装位(直径≥线径3倍)

高压连接器附近设置2个以上M3接地螺柱,间距15mm

③屏蔽实施细则

屏蔽腔体谐振频率>工作频率10倍,过孔阵列间距<λ/20

缝隙处采用导电胶填充,通风孔使用蜂窝状结构

4、测试验证军规

①设计自检清单

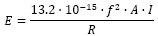

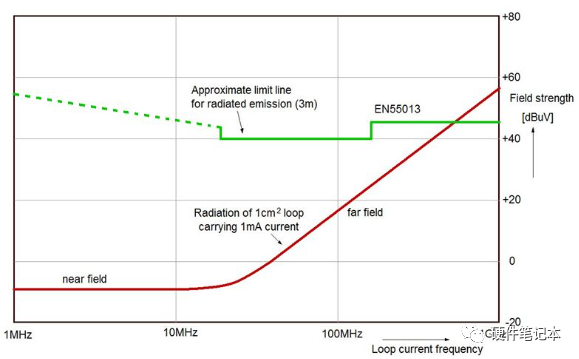

关键信号环路面积<200mm²,地线阻抗<1mΩ

电源入口插入损耗满足CISPR25 CLASS5要求

②仿真验证点

1GHz以上信号进行SIwave仿真,眼图高度>70%

共模辐射采用HFSS建模,屏蔽效能>40dB

③测试预处理

首次测试拆除所有滤波器件,记录裸机噪声频谱

预留20%余量设计滤波器,采用两级CLC拓扑结构

5、特殊场景应对

①高频接地策略

100MHz以上采用多点接地,地线宽度≥20mil

混合接地系统设置地平面切换区域,过渡带≥500mil

②热设计协同

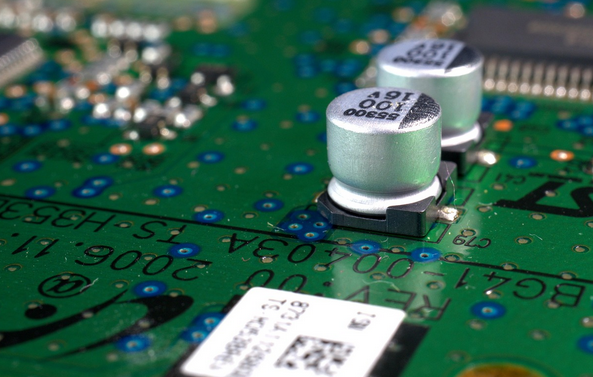

热敏器件(如液态电容)距发热源>15mm

散热片通过导电泡棉接地,接触电阻<10mΩ

③生产适配设计

滤波器件焊盘间距满足±0.1mm公差

屏蔽罩设置0.5mm工艺边,焊接温度≤235℃

本文凡亿教育原创文章,转载请注明来源!

暂无评论