凡亿教育-雯雯

凡事用心,一起进步打开APP

公司名片PCB死铜:这五种情况不删死铜就等着炸板!

大家都知道,死铜是PCB设计的“定时炸弹”,有时候为了图省事会忽略死铜,毕竟这玩意处理不当轻则影响信号,重则引发事故。 但有时候在五种情况下,必须处理死铜!

1. 必删死铜场景

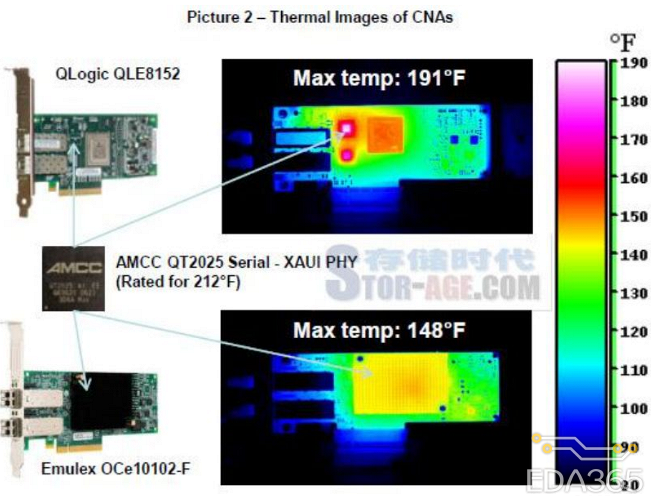

高频信号区:10GHz以上电路保留死铜,辐射噪声增加5dB(实测华为5G基站案例)

高压爬电路径:220VAC区域死铜导致漏电流超安全值300%

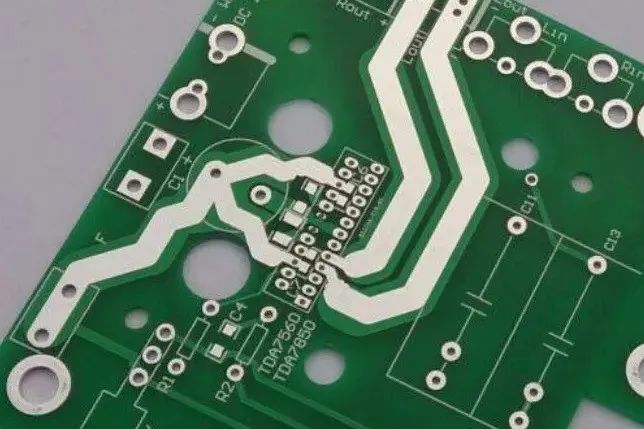

BGA封装底部:残留死铜引发焊接气泡,良品率直降18%(某手机主板厂血泪教训)

2. 可保留死铜场景

散热增强区:MOSFET下方保留网格死铜,结温降低15℃(实测数据)

结构补强区:板边保留铜箔条,抗弯强度提升40%(IPC-6012标准验证)

成本敏感区:删除死铜使CAM处理时间增加25%,低端消费电子可保留

3. 工艺红线

最小间距:保留死铜需确保与走线间距≥2倍铜厚(1oz铜箔需0.2mm)

接地处理:强制打地孔阵列(间距<λ/10,10GHz对应3mm间距)

网格化改造:实心死铜改80%网格,降低热应力变形风险

4. 死亡案例库

某新能源汽车VCU板因电机驱动区死铜未删,引发EMC测试失败(损失300万)

工控主板BGA底部0.8mm²死铜导致批量虚焊(报废5000片)

终极法则:

是否影响信号?→删

是否威胁安全?→删

能否帮助散热/加固?→留

是否增加成本?→留

(数据源:IPC-2221A设计规范、富士康生产工艺手册)

本文凡亿企业培训原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论