凡亿助教-小美

凡事用心,一起进步打开APP

公司名片 石英晶振的三大误区,踩坑即报废!

石英晶振是电路的“心跳源”,一个引脚接错,整个系统瘫痪。但在设计过程中,工程师可能会碰见几个问题,陷入误区,所以本文将盘点石英晶振的三大误区,去除问题!

误区一:引脚排列“想当然”

现象:误以为所有晶振引脚定义相同,直接套用经验接线。

真相:不同厂商、型号的引脚功能可能颠倒(如无源晶振无极性,有源晶振需区分电源/地/输出)。

后果:轻则无信号,重则烧毁芯片。

对策:必须查Datasheet,重点关注丝印标记点(通常1脚为GND或VCC)。

误区二:OE引脚“放养式”处理

现象:忽略有源晶振的OE(Output Enable)引脚,直接悬空或错误接电。

真相:OE引脚控制输出使能,悬空可能导致信号漂移或高阻态。

后果:时钟信号异常,系统频繁重启。

对策:根据Datasheet明确接法——通常接地(禁用输出)或接VCC(启用),绝不可悬空。

误区三:电源“反接”或“地线虚接”

现象:误将VCC接GND,或地线焊接不良。

真相:晶振对电源噪声敏感,反接会直接击穿内部电路;虚接导致信号抖动。

后果:晶振发热、不起振,甚至损坏周边IC。

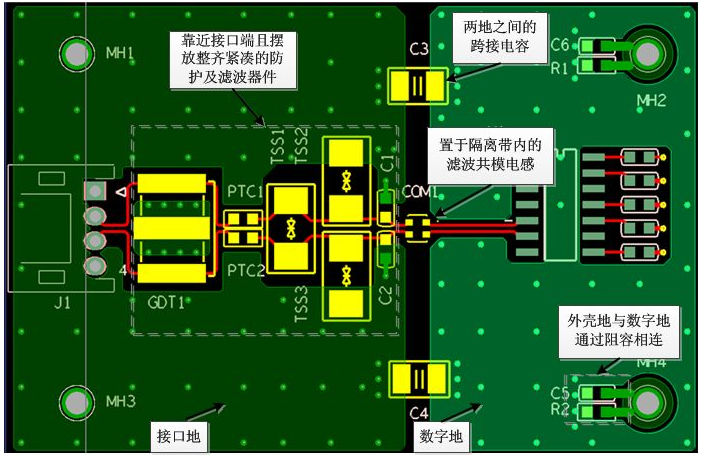

对策:用万用表确认VCC/GND位置,地线需保证低阻抗通路(如铺铜处理)。

4、进阶避坑指南

封装陷阱:SMD贴片晶振(如49S、3225)引脚间距极小,手工焊接需防短路。

温度补偿:高精度场景需选TCXO(温度补偿晶振),普通AT切晶振温漂可达±50ppm。

负载电容:无源晶振需外接匹配电容(通常12pF~22pF),值不对会频偏。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论