凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片AD如何使用单端蛇形走线?

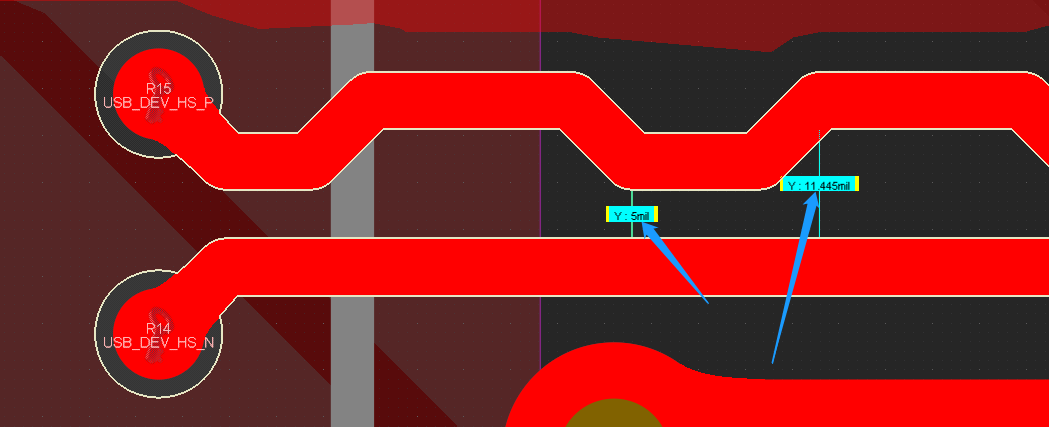

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

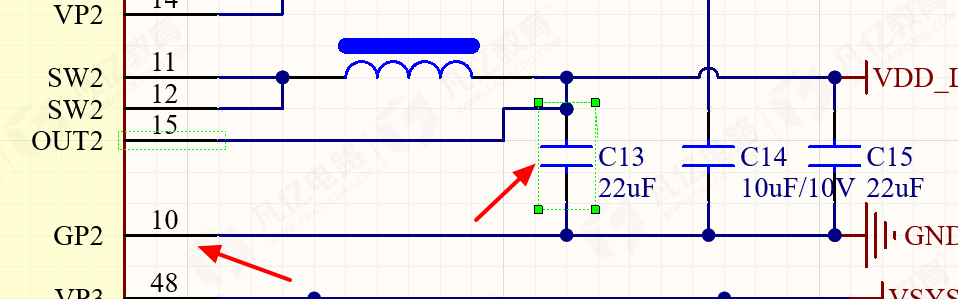

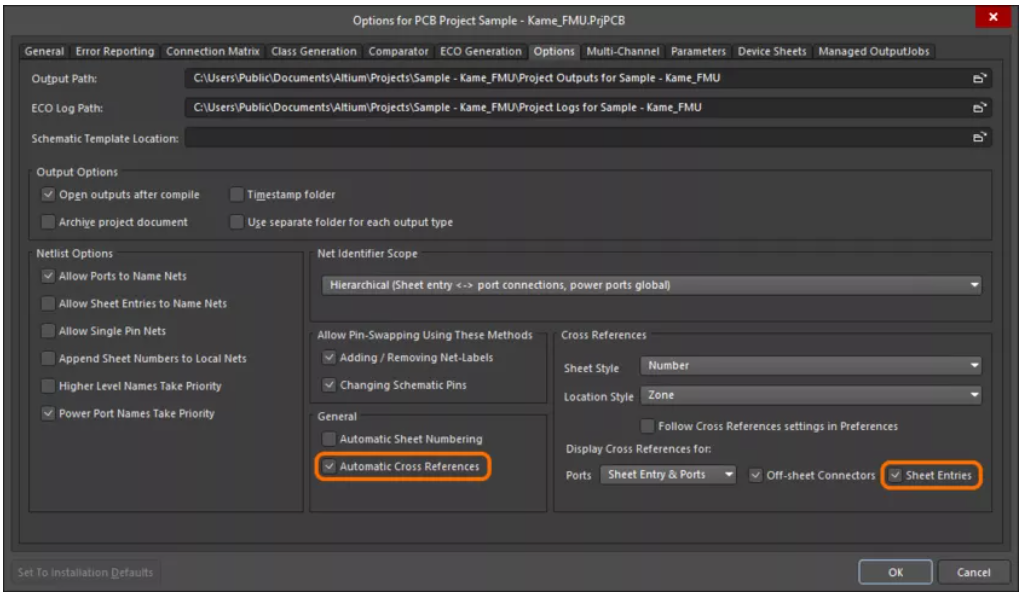

(1)在Altium Designer中,等长绕线之前建议完成PCB的连通性,并且建立好相对应的网络类,因为等长是在既有的走线上进行绕线的,不是一开始就走成蛇形线,等长的时候也是基于一个总线里面以最常的那条线为目标线进行长度的等长。

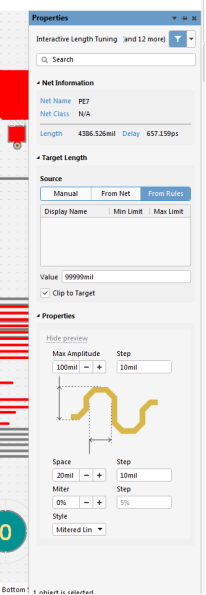

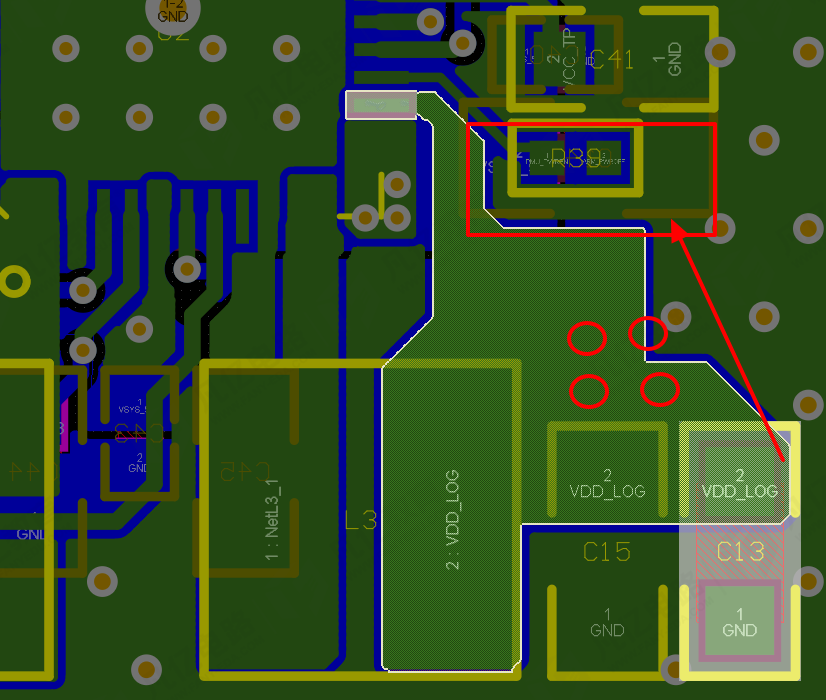

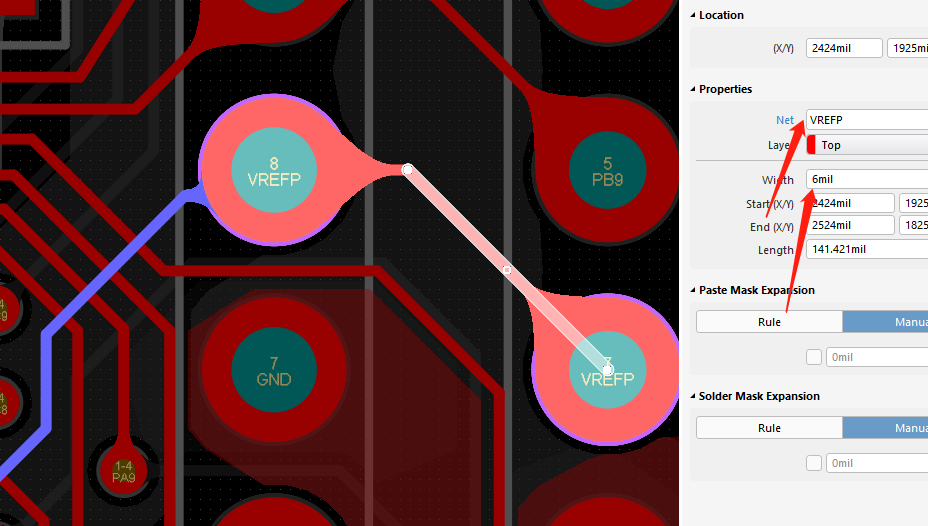

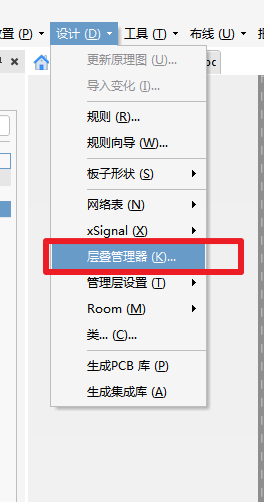

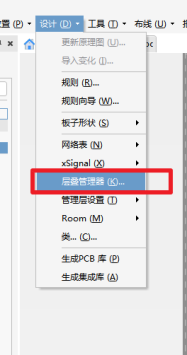

(2)执行菜单命令“布线-网络等长调节”如图5-128所示,或者快捷键“UR”,激活等长命令,单击需要等长的走线,并按“Tab”键调出等长参数设置窗口,如图5-129所示。

图5-128 “网络等长调节”命令

图5-129 单端蛇形线参数设置

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论