答:使用Allegro软件进行PCB设计,一般会使用约束规则辅助设计,当设计时有对象违反了设置的约束规则,软件会以DRC标记的形式提醒设计者。

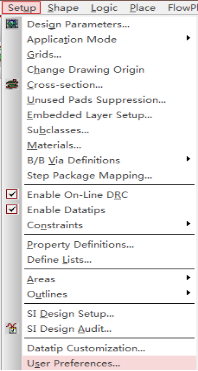

一般DRC标记分为填充和不填充显示的,显示的设置在Setup-User Preferences里,如图6-336所示;

图6-336 设置面板

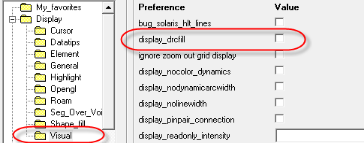

然后在Display-Visual选项板中勾选上display_drcfill,如图6-337所示,勾选上后,DRC显示方式会变为实心显示。此改动只会修改DRC的显示效果,如图6-338所示。

图6-337 Display选项面板

图6-338 DRC显示对比图示

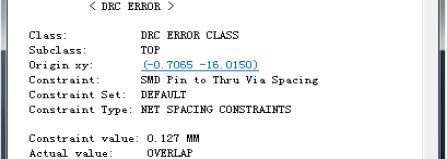

如果PCB中出现DRC,可以通过Display-show Element功能查询相关信息,包括产生DRC的所在层、坐标、名称、所属模板、类型、约束规则设定值、当前值等,如图6-339所示:

图6-339 DRC信息图示

Ø Subclass:DRC所在层为TOP层;

Ø Origin xy:DRC所在位置的坐标;

Ø Constraint:DRC报错具体内容;

Ø Constraint Set:DRC所属约束规则模板;

Ø Constraint Type:DRC所属类型;

Ø Constraint value:约束规则设定值大小;

Ø Actual value:当前值的大小。

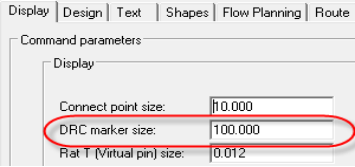

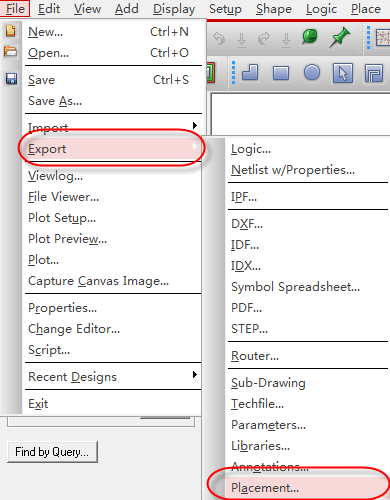

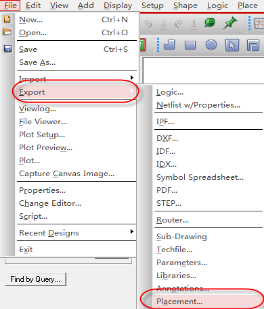

DRC显示大小可在Setup-Design parameters选项的Display选项卡进行设置,如图6-340所示。

图6-340 DRC显示大小修改图示

PCB设计中常见的DRC符号及其含义如下:

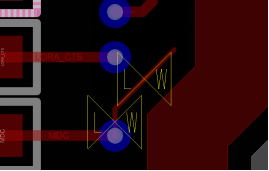

Ø L与L是指Line(走线)与Line(走线)的间距错误,需要移动走线或者修改约束规则管理器中的走线与走线间距数值进行DRC消除,如图6-341所示;

图6-341 线间距DRC图示

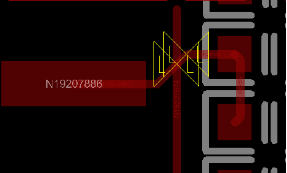

Ø L与W是指违反了Min line width(最小线宽)的错误,需要将线宽加粗到约束规则管理器设置的宽度值,如图6-342所示;

图6-342 线宽DRC图示

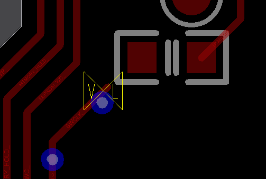

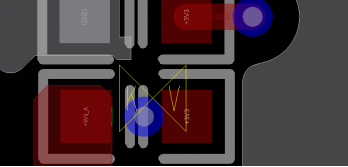

Ø L与V是指Line(走线)与Via(过孔)的间距错误,如图6-343所示;

图6-343 走线与过孔DRC图示

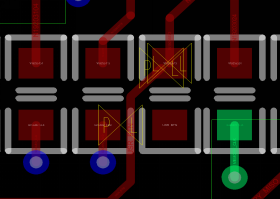

Ø P与P是指零件的PIN(管脚)与PIN(管脚)的间距错误,如图6-344所示;

图6-344 焊盘与焊盘DRC图示

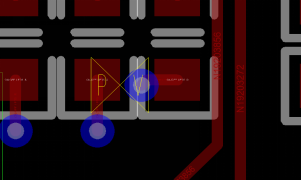

Ø P与L是指Pin(管脚)与Line(走线)的间距错误,如图6-345所示;

图6-345 焊盘与走线DRC图示

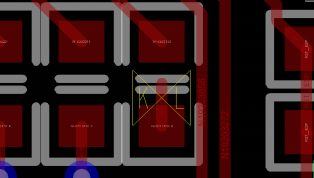

Ø P与V是指Pin(管脚)与Via(过孔)的间距错误,如图6-346所示;

图6-346焊盘与过孔DRC图示

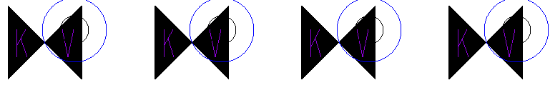

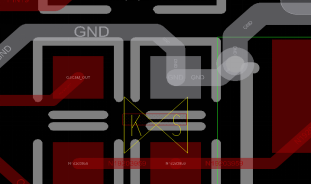

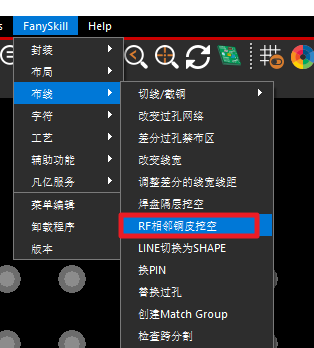

Ø K与L是指Keepout(禁布区域)内有Line(走线)而报错,如图6-347所示;

图6-347禁布区域与走线DRC图示

Ø K与V是指Keepout(禁布区域)内有Via(过孔)而报错,如图6-348所示;

图6-348 禁布区域与过孔DRC图示

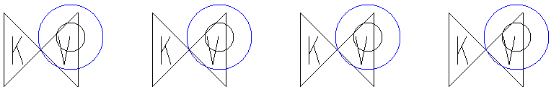

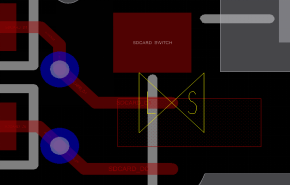

Ø K与S是指Keepout(禁布区域)内有Shape(铜皮)而报错,如图6-349所示;

图6-349 禁布区域与铜皮DRC图示

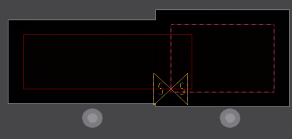

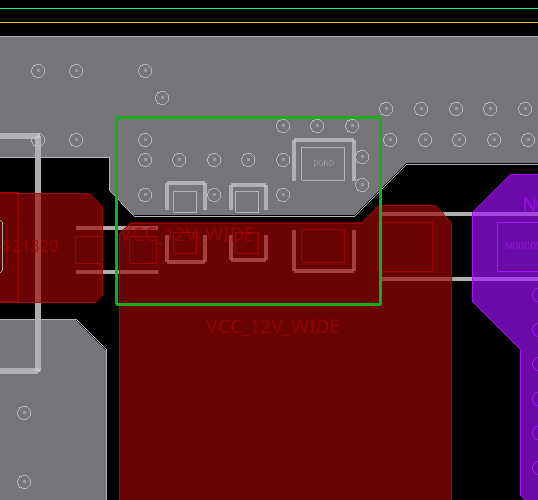

Ø S与S是指Shape(铜皮)与Shape(铜皮)的间距错误,一般指静态铜到静态铜的间距错误,如图6-350所示;

图6-350 铜皮与铜皮DRC图示

Ø L与S是指Line(走线)与Shape(铜皮)的间距错误,如图6-351所示;

图6-351走线与铜皮DRC图示

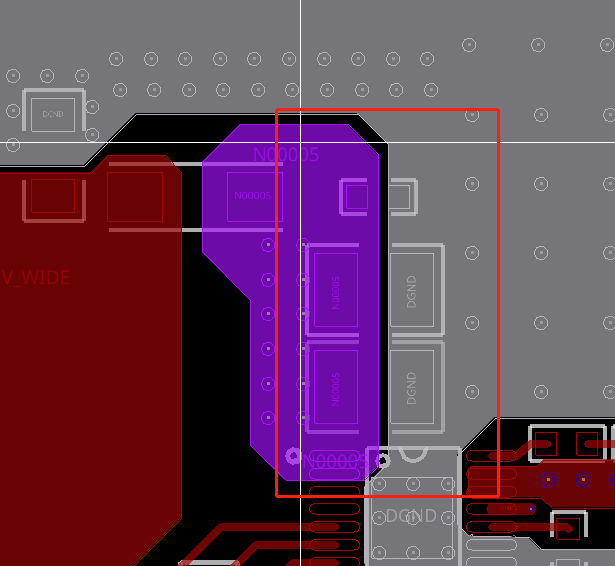

Ø V与S是指Via(过孔)与Shape(铜皮)的间距错误。如图6-352所示。

图6-352过孔与铜皮DRC图示

暂无评论