凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片PADS8层DDR3 Fly-by拓扑结构视频教程

一、PADS8层DDR3 Fly-by拓扑结构视频教程课程详情

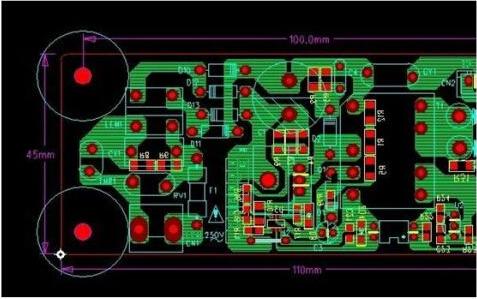

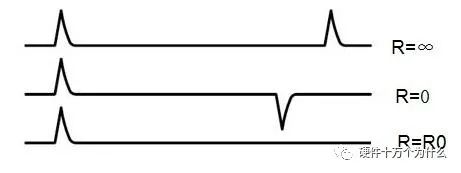

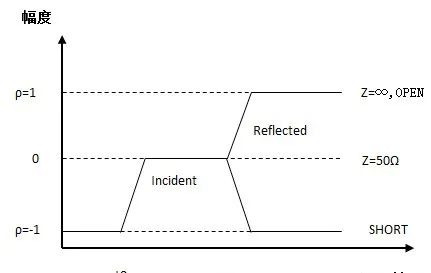

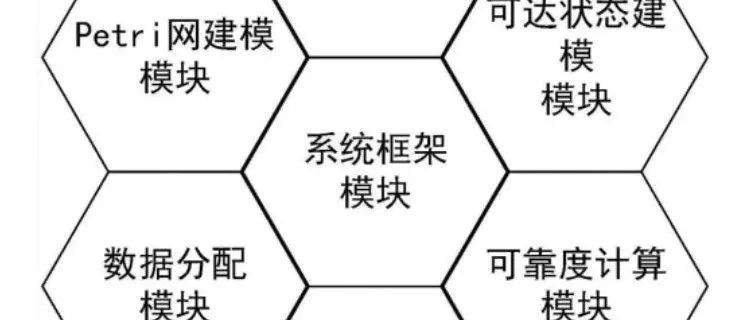

本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

二、课程目录

1、视频介绍及前期准备

2、原理图简单讲解、网标输出、错误解析

3、DDR 菊花链拓扑结构布局分析

4、叠层设置以及阻抗规则设置

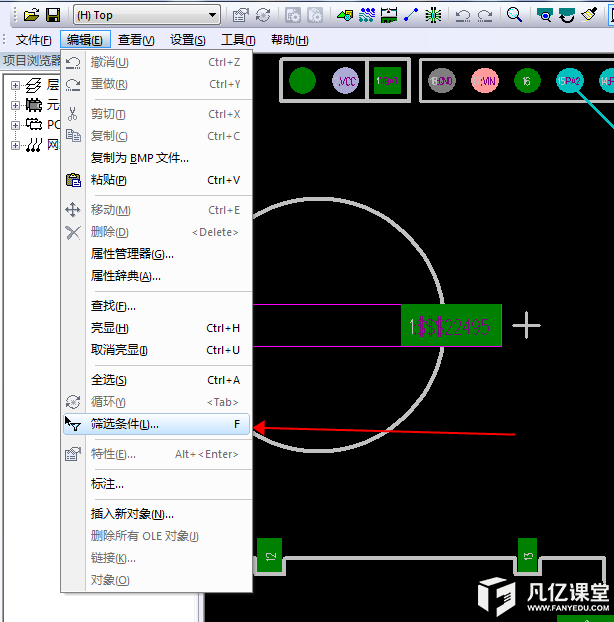

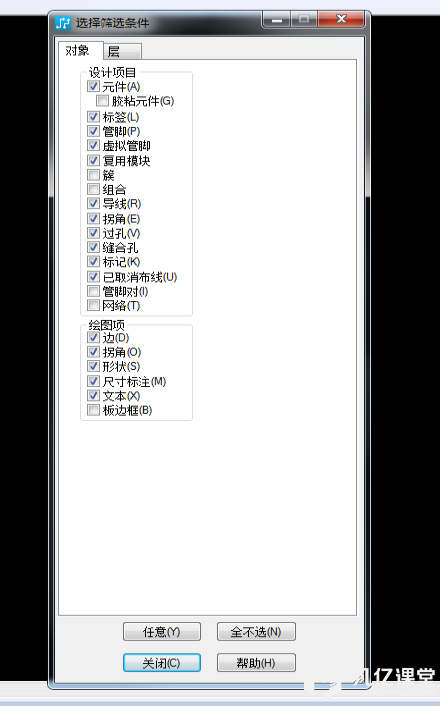

5、Fanout 处理、Class 设置、布线规划

6、DDR3 数据线布线(1)

7、DDR3 数据线布线(2)

8、DDR3 地址、控制线布线(1)

9、DDR3 地址、控制线布线(2)

10、DDR3 数据线时序等长(1)

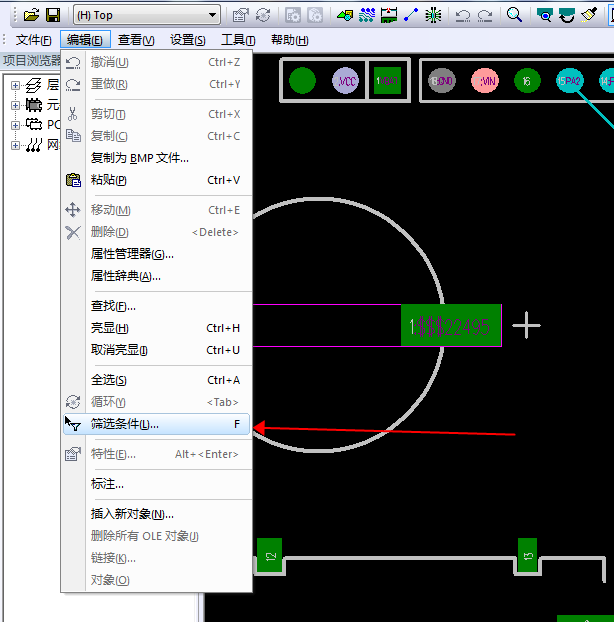

11、DDR3 数据线时序等长(2)

12、DDR3 数据线时序等长(3)

13、DDR3 地址、控制线时序等长(1)

14、DDR3 地址、控制线时序等长(2)

15、地平面处理与电源平面分割

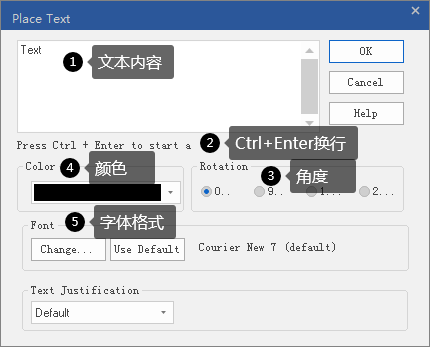

16、后期丝印处理、文本添加、整板铺地铜处理

17、Gerber 文件输出、贴片文件输出

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论