DC/DC 开关控制器的 MOSFET 选择是一个复杂的过程。仅仅考虑 MOSFET 的额定电压和电流并不足以选择到合适的 MOSFET。要想让 MOSFET 维持在规定范围以内,必须在低栅极电荷和低导通电阻之间取得平衡。在多负载电源系统中,这种情况会变得更加复杂。

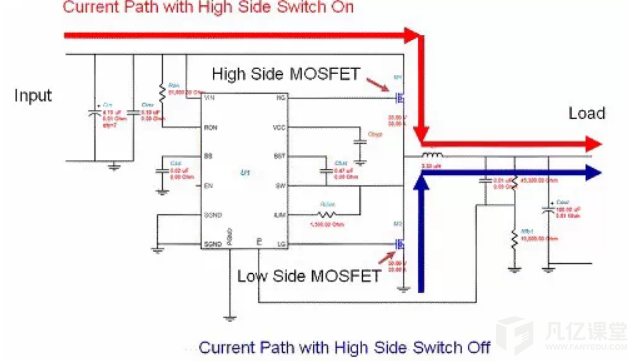

图 1—降压同步开关稳压器原理图

DC/DC 开关电源因其高效率而广泛应用于现代许多电子系统中。例如,同时拥有一个高侧 FET和低侧 FET 的降压同步开关稳压器,如图 1 所示。这两个 FET 会根据控制器设置的占空比进行开关操作,旨在达到理想的输出电压。降压稳压器的占空比方程式如下:

1) 占空比 (高侧FET,上管) = Vout/(Vin*效率)

2) 占空比 (低侧FET,下管) = 1 – DC (高侧FET)

FET 可能会集成到与控制器一样的同一块芯片中,从而实现一种最为简单的解决方案。但是,为了提供高电流能力及(或)达到更高效率,FET 需要始终为控制器的外部元件。这样便可以实现最大散热能力,因为它让FET物理隔离于控制器,并且拥有最大的 FET 选择灵活性。它的缺点是 FET 选择过程更加复杂,原因是要考虑的因素有很多。

一个常见问题是“为什么不让这种 10A FET 也用于我的 10A 设计呢?”答案是这种 10A 额定电流并非适用于所有设计。

选择 FET 时需要考虑的因素包括额定电压、环境温度、开关频率、控制器驱动能力和散热组件面积。关键问题是,如果功耗过高且散热不足,则 FET 可能会过热起火。我们可以利用封装/散热组件 ThetaJA 或者热敏电阻、FET 功耗和环境温度估算某个 FET 的结温,具体方法如下:

3) Tj = ThetaJA * FET 功耗(PdissFET) + 环境温度(Tambient)

它要求计算 FET 的功耗。这种功耗可以分成两个主要部分:AC 和 DC 损耗。这些损耗可以通过下列方程式计算得到:

4) AC损耗: AC 功耗(PswAC) = ½ * Vds * Ids * (trise + tfall)/Tsw

其中,Vds 为高侧 FET 的输入电压,Ids 为负载电流,trise 和 tfall 为 FET 的升时间和降时间,而Tsw 为控制器的开关时间(1/开关频率)。

5) DC 损耗: PswDC = RdsOn * Iout * Iout * 占空比

其中,RdsOn 为 FET 的导通电阻,而 Iout 为降压拓扑的负载电流。

其他损耗形成的原因还包括输出寄生电容、门损耗,以及低侧 FET 空载时间期间导电带来的体二极管损耗,但在本文中我们将主要讨论 AC 和 DC 损耗。

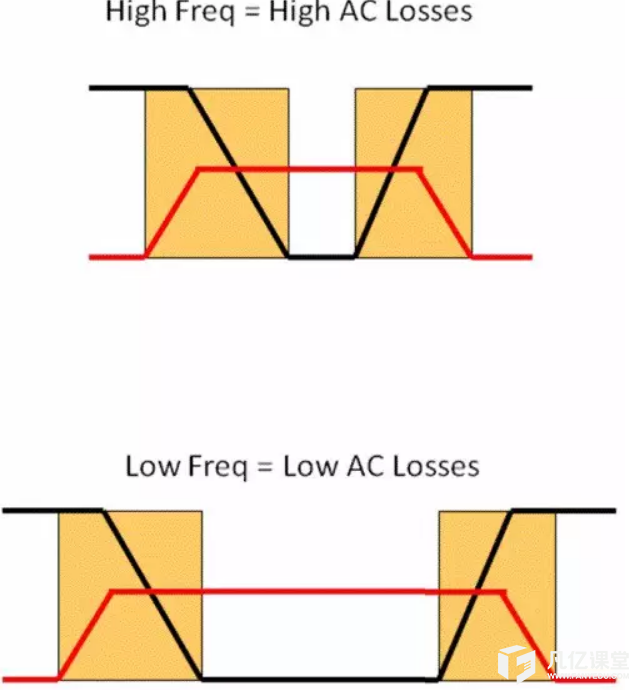

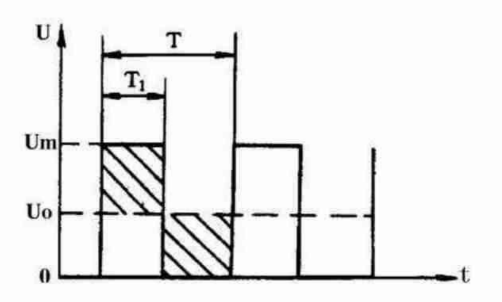

开关电压和电流均为非零时,AC 开关损耗出现在开关导通和关断之间的过渡期间。图 2 中高亮部分显示了这种情况。根据方程式 4),降低这种损耗的一种方法是缩短开关的升时间和降时间。通过选择一个更低栅极电荷的 FET,可以达到这个目标。另一个因数是开关频率。开关频率越高,图 3 所示升降过渡区域所花费的开关时间百分比就越大。因此,更高频率就意味着更大的AC开关损耗。所以,降低 AC 损耗的另一种方法便是降低开关频率,但这要求更大且通常也更昂贵的电感来确保峰值开关电流不超出规范。

图 2—AC 损耗图

图 3—开关频率对 AC 损耗的影响

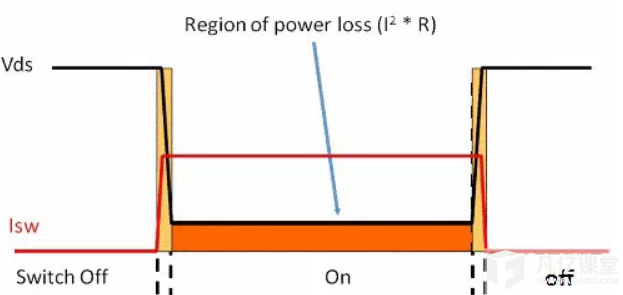

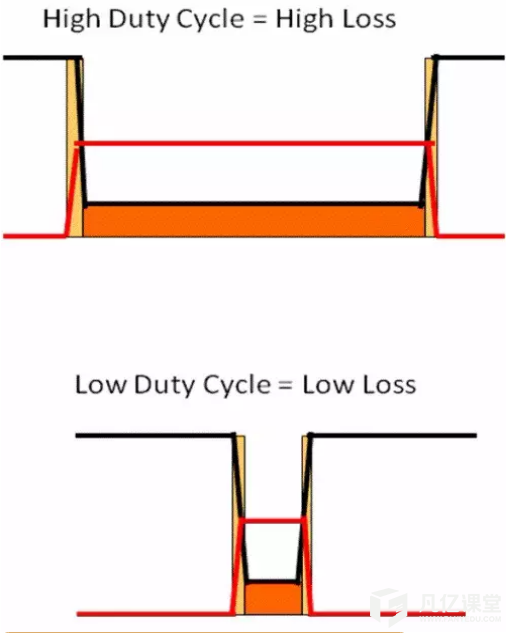

开关处在导通状态下出现 DC 损耗,其原因是 FET 的导通电阻。这是一种十分简单的 I2R 损耗形成机制,如图 4 所示。但是,导通电阻会随 FET 结温而变化,这便使得这种情况更加复杂。所以,使用方程式 3)、4)和 5)准确计算导通电阻时,就必须使用迭代方法,并要考虑到 FET 的温升。降低 DC 损耗最简单的一种方法是选择一个低导通电阻的 FET。另外,DC 损耗大小同FET 的百分比导通时间成正比例关系,其为高侧 FET控制器占空比加上 1 减去低侧 FET 占空比,如前所述。由图 5 我们可以知道,更长的导通时间就意味着更大的DC 开关损耗,因此,可以通过减小导通时间/FET 占空比来降低 DC 损耗。例如,如果使用了一个中间 DC 电压轨,并且可以修改输入电压的情况下,设计人员或许就可以修改占空比。

图 4—DC 损耗图

图 5—占空比对 DC 损耗的影响

尽管选择一个低栅极电荷和低导通电阻的 FET 是一种简单的解决方案,但是需要在这两种参数之间做一些折中和平衡。低栅极电荷通常意味着更小的栅极面积/更少的并联晶体管,以及由此带来的高导通电阻。另一方面,使用更大/更多并联晶体管一般会导致低导通电阻,从而产生更多的栅极电荷。这意味着,FET 选择必须平衡这两种相互冲突的规范。另外,还必须考虑成本因素。

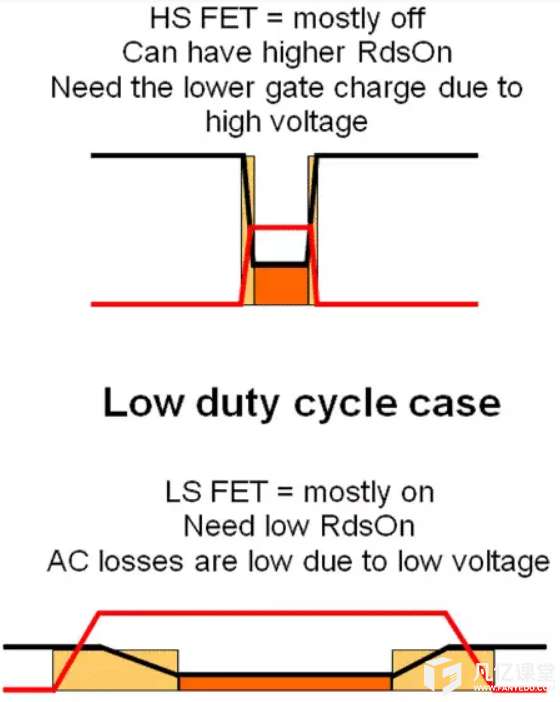

低占空比设计意味着高输入电压,对这些设计而言,高侧 FET 大多时候均为关断,因此 DC 损耗较低。但是,高 FET 电压带来高 AC 损耗,所以可以选择低栅极电荷的 FET,即使导通电阻较高。低侧 FET 大多数时候均为导通状态,但是 AC 损耗却最小。这是因为,导通/关断期间低侧 FET 的电压因 FET 体二极管而非常地低。因此,需要选择一个低导通电阻的 FET,并且栅极电荷可以很高。图 7 显示了上述情况。

图 7—低占空比设计的高侧和低侧 FET 功耗

如果我们降低输入电压,则我们可以得到一个高占空比设计,其高侧 FET 大多数时候均为导通状态,如图 8 所示。这种情况下,DC 损耗较高,要求低导通电阻。根据不同的输入电压,AC 损耗可能并不像低侧 FET 时那样重要,但还是没有低侧 FET 那样低。因此,仍然要求适当的低栅极电荷。这要求在低导通电阻和低栅极电荷之间做出妥协。就低侧 FET 而言,导通时间最短,且 AC 损耗较低,因此我们可以按照价格或者体积而非导通电阻和栅极电荷原则,选择正确的 FET。

图 8—高占空比设计的高侧和低侧 FET 功耗

假设一个负载点 (POL) 稳压器时我们可以规定某个中间电压轨的额定输入电压,那么最佳解决方案是什么呢,是高输入电压/低占空比,还是低输入电压/高占空比呢?使用不同输入电压对占空比进行调制,同时查看 FET功耗情况。

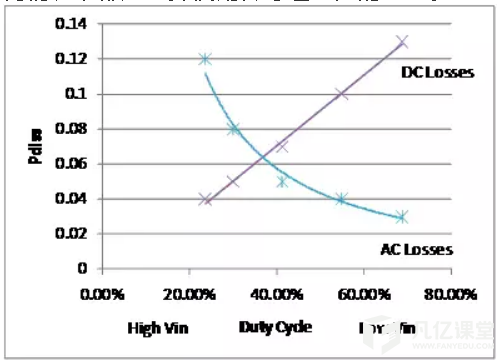

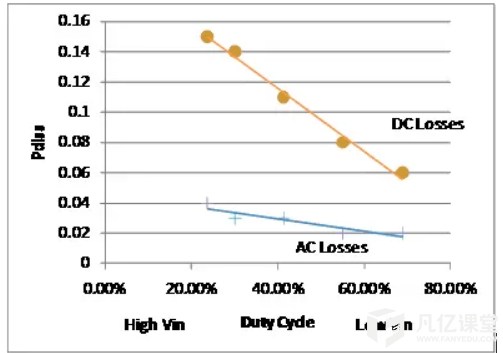

图 9 中,高侧 FET 反应曲线图表明,占空比从 25% 增至 40% 时 AC 损耗明显降低,而DC 损耗却线性增加。因此,35% 左右的占空比,应为选择电容和导通电阻平衡FET的理想值。不断降低输入电压并提高占空比,可以得到最低的AC 损耗和最高的 DC 损耗,就此而言,我们可以使用一个低导通电阻的 FET,并折中选择高栅极电荷。如低侧 FET 图 10 所示,控制器占空比由低升高时 DC 损耗线性降低(低侧 FET 导通时间更短),高控制器占空比时损耗最小。整个电路板的AC 损耗都很低,因此任何情况下都应选择使用低导通电阻的 FET。

图 9—高侧FET 损耗与占空比的关系

图 10—低侧 FET 损耗与控制器占空比的关系。请注意:低侧 FET 占空比为 1-控制器占空比,因此低侧 FET 导通时间随控制器占空比增加而缩短

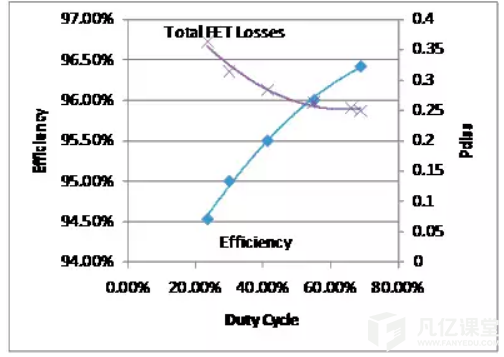

图 11 显示了我们将高侧和低侧损耗组合到一起时总效率的变化情况。我们可以看到,这种情况下,高占空比时组合 FET 损耗最低,并且效率最高。效率从 94.5% 升高至 96.5%。不幸的是,为了获得低输入电压,我们必须降低中间电压轨电源的电压,使其占空比增加,原因是它通过一个固定输入电源供电。因此,这样可能会抵消在 POL 获得的部分或者全部增益。另一种方法是不使用中间轨,而是直接从输入电源到 POL 稳压器,目的是降低稳压器数。这时,占空比较低,我们必须小心地选择 FET。

图 11—总损耗与效率和占空比的关系

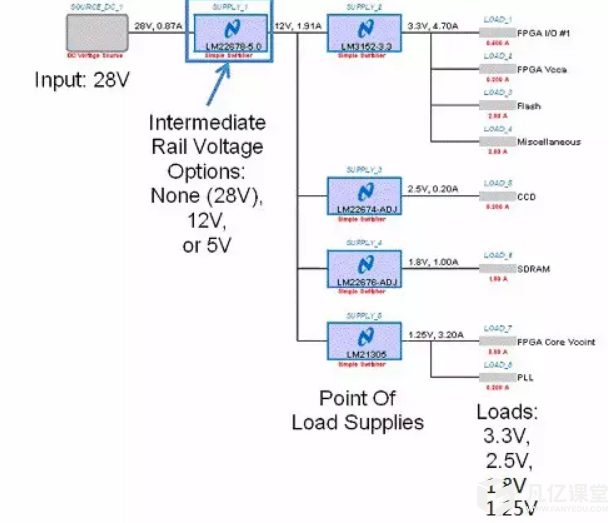

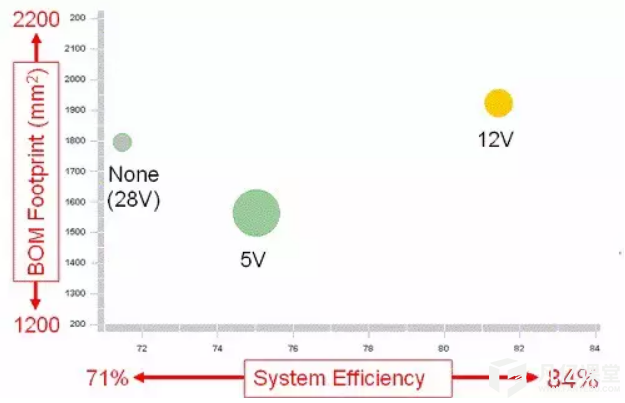

在有多个输出电压和电流要求的电源系统中,情况会更加复杂。对比不同 POL 稳压器占空比的效率、成本和体积。图 12 显示了一个系统,其输入电压为 28V,共有 8 个负载,4 个不同电压,范围为 3.3V 到 1.25V。共有 3 种对比方法:1)无中间轨,直接通过输入电源提供 28V 电压,以实现 POL 稳压器的低占空比;2)使用 12V 中间轨,POL稳压器中等占空比;3)使用 5V 中间轨,高 POL 稳压器占空比。图 13 和表 1 显示了对比结果。这种情况下,无中间轨电源的构架实现了最低成本,12V中间轨电压的构架获得了最高效率,而 5V 中间轨电压构架则实现了最小体积。因此,我们可以看到,对于这种大型系统而言,单POL电源情况下我们所看到的这些参数均没有明显的趋向。这是因为,使用多个稳压器时,除中间轨稳压器本身以外,每个稳压器都有其不同的负载电流和电压要求,而这些需求可能会相互冲突。研究这种情况的最佳方法是使用如 WEBENCH 电源设计师等工具,对不同的选项进行评估

图 12—表明输入、中间轨、负载点 (POL) 电源和负载的电源系统。中间轨电压的不同选择为 28V(直接使用输入电源)、12V 和 5V。这会带来不同的 POL 稳压器占空比。

图 13 电源设计曲线图,其表明中间轨电压对电源系统效率、体积和成本的影响。圆直径为 BOM(材料清单)价格。

轨电压 | 效率 | BOM 面积 (mm2) | BOM 成本 |

28V 输入 | 71.5% | 1795 | $15.14 |

12V | 81.4% | 1923 | $16.35 |

5V | 75.0% | 1564 | $18.52 |

表 1—中间轨电压对电源系统效率、体积和成本的影响。

暂无评论