凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片【经验分享】PCB差分信号设计中的3个常见误区

在高速PCB设计中,差分信号(Differential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。

布线要求

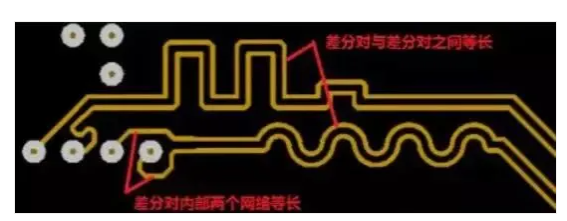

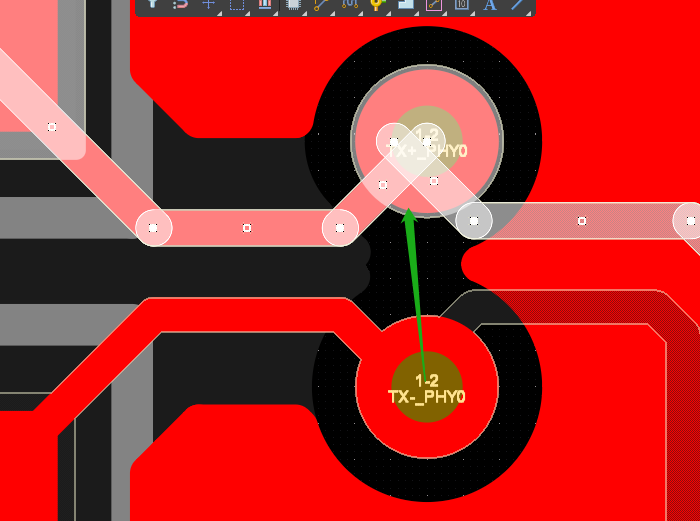

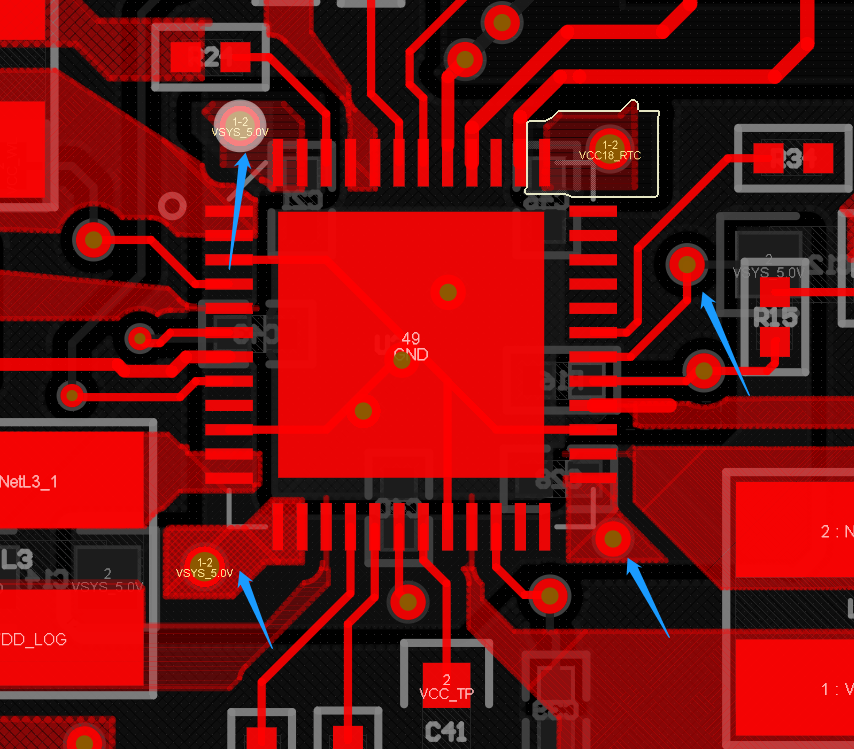

在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

▶ 等长:

等长是指两条线的长度要尽量一样长,是为了保证两个差分信号时刻保持相反极性。减少共模分量。▶ 等宽、等距:

等宽是指两条信号的走线宽度需要保持一致,等距是指两条线之间的间距要保持不变,保持平行。▶ 阻抗最小变化:

在设计具有差分信号的PCB时,最重要的事情之一是找出应用的目标阻抗,然后相应地规划差分对。此外,保持尽可能小的阻抗变化。差分线的阻抗取决于诸如走线宽度,走线耦合,铜厚度以及PCB材料和层叠等因素。当你尝试避免改变差分对阻抗的任何事情时,请考虑其中的每一个。常见误区

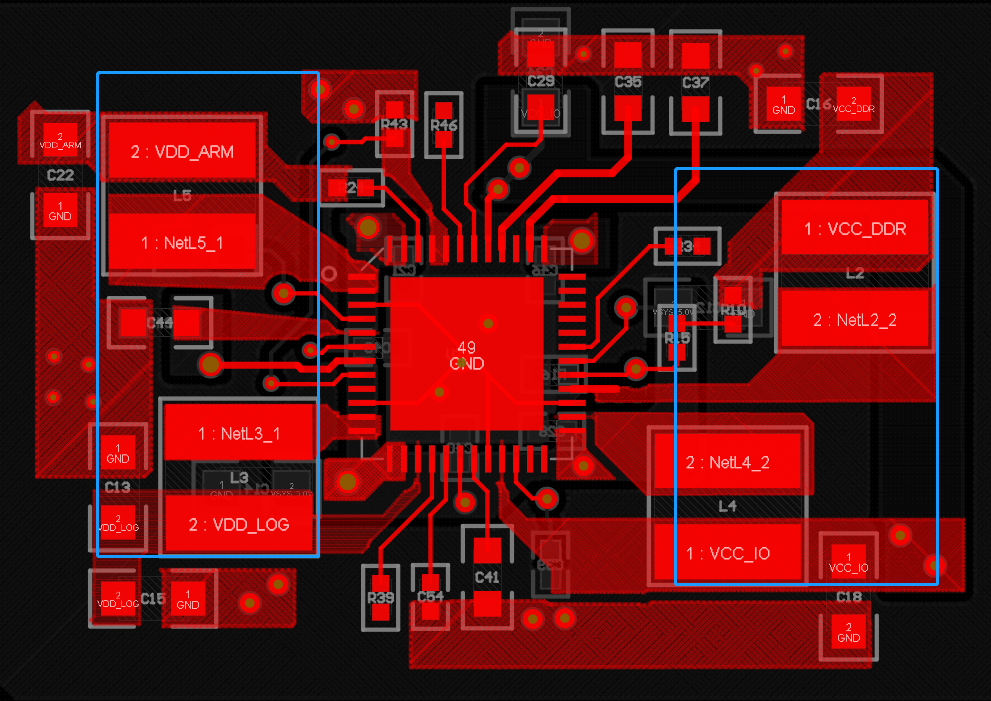

▶ 误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走线彼此为对方提供回流途径。

造成这种误区的原因是被表面现象迷惑,或者对高速信号传输的机理认识还不够深入。差分电路对于类似地以及其它可能存在于电源和地平面上的噪音信号是不敏感的。

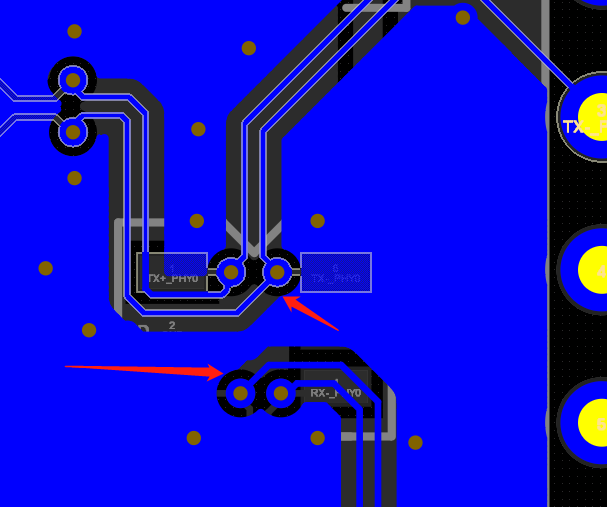

地平面的部分回流抵消并不代表差分电路就不以参考平面作为信号返回路径,其实在信号回流分析上,差分走线和普通的单端走线的机理是一致的,即高频信号总是沿着电感最小的回路进行回流,最大的区别在于差分线除了有对地的耦合之外,还存在相互之间的耦合,哪一种耦合强,哪一种就成为主要的回流通路。

▶ 误区二:认为保持等间距比匹配线长更重要。

PCB差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。

▶ 误区三:认为差分走线一定要靠的很近。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论