学习了很多硬件的知识,但仍不能随心所欲的设计出想要的电路,这是困扰了很多人的问题。追根到底,我们缺少的不是理论知识而是设计电路的思路,以及实战经验。在设计一款硬件电路时,除了需要掌握硬件设计基础、各种设计软件、工具操作技能等等,更重要的是养成一个良好的硬件电路设计思路,这能帮助你更好的、有针对性的去完成它。如何培养硬件电路的设计思路,下面为大家整理了设计的基本流程。

总体思路

设计硬件电路,大的框架和架构要搞清楚,但要做到这一点还真不容易。有些大框架也许自己的老板、老师已经想好,自己只是把思路具体实现;但也有些要自己设计框架的,那就要搞清楚要实现什么功能,然后找找有否能实现同样或相似功能的参考电路板(要懂得尽量利用他人的成果,越是有经验的工程师越会懂得借鉴他人的成果)。

理解电路

如果你找到了的参考设计,那么恭喜你,你可以节约很多时间了(包括前期设计和后期调试)。马上就copy?NO,还是先看懂理解了再说,一方面能提高我们的电路理解能力,而且能避免设计中的错误。

没有找到参考设计?

没关系。先确定大IC芯片找datasheet,看其关键参数是否符合自己的要求,哪些才是自己需要的关键参数,以及能否看懂这些关键参数,都是硬件工程师的能力的体现,这也需要长期地慢慢地积累。这期间,要善于提问,因为自己不懂的东西,别人往往一句话就能点醒你,尤其是硬件设计。

设计硬件电路

硬件电路设计主要是三个部分:原理图、pcb 以及物料清单(BOM)表。原理图设计就是将前面的思路转化为电路原理图,它很像我们教科书上的电路图。pcb涉及到实际的电路板,它根据原理图转化而来的网表(网表是沟通原理图和pcb之间的桥梁),而将具体的元器件的封装放置(布局)在电路板上,然后根据飞线(也叫预拉线)连接其电信号(布线)。完成了 pcb布局布线后,要用到哪些元器件应该有所归纳,所以我们将用到BOM表。

用什么工具?

Protel,也就是alTImuml容易上手,在国内也比较流行,应付一般的工作已经足够,适合初入门的设计者使用。其实无论用简单的protel或者复杂的cadence工具,硬件设计大环节是一样的(protel上的操作类似windwos,是post- command型的;而cadence的产品allegro是pre-command型的,用惯了protel突然转向cadence的工具,会不习惯就是这个原因)。

设计流程

原理图库建立

要将一个新元件摆放在原理图上,我们必须得建立元件的库。库中主要定义了该新元件的管脚定义及其属性,并且以具体的图形形式来代表(我们常常看到的是一个矩形(代表其IC BODY),周围许多短线(代表IC管脚))。protel创建库及其简单,而且因为用的人多,许多元件都能找到现成的库,这一点对使用者极为方便。应搞清楚ic body、ic pins、input pin、output pin、analog pin、digital pin、power pin等区别。

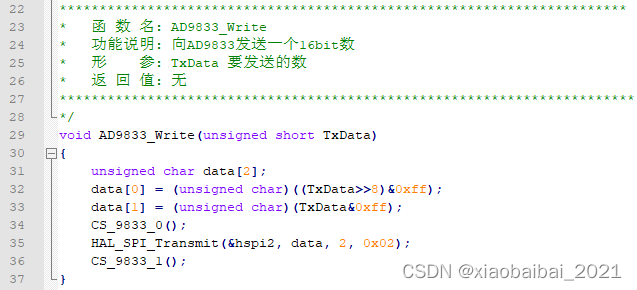

画原理图

有了充足的库之后,就可以在原理图上画图了,按照datasheet和系统设计的要求,通过wire把相关元件连接起来,在相关的地方添加line和text注释。wire和line的区别在于,前者有电气属性,后者没有。wire适用于连接相同网络,line适用于注释图形。这个时候,应搞清一些基本概念,如:wire、line、bus、part、footprint等等。

例如,post-command,例如我们要拷贝一个object(元件),我们要先选中这个object,然后按ctrl+C,然后按ctrl+V(copy命令发生在选中object之后)。这种操作windows和protel都采用的这种方式。但是allegro就是另外一种方式,我们叫做pre-command。同样我们要拷贝一个东西,先按ctrl+C,然后再选中object,再在外面单击(copy命令发生在选中 object之前)。

生成netlist

做完上一步,我们就可以生成netlist了,这个netlist是原理图与pcb之间的桥梁。原理图是我们能认知的形式,电脑要将其转化为pcb,就必须将原理图转化它认识的形式netlist,然后再处理、转化为pcb。

电气规则检查

得到netlist马上画pcb?别急,先做ERC先,ERC是电气规则检查的缩写。它能对一些原理图基本的设计错误进行排查,如多个output接在一起等问题。(但是一定要仔细检查自己的原理图,不能过分依赖工具,毕竟工具并不能明白你的系统,它只是纯粹地根据一些基本规则排查。)

获得pcb

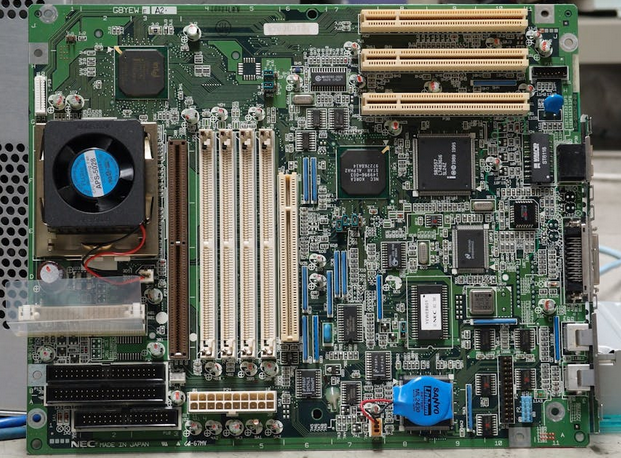

从netlist得到了pcb,一堆密密麻麻的元件,和数不清的飞线是不是让你吓了一跳?别急还得慢慢来。

确定板框大小

在keepout区(或mechanical区)画个板框,这将限制了你布线的区域。需要根据需求好考虑板长,板宽(有时,还得考虑板厚)。当然了,叠层也得考虑好。(叠层的意思就是,板层有几层,怎么应用,比如板总共4层,顶层走信号,中间第一层铺电源,中间第二层铺地,底层走信号)。

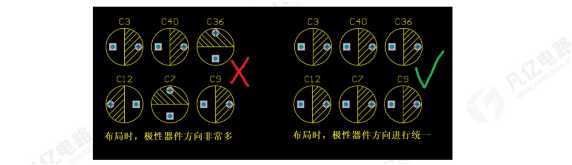

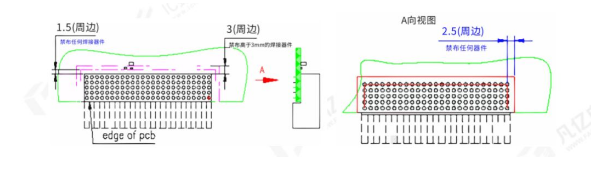

布局

确定完板框之后,就该元件布局(摆放)了,布局这步极为关键。它往往决定了后期布线的难易。哪些元器件该摆正面,哪些元件该摆背面,都要有所考量。但是这些都是一个仁者见仁,智者见智的问题,从不同角度考虑摆放位置都可以不一样。其实自己画了原理图,明白所有元件功能,自然对元件摆放有清楚的认识(如果让一个不是画原理图的人来摆放元件,其结果往往会让你大吃一惊^_^)。对于初入门的,注意模拟元件,数字元件的隔离,以及机械位置的摆放,同时注意电源的拓扑就可以了。

布线

接下来就是布线,这与布局往往是互动的,有经验的人往往在开始就能看出哪些地方能布线成功,如果有些地方难以布线还需要改动布局。对于fpga设计来说往往还要改动原理图来使布线更加顺畅。布线和布局问题涉及的因素很多,对于高速数字部分,因为牵扯到信号完整性问题而变得复杂,但往往这些问题又是难以定量或即使定量也难以计算的。所以,在信号频率不是很高的情况下,应以布通为第一原则。

布局布线之后需要注意的问题

OK了?别急,用DRC检查检查先,这是一定要检查的。DRC对于布线完成覆盖率以及规则违反的地方都会有所标注,按照这个再一一的排查,修正。有些pcb还要加上敷铜(可能会导致成本增加),将出线部分做成泪滴(工厂也许会帮你加),最后的pcb文件转成gerber文件就可交付pcb生产了。(有些直接给pcb也成,工厂会帮你转gerber)。

要装配pcb准备bom表,一般能直接从原理图中导出。但是需要注意的是,原理图中哪些部分元件该上,哪些部分元件不该上,要做到心理有数。对于小批量或研究板而言,用excel自己管理倒也方便(大公司往往要专业软件来管理)。而对于新手而言,第一个版本,不建议直接交给装配工厂或焊接工厂将bom 的料全部焊上,这样不便于排查问题。最好的方法就是,根据bom表自己准备好元件。等到板来了之后,一步步上元件、调试。

功能调试

拿到板第一步做什么,不要急急忙忙供电看功能,硬件调试不可能一步调试完成的。先拿万用表看看关键网络是否有不正常,主要是看电源与地之间有否短路(尽管生产厂商已经帮你做过测试,这一步还是要自己亲自看看,有时候看起来某些步骤挺繁琐,但是可以节约你后面不少时间!),其实短路与否不光pcb有关,在生产制作的任何一个环节可能导致这个问题,IO短路一般不会造成灾难性的后果,但是电源短路就......

电源网络没短路?那么好,那就看看电源输出是否是自己理想的值,对于初学者,调试的时候最好IC一件件芯片上,第一个要上的就是电源芯片。

电源网络短路了?这个比较麻烦,不过要仔细看看自己原理图是否有可能这样的情况,同时结合割线的方法一步步排查到底是什么地方短路了,是pcb的问题(一般比较烂的pcb厂就可能出现这种情况),还是装配的问题,还是自己设计的问题。

电源芯片没有输出?检查检查你的电源芯片输入是否正常吧,还需要检查的地方有使能信号、分压电阻、反馈网络等等。

电源芯片输出值不在预料范围?如果超过很离谱,比如到了10%,那么看看分压电阻先,这两个分压电阻一般要用1%的精度,这个你做到了没有,同时看看反馈网络吧,这也会影响你的输出电源的范围。

电源的输出跳变是否正常?电源输出正常了,别高兴,如果有条件的话,拿示波器看看吧,看看电源的输出跳变是否正常。也就是抓取开电的瞬间,看看电源从无到有的情况。

电源设计

无疑电源设计是整个电路板最重要的一环。电源不稳定,其他啥都别谈。在电源设计我们用得最多的场合是,从一个稳定的“高”电压得到一个稳定的“低”电压。

这也就是经常说的DC-DC(直流-直流),而直流-直流中用得最多的电源稳压芯片有两种,一种叫LDO(低压差线性稳压器,我们后面说的线性稳压电源,也是指它),另一种叫PWM(脉宽调制开关电源,我们在本文也称它开关电源)。我们常常听到PWM的效率高,但是LDO的响应快,这是为什么呢?别着急,先让我们看看它们的原理。

线性稳压电源和开关电源的比较

懂得了线性稳压电源和开关电源的工作原理之后,我们就可以明白为什么线性稳压电源有较小的噪声,较快的瞬态响应,但是效率差;而开关电源噪声较大,瞬态响应较慢,但效率高了。线性稳压电源内部结构简单,反馈环路短,因此噪声小,而且瞬态响应快(当输出电压变化时,补偿快)。但是因为输入和输出的压差全部落在了MOSFET上,所以它的效率低。因此,线性稳压一般用在小电流,对电压精度要求高的应用上。

而开关电源,内部结构复杂,影响输出电压噪声性能的因数很多,且其反馈环路长,因此其噪声性能低于线性稳压电源,且瞬态响应慢。但是根据开关电源的结构,MOSFET处于完全开和完全关两种状态,除了驱动MOSFET,和MOSFET自己内阻消耗的能量之外,其他能量被全部用在了输出(理论上L、C是不耗能量的,尽管实际并非如此,但这些消耗的能量很小)。

高速信号

高速看的是信号沿,不是时钟频率。 一般而言,时钟频率高的,其信号上升沿快,因此一般我们把它们当成高速信号;但反过来不一定成立,时钟频率低的,如果信号上升沿依然快的,一样要把它当成高速信号来处理。根据信号理论,信号上升沿包含了高频信息(用傅立叶变换,可以找出定量表达式),因此,一旦信号上升沿很陡,我们应该按高速信号来处理,设计不好很可能出现上升沿过于缓慢、有过冲、下冲、振铃的现象。

比如,I2C信号,在超快速模式下,时钟频率为1MHz,但是其规范要求上升时间或下降时间不超过120ns。因此,我们更应该关注的是信号带宽。根据经验公式,带宽与上升时间(10%~90%)的关系为 Fw * Tr = 3.5。

很多人注意到了示波器的采样率,没有注意到示波器的带宽,但往往示波器带宽是一个更重要的参数。一些人以为只要示波器采样率满足超过信号时钟频率的两倍就行了,这是大错特错,错误的原因是错误的理解了采样定理。采样定理说明了当采样频率大于信号最大带宽的两倍,就能完美地恢复原信号。但是,采样定理指的信号是带限信号(带宽是有限的),与现实中的信号严重不符。

我们一般的数字信号,除了时钟之外都不是周期的,从长时间来看,其频谱是无限宽的,要能捕获到高速信号,就不能对其高频分量太多的失真。示波器带宽指标与此息息相关。因此,真正要注意的依然是用示波器捕获的信号的上升沿失真在我们可接受的范围。

那么选多高带宽的示波器才合适呢?理论上5倍于信号带宽的示波器捕获的信号比原信号损失不到3%。如果要求损失更宽松,那就可以选择更低端的示波器。用到3倍于信号带宽的示波器应该能满足大多数要求,但是不要忘了你探头的带宽。

暂无评论