反射引起的振铃效应——电路谐振

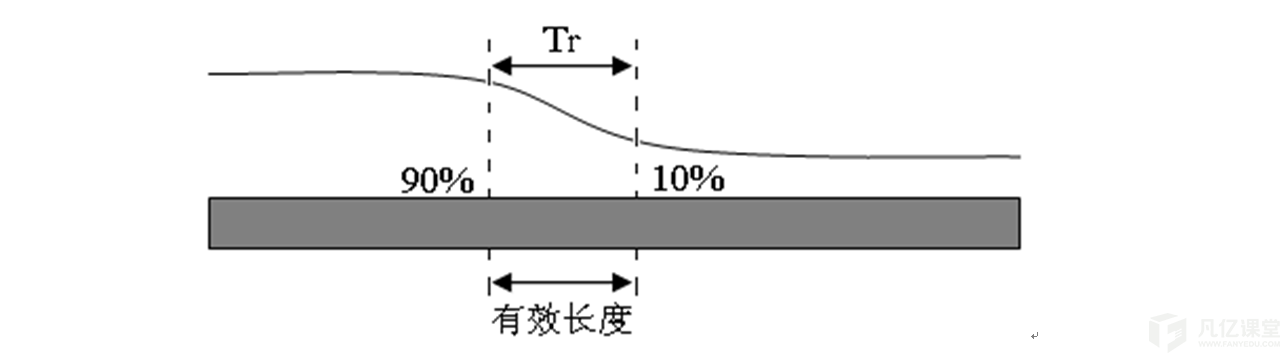

在研究由反射引起的振铃效应前,先讨论由电路谐振引起的振铃效应。在时钟速度高达10MHz的数字系统中,振铃(Ringing)现象是设计中的显著问题。传导系统对输入信号的响应,在很大程度上取决于系统的尺寸是否小于信号中最快的电气特性的有效长度,反之亦然。电气特性的有效长度由它的持续时间和传播延迟决定,即l=Tr/D(Tr =上升时间,ps;D=延迟,ps/in)。如果走线长度小于有效长度的1/6,该电路表现为集总系统,如果系统对输入脉冲的响应是沿走线分布的,称之为分布系统。

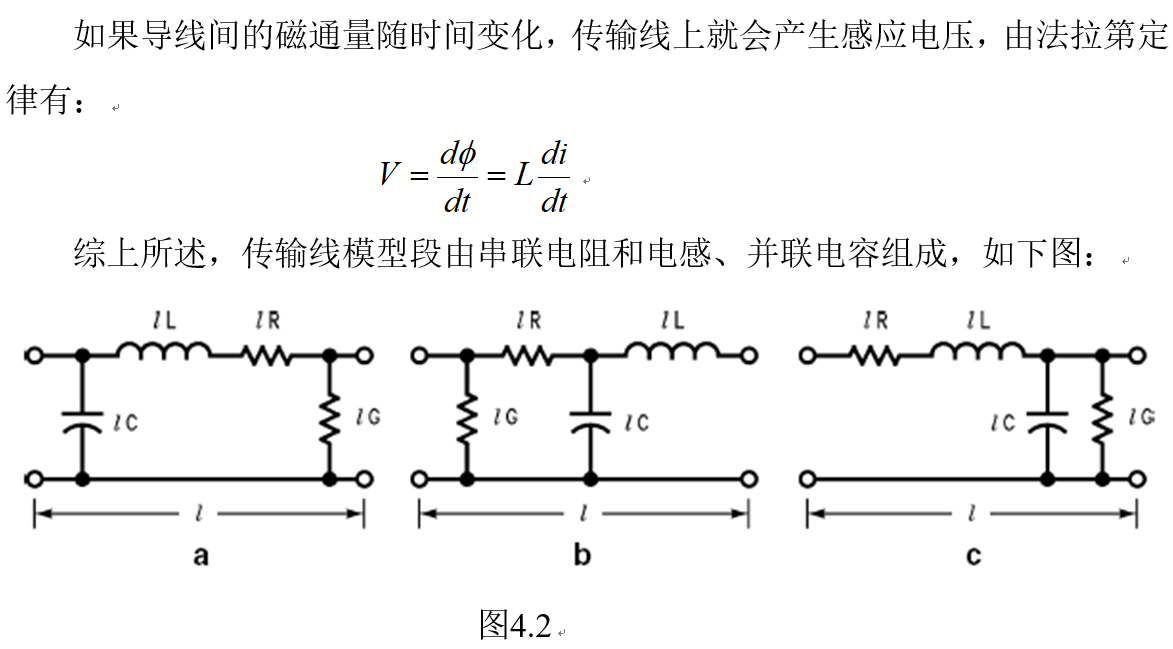

对于不同长度的印制板布线,有不同的处理方法。一般来说,长度小于2英寸的走线的电气特性更像集总参数的LC电路;长度大于8英寸的走线的电气特性更像分布参量的传输线电路。为了消除以振铃噪声,对于不同长度的走线有不同的处理措施,这些措施和印制版走线的等效电路模型有关。

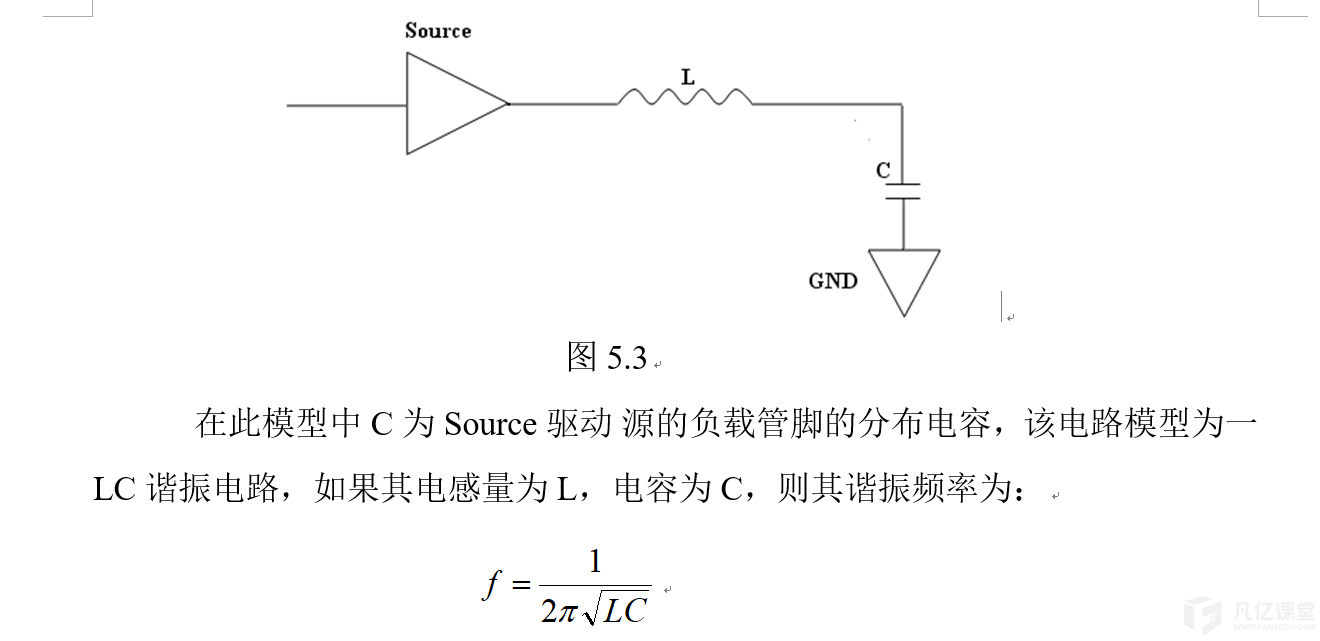

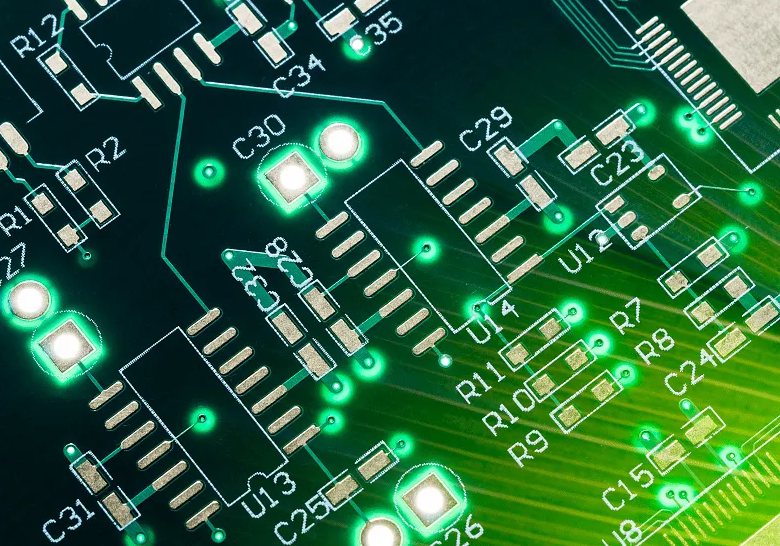

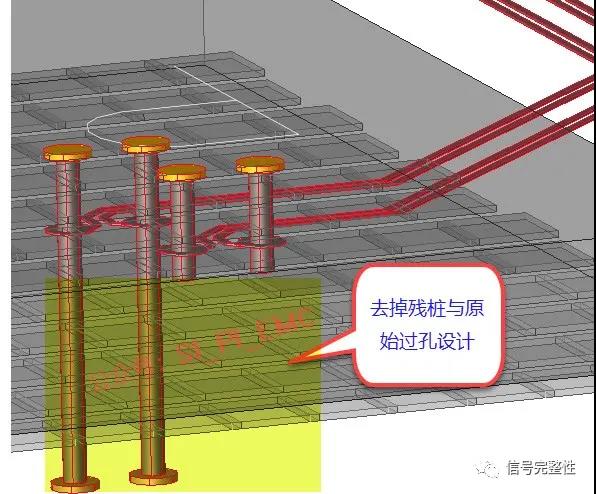

印制版的走线类似于谐振电路,由板上的铜铂提供电感,负载提供电容,同时铜铂依其长度有分布电感存在。下图即为其简化模型:

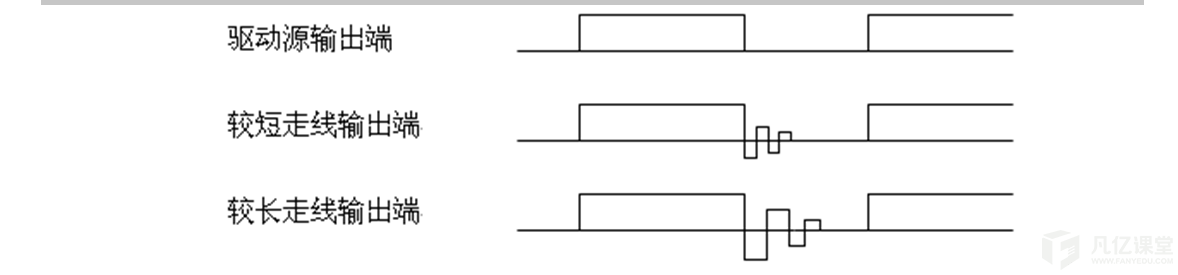

振铃噪声大致正比于谐振周期和时钟沿上升/下降时间的比值。当走线很短时,电感量和分布电容量都很小,这样谐振频率很高,谐振周期很短,振铃的幅度亦很小。当走线长度增加时,电感量和分布电容量都加大,谐振周期变长,振铃幅度也加大,此时对电路的正常工作会产生较大的影响。如下图所示:

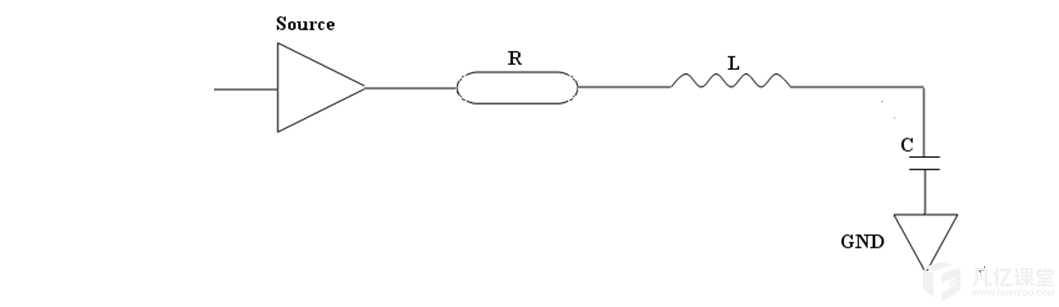

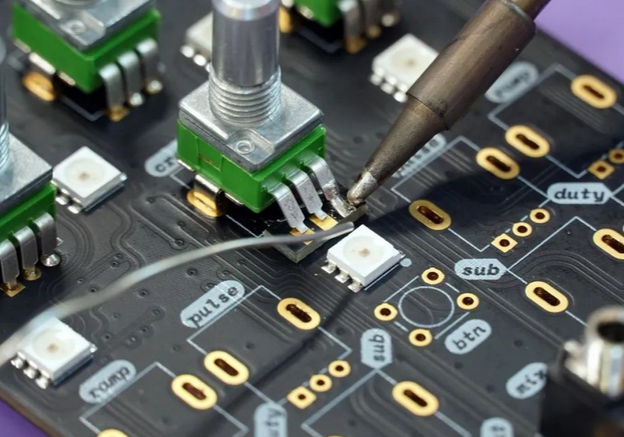

减小振铃噪声的一种有效手段是在电路中串联一个小电阻,此时电路模型变为下图:

显然,该电阻为谐振电路提供了阻尼,该阻尼电阻能显著减小振铃幅度,缩短振铃震荡时间,同时几乎不影响电路速度。在工程使用上,该电阻通常为25欧姆。

理论上,电平从高到低跳变和从低到高跳变都会引起振铃,但是在典型的TTL电路中,从高到低的电平跳变引起的振铃现象更为显著。这是因为相对于从低到高的电平跳变,CMOS和TTL的输出级在从高到低的跳变时有更强的驱动能力,同时其等效的输出阻抗更小,一般只有3-10欧姆,这样就不能为谐振回路提供强的阻尼,所以从高到低的跳变 引起的振铃较剧烈,对电路的影响也较大。同时TTL电平对高低门限有不同耐受程度:典型的逻辑信号在高电平时有3.5V,而在低电平时为0.2V,而高低电平门限为1.4V,所以在从低到高的跳变产生的振铃必须有(3.5-1.4=2.1V)的幅度才会产生数据错误;而从高到低的振铃幅度只要有(1.4-0.2=1.2V)就会产生数据错误。

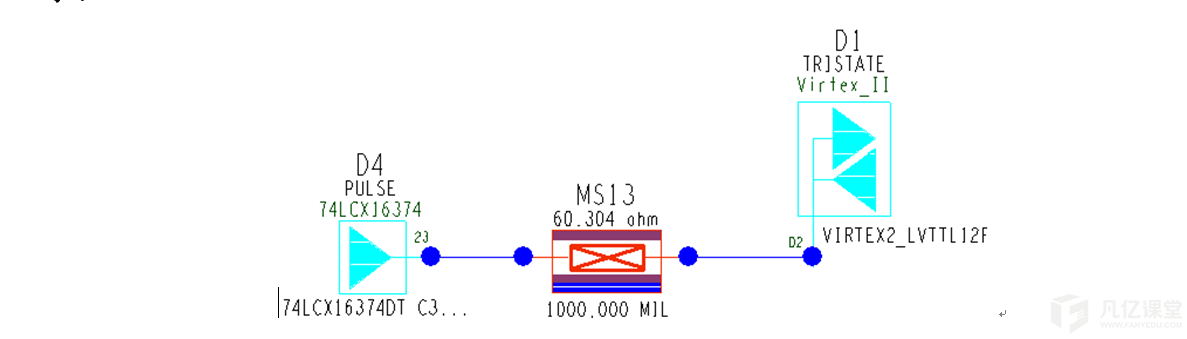

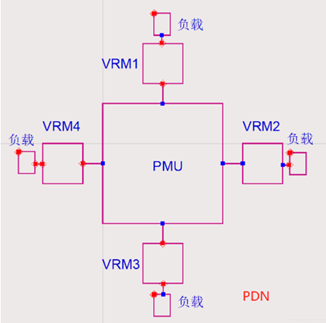

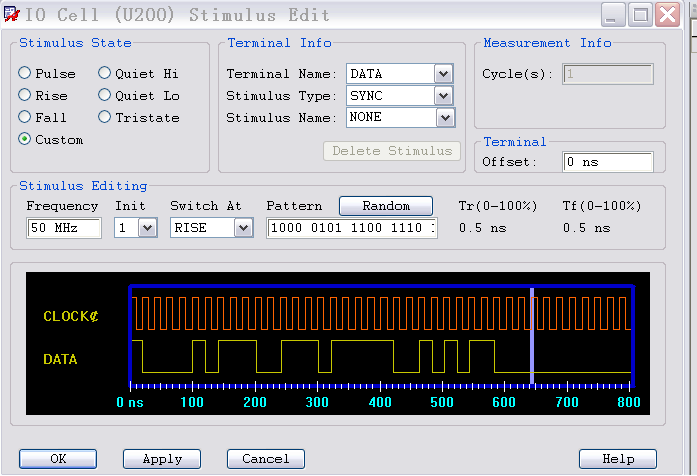

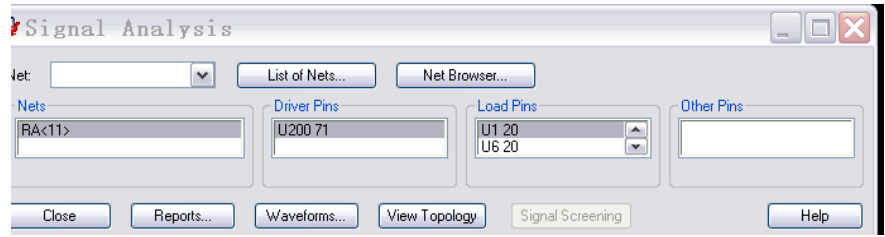

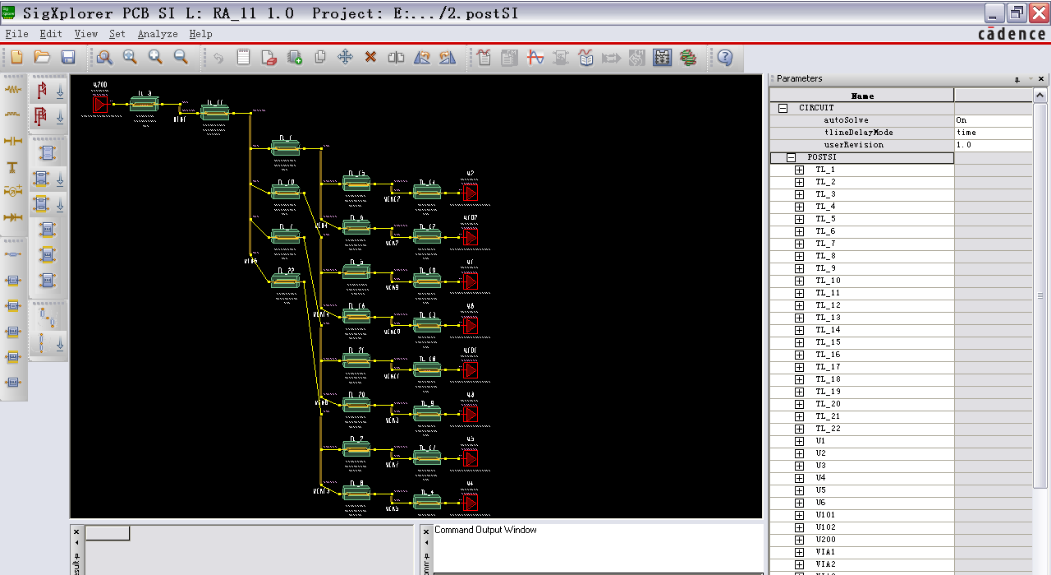

对长度小于2英寸,线宽10mil的走线进行仿真,发射端为74LCX16374芯片NO.23引脚,接收端为Virtex_ⅡNO.D2引脚,激励为100MHZ的方波,如下图所示:

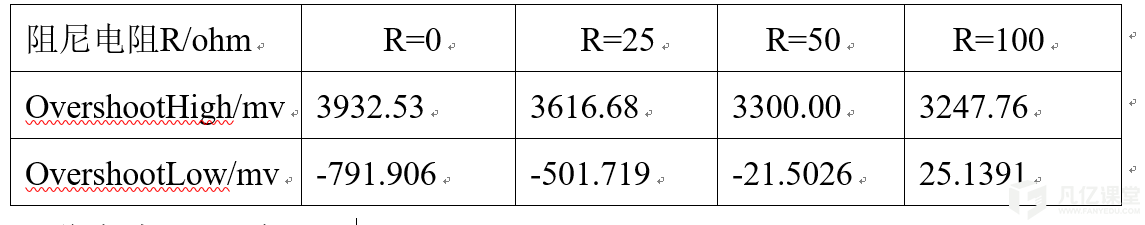

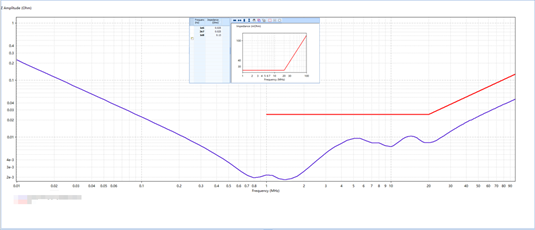

在不加阻尼电阻、加入阻尼电阻R=25ohm、R=50ohm、R=100ohm的情况下得到的仿真结果如下表:

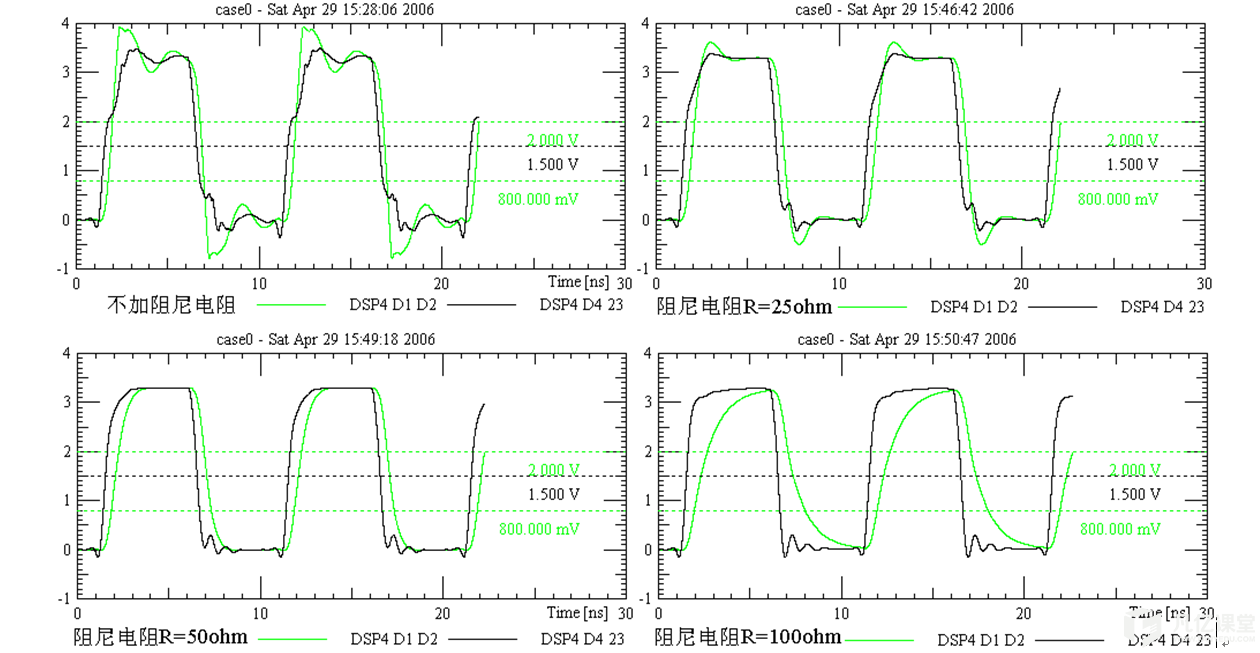

仿真波形对比如下:

从上图可看出,在接收端波无阻尼电阻时波形有明显的振铃效应存在,为了减小振铃效应,在发射端与接收端之间加入阻尼电阻后,振铃效应有明显的改善,随着R的增大,振铃的幅度和次数逐渐减少,对于波形的改善有一定效果。

暂无评论