我们在电源滤波电路上可以看到各种各样的电容,100uF、10uF、100nF、10nF不同的容值,那么这些参数是如何确定的?

数字电路要运行稳定可靠,电源一定要”干净“,并且能量补充一定要及时,也就是滤波去耦一定要好。什么是滤波去耦,简单的说就是在芯片不需要电流的时候存储能量,在需要电流的时候又能及时地补充能量。有读者看到这里会说,这个职责不是DC/DC、LDO的吗?对,在低频的时候它们可以搞定,但高速的数字系统就不一样了。

先来看看电容,电容的作用简单来说就是存储电荷。我们都知道在电源中要加电容滤波,在每个芯片的电源脚放置一个0.1uF的电容去耦。但是,怎么有些板子芯片的电源脚旁边的电容是0.1uF的或者0.01uF的,有什么讲究吗?

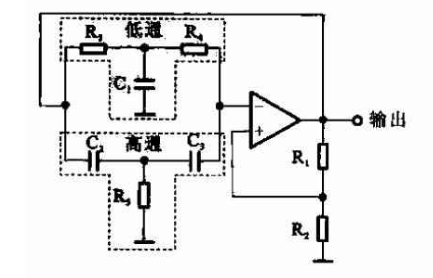

要搞懂这个道道就要了解电容的实际特性。理想的电容它只是一个电荷的存储器,即C,而实际制造出来的电容却不是那么简单。分析电源完整性的时候我们常用的电容模型如图1所示。

图 1

图1中,ESR是电容的串联等效电阻,ESL是电容的串联等效电感,C才是真正的理想电容。ESR和ESL是由电容的制造工艺和材料决定的,没法消除。那这两个东西对电路有什么影响?ESR影响电源的纹波,ESL影响电容的滤波频率特性。

我们知道:

电容的容抗:Zc=1/ωC

电感的感抗:Zl=ωL,ω=2πf

实际电容的复阻抗为:

Z=ESR+jωL-1/jωC

=ESR+j2πf L-1/j2πf C

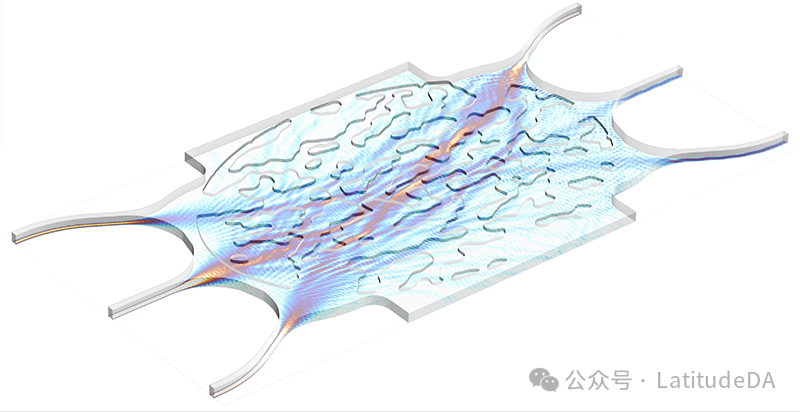

可见,当频率很低的时候是电容起作用,而频率高到一定程度电感的作用就不可忽视了;再高的时候电感就起主导作用了,电容就失去滤波的作用了。所以记住,高频的时候电容就不是单纯的电容了。实际电容的滤波曲线如图2所示。

图 2

上面说了,电容的等效串联电感是由电容的制造工艺和材料决定的。实际的贴片陶瓷电容,ESL从零点几nH到几个nH不等,封装越小ESL就越小。

从图2中看出,电容的滤波曲线并不是平坦的,它像一个’V’,也就是说有选频特性。有时候我们希望它越平越好(前级的板级滤波),而有时候希望它越尖越好(滤波或陷波)。

影响这个特性的是电容的品质因素Q:Q=1/ωCESR

ESR越大,Q就越小,曲线就越平坦;反之ESR越小,Q就越大,曲线就越尖。

通常钽电容和铝电解有比较小的ESL,而ESR大,所以钽电容和铝电解具有很宽的有效频率范围,非常适合前级的板级滤波。也就是说,在DC/DC或者LDO的输入级,常常用较大容量的钽电容来滤波。而在靠近芯片的地方放一些10uF和0.1uF的电容来去耦,陶瓷电容有很低的ESR。

说了那么多,那到底在靠近芯片的管脚处放置0.1uF还是0.01uF?下面列出来给大家参考。

频率范围/Hz

电容取值DC-100K

10uF以上的钽电容或铝电解

100K-10M

100nF(0.1uF)陶瓷电容10M~100M10nF(0.01uF)陶瓷电容>100M

1nF(0.001uF)陶瓷电容、PCB电源与地间的电容

所以,以后不要见到什么都放0.1uF的电容,有些高速系统中这些0.1uF的电容根本就起不了作用。

声明:本文转载自网络,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

暂无评论