ReturnPath回流路径

高速设计已成为愈来愈多PCB设计人员关切的重点。在进行高速PCB设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路越大,这些信号愈有可能吸收来自系统中任何其他Net的噪声。

一般回流路径不连续问题常是由于缺少接地过孔Via、接地层中的间隙、缺少去耦电容,或是使用错误Net所引起的。而当你的PCB设计愈趋复杂,要快速找出这些问题难度也愈高。

本文将通过设计实例详解如何使用Allegro®PCBDesigner中IDA(In-DesignAnalysis,设计同步分析)的ReturnPath分析功能,在PCB设计过程中进行回流路径分析,帮助工程师快速找出那些高速信号的回流路径是否适当,以确保Layout的质量并且减少产品量产后因信号不稳而需要召回的重大损失,实现设计一次性成功。

本文重点

回流路径释义ReturnPath分析重要性ReturnPath分析实例详解ReturnPath分析结果解析

1、何谓回流路径(ReturnPath)

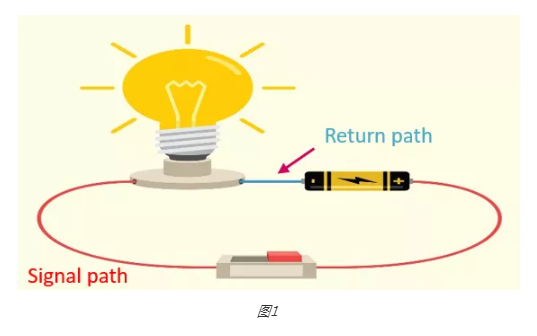

电气产品的运作需要有其信号的回路才能运行,就像下图(一)中电池的负极也要接那条蓝线过去电灯才会亮。早期,我们可以看到电报系统是把“大地”当作信号回路的地平面,可以少布另一条地线以减少昂贵成本。或若在现代生活中类似情况就是当车上要加装灯泡时,我们可以把“车壳”视作信号回路的地,将灯泡负极直接接至车壳就会亮,就可以省掉多布一条线的麻烦,且也不太需要考虑到回流路径问题。

不过若当要接上的是行车系统、CAN(车载网络系统)甚或是ADAS(先进驾驶辅助系统)上的各种感应或处理器,就不是直接接上、省掉导线这么单纯了,因较易涉及高频/高速传输,会必须要注意其回流路径的完整性。

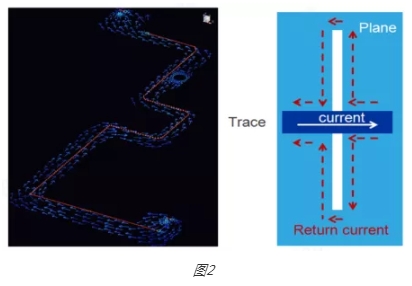

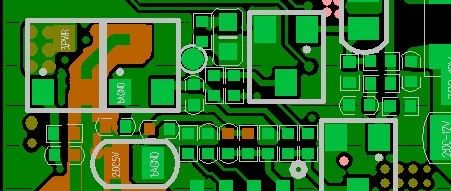

同样的!对PCB设计上来说,如果是低频信号其回流路径会随最低阻抗而返回,但随着频率拉高,电流需要以封闭回路回到源头,因而会更考虑最低电感的回流路径,并且通常会对应在其布线的上下层返回路径如下左图(二)示意,以避免如下右图(二)因内层切割而造成回流路径迂回的问题,所以高速信号的回流路径考虑就更显重要了。

2、什么需要ReturnPath分析?

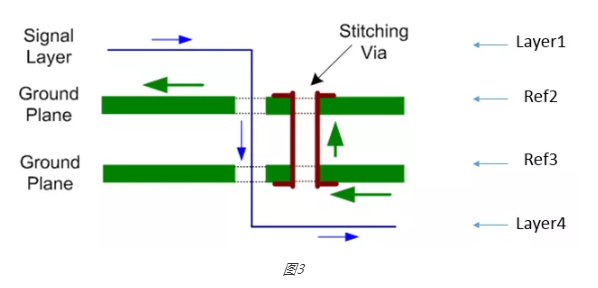

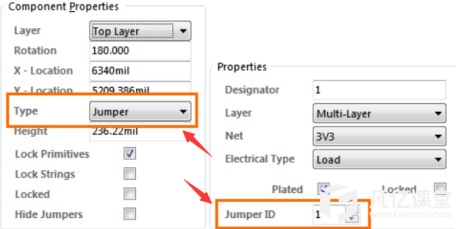

如上所述,考虑高速信号的回流路径至关重要,因稍一不慎就会大大减弱电路功能。一般而言,因为标准PCB的DRC检查只会检查鼠线有没接完和安全间距够不够这两种状况,所以像ReturnPath这样的分析就较不易实现,往往需有经验的老手开启相关的图层跟着看高速信号走线的相邻层来确保回流路径,管控Layout质量。亦或对Layout订立一些走线旁该怎么加STItchingVia的规范,STItchingVia的示意如下图(三),至于差动信号打Via后旁边要拱几个STItchingVia,那又是另外的故事了!

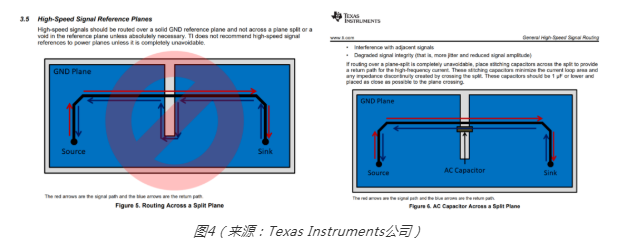

甚或是最后不得已需添加缝补电容以填补那些跨不过壕沟(Moat),而导致成本增加以完善回流路径,如下图(四)TI规范中的例子。

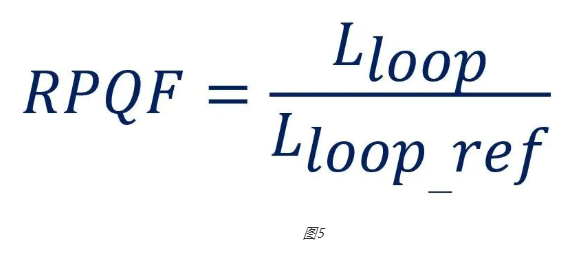

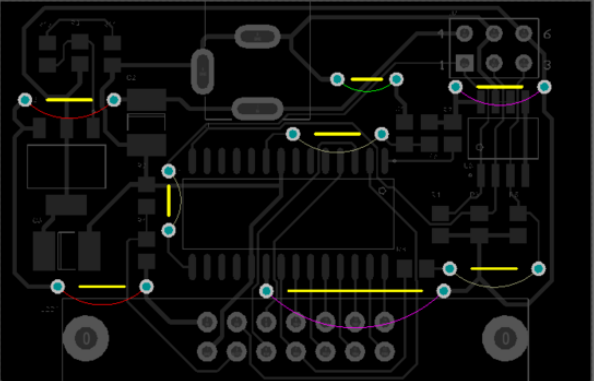

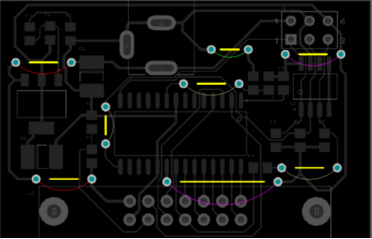

所以如果我们有个直观的辅助分析工具会依照信号的几何结构分析回流路径,并在不需Models的状况下,计算出其电感的比值RPQF(ReturnPathQualityFactor,回流路径质量系数)如下图五所示。

当RPQF值越趋近于1,则表示信号布线与与回流路径是越贴近的,越高则代表回流路径越曲折绕越远的路径。

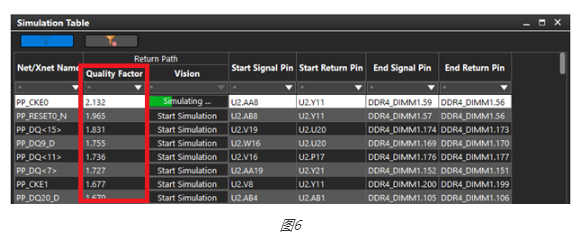

而且在执行分析完毕后可直接列出相关信号的RPQF值如下图六所示,让我们能快速识别各个信号的严重性,修正不理想的部分。

注:IDA(In-DesignAnalysis,设计同步分析)中另外的Impedance阻抗分析和Coupling耦合干扰分析,也是一样可以在不需Models的情况下,照着检查流程执行就可以很快实现各项Layout质量管控的快筛分析。

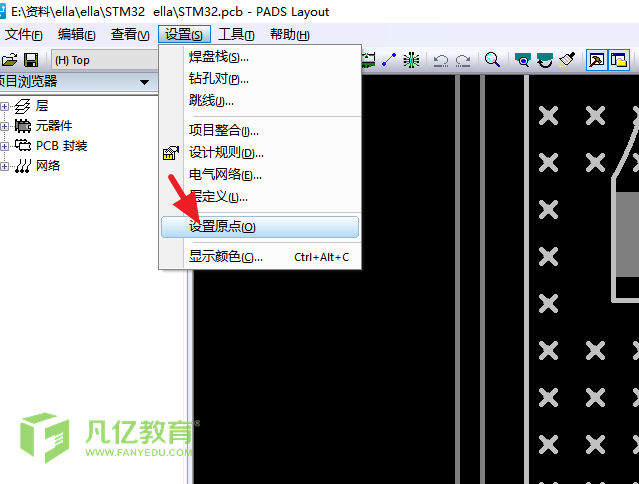

3、何执行ReturnPath分析

现在Allegro中导入了Sigrity专业的模拟分析技术,将IDA(In-DesignAnalysis,设计同步分析)带入PCB设计流程之中,帮助PCB工程师在设计中同步进行分析,预先找出常见的回流路径不连续问题,实时解决,快速确保信号回流路径的质量,使设计效率提升,不良机率减少。同样重要的是ReturnPath检查也是不需要Models并且只需简单的流程,就可轻易实现!

作者:EricChen来源:GraserCadence楷登PCB及封装资源中心

声明:本文由作者原创,文章内容系作者个人观点,电子发烧友网转载仅作为传达一种不同的观点,不代表电子发烧友网对该观点的赞同或支持,如有异议,欢迎联系电子发烧友网。

更多热点文章阅读

暂无评论