了解CMOS集成电路的技术参数及特性,有助于更好地帮助我们提高集成电路的设计效率,也能进一步巩固我们的自身基础知识,所以今天我们将详谈CMOS集成电路的技术参数及特性。

1.标称逻辑电平

门电路的逻辑功能是通过指定高电平表示1,低电平表示0来实现的。这种表示逻辑值1和0的理想电平值,记为U(1)和U(0),称为标称逻辑电平。标称逻辑电平分别为U( 1)=5V,U(0)=0V。

2.开门电平U0H与关门电平U0L

实际门电路中,高电平和低电平都不可能是标称逻辑电平,而是在偏离这一数值的一个范围内。若用非U(),非U(0)分别表示高低两个电平的两个允许偏离值,那么在偏离范围内都可称为1, 0。我们把表示逻辑值1的最小高电平UOH(min)称为开门电平,表示逻辑值0的最大低电平UOL(max)称为关门电平。

3.输入高电平电流IIH和输入低电平电流IIL

作为负载的门电路,当某一输入端输入高电平,其余输入端接低电平时,流入该输入端的电流称为拉出前级门电路输出端的电流。作为负载的门电路,当某一输入端输入低电平,其余输入端接高电平时,从该输入端流出的电流称为灌入前级输出端的电流。

4.输出高电平电流IOH和输出低电平电流I0L

I0H是指输出高电平时流出该输出端的电流,它反映了门电路带拉电流负载的能力。IOL是指输出低电平时流入该输出端的电流,它反映了门电路带灌电流负载的能力。

5.扇入系数Nr

门电路允许的输入端数月,称为该门电路的扇入系数。一般门电路的扇入系数为1-5,最多不超过8。实际应用中若要求门电路的输入端数目超过它的扇入系数,可使用与扩展器或者或扩展器来增加输入端数目,也可改用分级实现的方法。

实际应用中若要求门电路的输入端数目小于它的扇入系数,可将多余的输入端接高电平或低电平,这取决于门电路的逻辑功能。

6.扇出系数Nc

门电路通常只有一个输出端,但它能与下一级的多个门的输入端连接。一个门的输出端所能连接的下一级门输入端的个数称为该门电路的扇出系数,或称负载能力。TTL一般门电路的扇出系数为8,驱动门的扇出系数可达25。CMOS门的扇出系数更大一些。

7.平均传输延迟时间(ty)

平均传输延迟时间是反映门电路工作速度的一个重要参数。以与非门为例,在输入端加上一个正方波,则需要一定的时间间隔才能从输出端得到-一个负方波。若定义输入波形前沿的50%到输出波形前沿的50%之间的时间间隔t1为前沿延迟:同样,若定义t2为后沿延迟,则它们的平均值称为平均传输延迟时间,简称平均时延。

8.空载功耗.

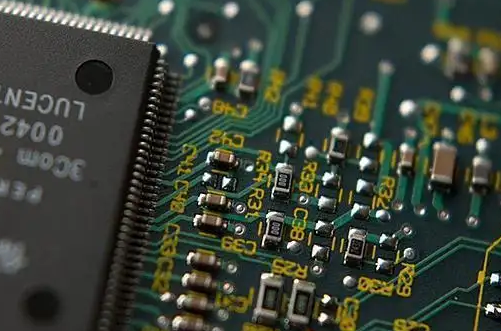

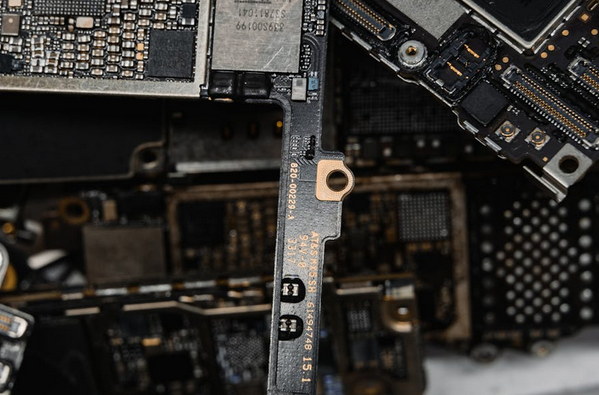

集成电路的功耗和集成密度密切相关。功耗大的的元器件集成度不能很高,否则,器件因无法散热而容易烧毁。

当输出端空载,门J电路输出低电平时电路的功耗称为空载导通功耗Pon。当输出端为高电平时,电路的功耗称为空载截止功耗Poff。平均功耗P=(Pon+Poff)/2。 例如74H系列TTL门电路,平均功耗为22亳瓦。而CMOS门电路平均功耗在微瓦数量级。

4000-→74C-→74HC-→74HCT, 74BCT[与TTL兼容]

暂无评论