同步电路和异步电路是常见的电子电路两大类,但由于小白经常将同步电路和异步电路混为一谈,导致在电路设计或面试过程中出错,所以了解同步电路和异步电路是很有必要的,接下来看看吧。

1、同步电路和异步电路的区别及联系

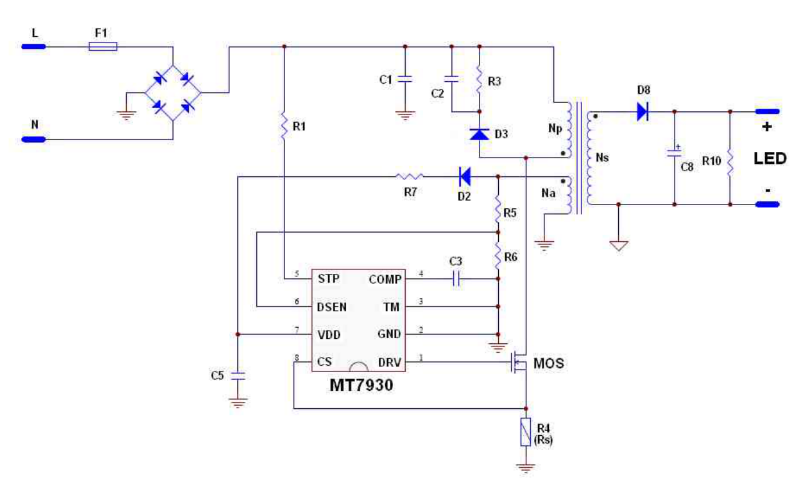

异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,但它同时也用在时序电路中,此时它没有统+的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。也就是说一- 个时刻允许一个输入发生变化,以避免输入信号之间造成的竞争冒险。电路的稳定需要有可靠的建立时间和持时间。

同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。比如D触发器,当上升延到来时,寄存器把D端的电平传到Q输出端。

在同步电路设计中一般采用D触发器,异步电路设计中一般采用Latch。

2、同步逻辑和异步逻辑的区别

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。电路设计可分类为同步电路和异步电路设计。同步电路利用时钟脉冲使其子系统同步运作,而异步电路不使用时钟脉冲做同步,其子系统是使用特殊的“开始”和“完成”信号使之同步。由于异步电路具有下列优点-无时钟歪斜问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性——因此近年来对异步电路研究增加快速,论文发表数以倍增,而Intel Pentium 4处理器设计,也开始采用异步电路设计。

异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,其逻辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路些时序电路共享同一个时钟C L K,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。

暂无评论