凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片如何解决异步时钟域数据同步的问题?

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?

处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要求,即尽量避免亚稳态的发生和传播,然而当系统存在已不远就,亚稳态问题将无可避免,因此我们设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感,可以通过下列方法来解决:

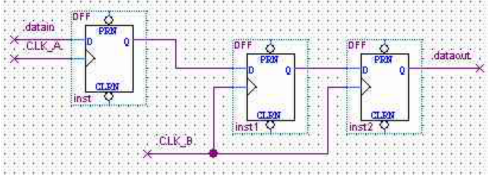

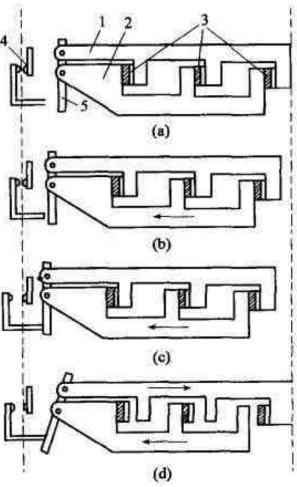

1、用触发器打两拍

如图所示,左边是异步输入端,经过两极触发器同步, 在右边的输出将是同步的,而且该输出基本不存在亚稳态。其原理是即使第一个触发器的输出端存在亚稳态,经过-一个CLK周期后,第二个触发器D端的电平仍未稳定的概率非常小,因此第二个触发器Q端基本不会产生亚稳态。然而,亚稳态是无法被根除的,一旦亚稳态发生,后果的严重程度依赖于你设计系统对产生的错误是否敏感。

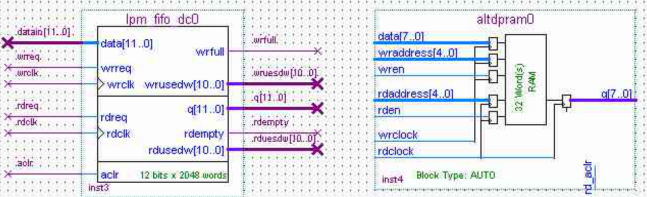

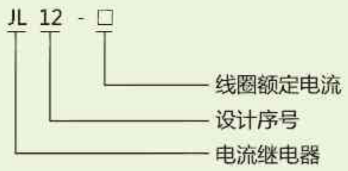

2、异步FIFO或DPRAM

因为异步FIFO或DPRAM使用格雷码计数器读写地址的指针,所以它可以很好地避免亚稳态的发生,使用方法是:将上级芯片提供的数据随路时钟作为写信号,将数据写入异步FIFO或DPRAM,然后使用本级的采样时钟数据独处即可。需要注意的是,当两级时钟频率不同时,需要设计好缓冲区,并通过监控full、half、empty、useword信号,保证数据不会溢出,也不会被读空。

3、调整时钟相位

该种方法的设计难度较大,且适用面有限,首先需对跨时钟域数据的路径进行详细的静态时序分析,然后将违反setup时间和hold时间的情况一一列出,在不影响其他设计性能的签一下,综合考虑调整两级时钟的相位关系,最终使其setup时间和hold时间满足要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论