在电子电路设计中,抑制电磁干扰是小白必学的基础知识之一,但有很多小白在电路设计中经常多走歪路,导致电路报废,费时费力费钱,所以本文将分享有用的电路设计技巧,可以帮助小伙伴们更快的完成电路设计。

目前产品的电磁兼容问题常常在检测机构对产品进行电磁兼容测试以后才去解决,甚至当产品使用后出现问题时才去补救。这样做非但费时费力,而且不能从根本上解决问题。因此,应该在产品开发的最初阶段就进行电磁兼容设计。由于PCB板上的电子器件密度越来越大,走线越来越窄,信号的频率越来越高,不可避免地会引入EMC(电磁兼容)和EMI(电磁干扰)。

所以,设计目的是使板上各部分电路之间没有相互干扰,并使印制板对外的传导发射和辐射发射尽可能降低,达到有关标准要求。外部的传导干扰和辐射干扰对板上的电路基本无影响,实际上在设计中采取正确的措施常常能同时直到抗干扰和抑制发射的作用。在设计印制电路板布线时,首先要选取印制板类型,然后确定元器件在板上的位置,再依次布置地线、电源线、高速信号线和低速信号线。

在EMC设计中,电容是应用最广泛的元件之一,主要用于构成各种低通滤波器或用作去耦电容和旁路电容。大量实践表明:在EMC设计中,恰当选择与使用电容,不仅可解决许多EMI问题,而且.能充分体现效果良好、价格低廉、使用方便的优点。若电容的选择或使用不当,则可能根本达不到预期的目的,甚至会加剧EMI程度。

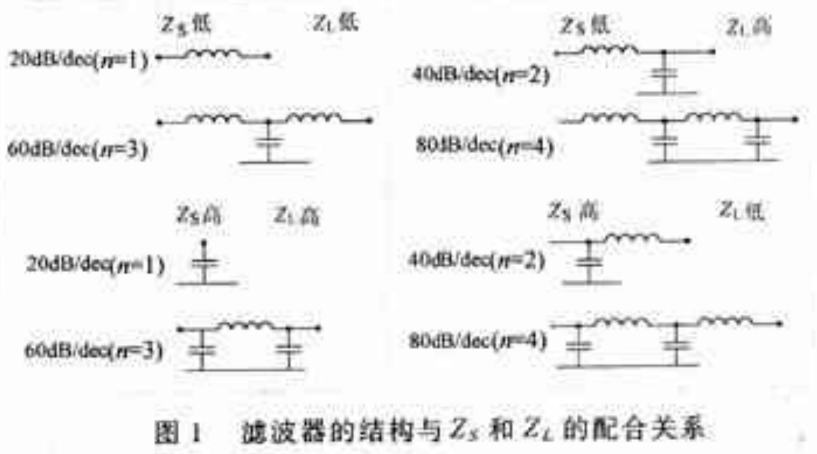

滤波器结构的选择EMC设计中的滤波器通常指由L,C构成的低通滤波器。不同结构的滤波器的主要区别之一,是其中的电容与电感的联接方式不同。滤波器的有效性不仅与其结构有关,而且还与连接的网络的阻抗有关。如单个电容的滤波器在高阻抗电路中效果很好,而在低阻抗电路中效果很差。

传统上,在滤波器两端的端接阻抗为50欧姆的条件下描述滤波器的特性(这一点往往未被注意),因为这样测试方便,并且是符合射频标准的。但是,实践中源阻抗Zs和负载阻抗Zi很复杂,并且在要抑制的频率点上可能是未知的。如果滤波器的一端或两端与电抗性元件相联结,则可能会产生谐振,使某些频率点的插入损耗变为插入增益。

可见,正确选择滤波器的结构至关重要。究竟是选择电容、电感还是两者的组合,是由所谓的"最大不匹配原则"决定的。简言之,在任何滤波器中,电容两端存在高阻抗,电感两端存在低阻抗。图1是利用最大不匹配原则得到的滤波器的结构与ZS和ZL的配合关系,每种情形给出了2种结构及相应的衰减斜率。

欲了解更多的电路设计方法,来《从零开始学硬件电路设计》。

暂无评论